Изобретение относится к вычислительной технике. Оно может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве, сохраняющем информацию при отключении источника питания, на запоминающих транзисторах c плавающими, управляющими, стирающими затворами.

Целью изобретения является повышение надежности работы матричного накопителя.

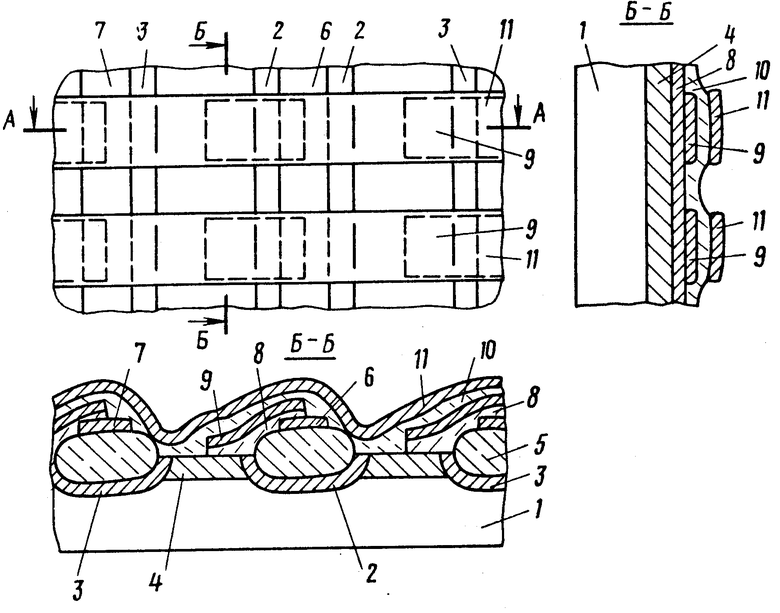

На чертеже приведен вариант матричного накопителя для электрически перепрограммируемого постоянного запоминающего устройства.

Матричный накопитель содержит полупроводниковую подложку 1 первого типа проводимости, в приповерхностном слое которой размещены одни и другие разрядные диффузионные шины 2, 3 второго типа проводимости, между ними диффузионный слой 4 первого типа проводимости.

На поверхности полупроводниковой подложки 1 над разрядными диффузионными шинами 2, 3 расположен первый диэлектрический слой 5, на поверхности которого над одними и другими разрядными диффузионными шинами 2, 3 размещены соответственно одни и другие стирающие поликремниевые шины 6, 7.

На поверхности полупроводниковой подложки 1, первого диэлектрического слоя 5, стирающих поликремниевых шин 6, 7, одних торцах разрядных диффузионных шин 2, 3, слое 4 расположен второй диэлектрический слой 8 меньшей толщины.

На поверхности второго диэлектрического слоя 8 размещены поликремниевые (плавающие) электроды 9 над стирающими поликремниевыми шинами 6, 7 с малой площадью их перекрытия и с перекрытием зазора между разрядными диффузионными шинами 2, 3 на 0,4-0,6 от величины этого зазора.

На поверхности поликремниевых электродов 9, второго диэлектрического слоя 8, слое 4 первого типа проводимости, других торцах разрядных диффузионных шин 2, 3 расположен третий диэлектрический слой 10, на поверхности которого над поликремниевыми электродами 9 и слоем 4 первого типа проводимости размещены адресные поликремниевые шины 11 перпендикулярно разрядным диффузионным шинам 2, 3.

Места переcечения адресных поликремниевых шин 11 и разрядных диффузионных шин 2, 3 представляют собой ячейки памяти в виде последовательно включенных адресного МДП-транзистора и запоминающего транзистора с плавающим, управляющим, стирающим затворами.

Поликремниевые электроды 9 являются плавающими (запоминающими) затворами, адресные поликремниевые шины 11 управляющими затворами, стирающие поликремниевые шины 6, 7 стирающими затворами запоминающих транзисторов, адресные поликремниевые шины 11 затворами адресных МДП-транзисторов, разрядные диффузионные шины 2, 3 стоками (истоками) адресных МДП-транзисторов, истоками (стоками) запоминающих транзисторов.

Сущность работы матричного накопителя заключается в следующем. Для одновременного стирания информации из всех запоминающих транзисторов матричного накопителя на все стирающие поликремниевые шины 6, 7 относительно полупроводниковой подложки 1 подают высокое импульсное положительное напряжение, на адресные поликремниевые шины 11, разрядные диффузионные шины 2, 3 нулевое напряжение.

Под действием этих напряжений во втором диэлектрическом слое 8 между стирающими поликремниевыми шинами 6, 7 и поликремниевыми электродами 9 возникает высокая напряженность электрического поля, под действием которого электроны с нижней поверхности поликремниевых электродов 9 инжектируются в диэлектрический слой 8 и удаляются через стирающие поликремниевые шины 6, 7, в результате чего пороговые напряжения запоминающих транзисторов становятся отрицательными, что эквивалентно единичному, проводящему состоянию в режиме считывания информации.

В режиме постраничного стирания информации в отличие от общего на невыбранные стирающие поликремниевые шины 6, 7 подают нулевое напряжение, а на невыбранные адресные поликремниевые шины 11 низкое положительное импульсное напряжение. Это приводит к уменьшению напряженности электрического поля в диэлектрическом слое 8 между стирающими поликремниевыми шинами 6, 7 и поликремниевыми электродами 9 невыбранных запоминающих транзисторов, в результате чего пороговые напряжения у невыбранных запоминающих транзисторов сохраняются неизменными, а пороговые напряжения у выбранных запоминающих транзисторов принимают отрицательные значения.

В режиме пословарного программирования запоминающих транзисторов на выбранную адресную поликремниевую шину 11 подают высокое положительное импульсное напряжение относительно полупроводниковой подложки 1, на невыбранные адресные поликремниевые шины 11 подают нулевое напряжение.

На выбранные разрядные диффузионные шины 2 (3), расположенные с перекрытием выбранных поликремниевых электродов 9, подают высокое положительное импульсное напряжение, на смежные с ними разрядные шины 3 (2) подают нулевое напряжение, остальные отключают или подают на них через нагрузку низкое положительное напряжение.

При протекании тока через открытые выбранные запоминающие транзисторы и адресные МДП-транзисторы за счет высокой напряженности стокового электрического поля выбранных запоминающих транзисторов "горячие" электроны инжектируются из каналов этих транзисторов, захватываются поликремниевыми электродами 9, что приводит к увеличению их пороговых напряжений. Это эквивалентно нулевому непроводящему состоянию в режиме считывания информации.

Состояния остальных невыбранных запоминающих транзисторов сохраняются неизменными из-за нулевого напряжения на адресных шинах 11 (управляющих затворах) или низкого напряжения на стоках запоминающих транзисторов, в результате чего отсутствует инжекция "горячих" электронов в их каналах.

Для одновременного программирования всех запоминающих транзисторов на все адресные поликремниевые шины 11 подают высокое положительное импульсное напряжение относительно полупроводниковой подложки 1, на все стирающие поликремниевые шины 6, 7, разрядные диффузионные шины 2, 3 нулевое напряжение.

Под действием высокой напряженности электрического поля в диэлектрическом слое 8 между поликремниевыми электродами 9 и стирающими поликремниевыми шинами 6, 7 электроны инжектируются с верхней поверхности стирающих поликремниевых шин 6, 7, туннелируют через диэлектрический слой 8, захватываются поликремниевыми электродами 9, увеличивая пороговые напряжения запоминающих транзисторов, что эквивалентно непроводящему, нулевому состоянию в режиме считывания информации.

В режиме постраничного программирования информации в отличие от общего на невыбранные адресные поликремниевые шины 11 подают нулевое напряжение, на невыбранные стирающие поликремниевые шины 6, 7 низкое, нулевое положительное импульсное напряжение. Это приводит к уменьшению напряженности электрического поля в диэлектрическом слое 8 между стирающими поликремниевыми шинами 6, 7 и поликремниевыми электродами 9 невыбранных запоминающих транзисторов, в результате чего пороговые напряжения у невыбранных запоминающих транзисторов сохраняются неизменными, а у выбранных транзисторов принимают положительные значения.

В режиме считывания информации на адресную поликремниевую шину 11 и разрядную диффузионную шину 2 (3) подают низкое положительное напряжение, на разрядную шину 3 (2), стирающие поликремниевые шины 6, 7, полупроводниковую подложку 1 подают нулевое напряжение. На остальные адресные поликремниевые шины 11 подают нулевое напряжение, на разрядные шины 2 (3) низкое положительное напряжение.

Через выбранные запоминающие транзисторы ток не протекает; протекает если они находятся в нулевом (единичном) состоянии. Через невыбранные запоминающие транзисторы ток не протекает.

Полупроводниковая подложка 1 может быть выполнена из кремния p-типа проводимости с удельным сопротивлением более 7-40 Ом см. Толщина первого диэлектрического слоя из двуокиси кремния составляет 0,5-1 мкм, второго диэлектрического слоя 8 из двуокиси кремния 0,03-0,05 мкм, третьего диэлектрического слоя 10 из двуокиси кремния 0,05-0,08 мкм.

Диффузионный слой 4 выполнен легированием бора с поверхностной концентрацией 1016-5 ˙ 1016 см-3. Разрядные диффузионные шины 2, 3 легированы мышьяком, сопротивление их менее 50 Ом/ расстояние между ними 4 мкм, ширина 3 мкм. Ширина адресных поликремниевых шин 11 и поликремниевых электродов 9 составляет 3 мкм, зазоры между ними 2 мкм, ширина стирающих поликремниевых шин 6, 7 составляет 0,5-2,0 мкм. Площадь ячейки памяти при нормах проектирования 2 мкм составляет 35 мкм2 (при нормах проектирования 1,2 мкм 13 мкм2).

Считывание информации проводят при низком положительном напряжении 5 В, стирание при высоком положительном напряжении 20 В. Словарное программирование запоминающих транзисторов путем инжекции "горячих" электронов из канала при токе 0,5-1 мА проводят от источника питания 13 В, общее, страничное программирование этих транзисторов (с малой потребляемой мощностью) проводят при более высоком положительном импульсном напряжении 25-30 В.

Для матричного накопителя поликремниевые электроды размещены с перекрытием зазора между разрядными диффузионными шинами на 0,4-0,6 от величины зазора. Зазор между разрядными диффузионными шинами (например, равный 4 мкм) равен сумме длин каналов запоминающего транзистора и адресного МДП-транзистора. Вышеуказанное перекрытие эквивалентно длине канала запоминающих транзисторов 1,6-2,4 мкм и длине канала адресного МДП-транзистора 2,4-1,6 мкм соответственно.

С уменьшением длины канала запоминающего транзистора (при нормах проектирования 2 мкм) увеличивается невоспpоизводимость длины канала запоминающего транзистора из-за погрешности совмещения поликремниевых электродов с краями разрядных диффузионных шин. При увеличении длины канала запоминающего транзистора увеличивается невоспроизводимость канала адресного МДП-транзистора. Т. е. размещение поликремниевых электродов с перекрытием 0,4-0,6 от величины зазора между разрядными диффузионными шинами является оптимальным при изготовлении запоминающих и адресных МДП-транзисторов с учетом технологических разбросов их изготовления.

Основным преимуществом предлагаемого матричного накопителя является повышение надежности его работы за счет размещения стирающих поликремниевых шин над всеми разрядными шинами под плавающими поликремниевыми электродами, в результате чего под адресными поликремниевыми шинами, между краем разрядной диффузионной шины с одной стороны и краем плавающего затвора с другой стороны образованы адресные МДП-транзисторы, последовательно включенные с запоминающими транзисторами, что и позволяет проводить стирание информации до отрицательных пороговых напряжений запоминающих транзисторов без изменения работоспособности матричного накопителя, т.е. увеличить разницу пороговых напряжений запоминающих транзисторов в различных состояниях.

Соединение МДП-транзисторов с каждой разрядной шиной позволяет при программировании за счет падения напряжения на открытом адресном МДП-транзисторе при зарядке емкости невыбранной разрядной шины исключить инжекцию "горячих" электронов из канала невыбранного запоминающего транзистора, а именно, исключить изменение порогового напряжения невыбранного запоминающего транзистора, что повышает надежность работы матричного накопителя с большой информационной емкостью.

Изобретение относится к вычислительной технике. Оно может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве, сохраняющем информацию при отключении источника питания, на запоминающих транзисторах с плавающими, управляющими, стирающими затворами. Целью изобретения является повышение надежности работы матричного накопителя. Цель достигается за счет размещения стирающих шин над всеми разрядными шинами под плавающими поликремниевыми электродами. При этом МДП-транзисторы соединены с каждой разрядной шиной, а не с одними разрядными шинами, что позволяет при программировании за счет падения напряжения на открытом адресном МДП транзисторе при заряде емкости невыбранной разрядной шины исключить инжекцию "горючих" электронов из канала невыбранного запоминающего транзистора, а именно исключить изменение порогового напряжения невыбранного запоминающего транзистора. 1 ил.

МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий полупроводниковую подложку первого типа проводимости, в приповерхностном слое которой размещены одни и другие разрядные диффузионные шины второго типа проводимости, в зазорах между которыми расположен диффузионный слой первого типа проводимости, на поверхности разрядных диффузионных шин расположен первый диэлектрический слой, на поверхности которого размещены стирающие поликремниевые шины, одни над одними разрядными диффузионными шинами, на поверхностях первого диэлектрического слоя, диффузионными шинами, на поверхностях первого диэлектрического слоя, диффузионного слоя первого типа проводимости, стирающих поликремниевых шин и одних торцах разрядных диффузионных шин второго типа проводимости расположен второй диэлектрический слой, на поверхности которого размещены поликремниевые электроды с малой площадью перекрытия стирающих поликремниевых шин, на поверхностях которых и второго диэлектрического слоя расположен третий диэлектрический слой, на поверхности которого размещены адресные поликремниевые шины над поликремниевыми электродами перпендикулярно разрядным диффузионным шинам, отличающийся тем, что, с целью повышения надежности работы матричного накопителя, другие стирающие поликремниевые шины размещены над другими разрядными диффузионными шинами, поликремниевые электроды размещены с перекрытием зазора между разрядными диффузионными шинами на 0,4 0,6 от величины зазора, третий диэлектрический слой расположен на поверхности диффузионного слоя первого типа проводимости с перекрытием других торцов разрядных диффузионных шин.

| Авторское свидетельство СССР N 795263, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-12-20—Публикация

1986-01-21—Подача