транзисторы 5 второй группы На выбранную разрядную шину 7 (11) подают низкое положительное напряжение (2 В), остальные разрядные шшш 7 (11) от клгоч ают„

Если напряжение на выбранной адресной шине б превышает (не превышает) пороговое напряжение транзисторов 1 этой строки, то они находятся в открытом (закрытом) состоянии, через них, открытые транзисторы 4 первой группы, разрядные шины 7 (11), шину 9 iryjiesoro потенциала протекает (не протекает) ток, что эквивалентно единичному (нулевому) состоянию,

В одном режиме общего стирания информации на псе адресные шины 6 подают нулевое напряжение, все разрядные шины 7, 11 отключают. На шину 10 третьей группы подают высокое положительное импульсное напряжение (15 В, 1 с), В результате высокое положительное напряжение через открытые транзисторы 5 второй группы пере- даетря на одни обкладки накопительный: конденсаторов 3 и истоки всех тран- зиг.торов 1 6 На управляющие затворы транзисторов I и другие обкладки конденсаторов 3 передается нулевое напряжение с адресных шин 6. Под действием этих напряжений избыточный заряд электронов удаляется с плавающих затворов транзисторов 1 через накопительные конденсаторы 3, в результате чего их пороговое напряжение становится менее 1 В (до -2 В), что эквивалентно единичному состоянию в режиме считывания информации. В другом режиме общего стирания информации на все адресные шины 6 и шины 9, 10 подают нулевое напряжение. На разрядные шины 7, II первой и второй групп подают высокое положительное импульсное напряжение (12 В, 1 с). Под действием этих напряжений избыточный заряд электронов удаляется с плавающих затворов транзисторов I через конденсаторы 3, в результате чего их пороговые напряжения становятся отрицательными, что эквивалентно единичному состоянию в режиме считывания информации.

Следует отметить, что для обеспечения блочного стирания информации р первом режиме через выбранные транзисторы 5 второй группы на выбранные шины 8 подают высокое положительное импульсное напряжение, при

10

15

20

252886

этом остальные транзисторы 5 невЪ1б- , ранных строк находятся в закрытом состояниио Через конденсаторы 3 выбранных строк происходит удаление -иэ- быточного заряда транзисторов 1 выбранных строк, состояния остальных транзисторов сохраняются неизменными

Для обеспечения блочного стирания информации во втором режиме только на выбранные разрядные шины 7, 11 подают высокое положительное импульсное напряжение. В режиме программирования информации на выбранную адресную шину 6 и через нагрузку на разрядную шину 7 (11) подают высокое положительное импульсное напряжение (12 В, 0,1 мс), на остальные адресные тины 6 и разрядные шины 7, 11, .шину 9 нулевого потенциала подают нулевое напряжение, на шину 10-опорное напряжение (3-5 В).

Под действием этих напряжений через выбранные запоминающие транзисто- ры 1 и транзисторы 4 первой группы той же строки протекает ток, вызывая инжекцшо горячих электронов в каналах запоминающих транзисторов 1, захват их плавающими затворами этих транзисторов о Это приводит к положительным пороговым напряжениям запоминающих транзисторов 1 (6-8 В), что эквивалентно нулевому состоянию. Состояния остальных запоминающих транзисторов 1 сохраняются неизменными из-за отсутствия инжекции горячих электронов в их каналах в малого падения напряжения на конденсаторах 2.

Основным преимуществом предложенного матричного накопителя по отношению к прототипу является повышение его работоспособности, обеспечивающего надежную работу при отрицательных пороговых напряжениях запоминающих транзисторов после стирания информации до -3 В,

30

35

40

45

Подключение стоков запоминающих транзисторов столбцов соседних четных и нечетных строк к разным разрядным шинам первой и второй групп позволяет исключить влияние запоминающего транзистора соседней строки с отрицательным порогочым напряжением, так как токи протекают через разные разрядные шины 7, 41.

Подключение истоков запоминающих транзисторов 1 остальных невыбрлн- ных строк через трапзнстгоы 5 иго5

рой группы к шине 10 опорного питания позволяет сместить по истоку эти запоминающие транзисторы (на 2-3 В) при заземленных их управляющих зат- ворах что эквивалентно подаче отрицательного напряжения ((-2)-(-3) В) на управляющие затворы и подложку этих запоминающих транзисторов. В результате чего эти запоминающие трав зисторы находятся в закрытом состоянии при отрицательных пороговых напряжениях (-3)-(-4) В) с учетом обратного смещения по подложке.

16

Формула изобретен ,и я

j

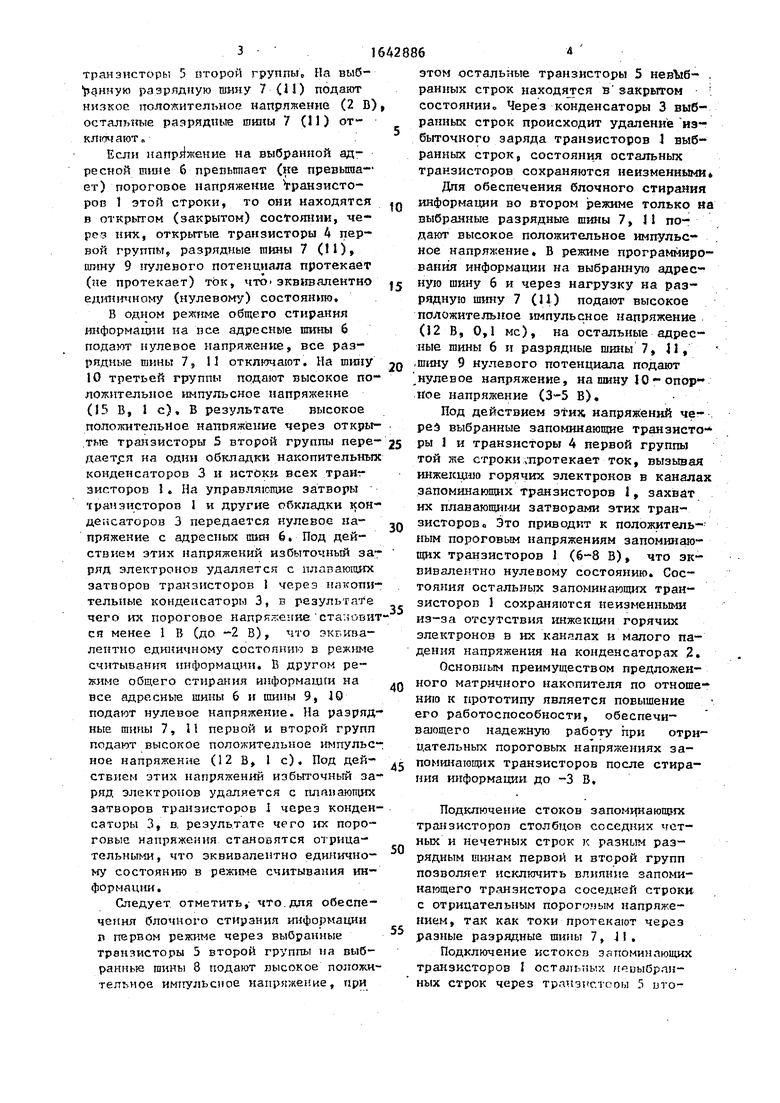

Матричный накопитель для постоянного запоминающего устройства, содержащий ячейки памяти, каждая из Koto- рых состоит из запоминающего транзистора и первого и второго конденсаторов, первые обкладки которых под- ключены к плавающему затвору, а вторые - соответственно к стоку и истоку запоминающего Транзистор., тран-

42886

зисторы выборки первой и второй группt управляющие затворы запоминающих транзисторов каждой строки, псдклю, ценные к соответствующей адресной шине, стоки запоминающих транзисторов столбца нечетных строк, подключенные к разрядной шине первой группы, объе,- динекные стоки запоминающих транзис- 10 -торов столбца четных строк, истоки запоминающих транзисторов смежных строк, подключенные к шине первой группы, истоки транзисторов выборки первой и второй групп, подключенные

15 к шинам второй и третьей групп соответственно, отличающийся тем что, с целью повышения надежности работы матричного накопителя, затворы транзисторов выборки первой

20 группы в строке подключены к адресной шине, стоки транзисторов выборки первой и второй групп в строке подключены к шине первой группы, стоки запоминающих транзисторов смежных строк

25 подключены к- разрядной шине второй группы.

rr

7

1110

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1405575A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ИНФОРМАЦИИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378683A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1025259A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1338688A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

Авторы

Даты

1992-09-23—Публикация

1989-07-18—Подача