-4

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| Многоканальный коммутатор | 1980 |

|

SU938406A1 |

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

| Электронный ключ на мдп транзисторах | 1974 |

|

SU500588A1 |

| @ - @ -Триггер | 1982 |

|

SU1034154A1 |

| Аналоговое множительное устройство | 1979 |

|

SU932506A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Аналоговый ключ | 1982 |

|

SU1026310A1 |

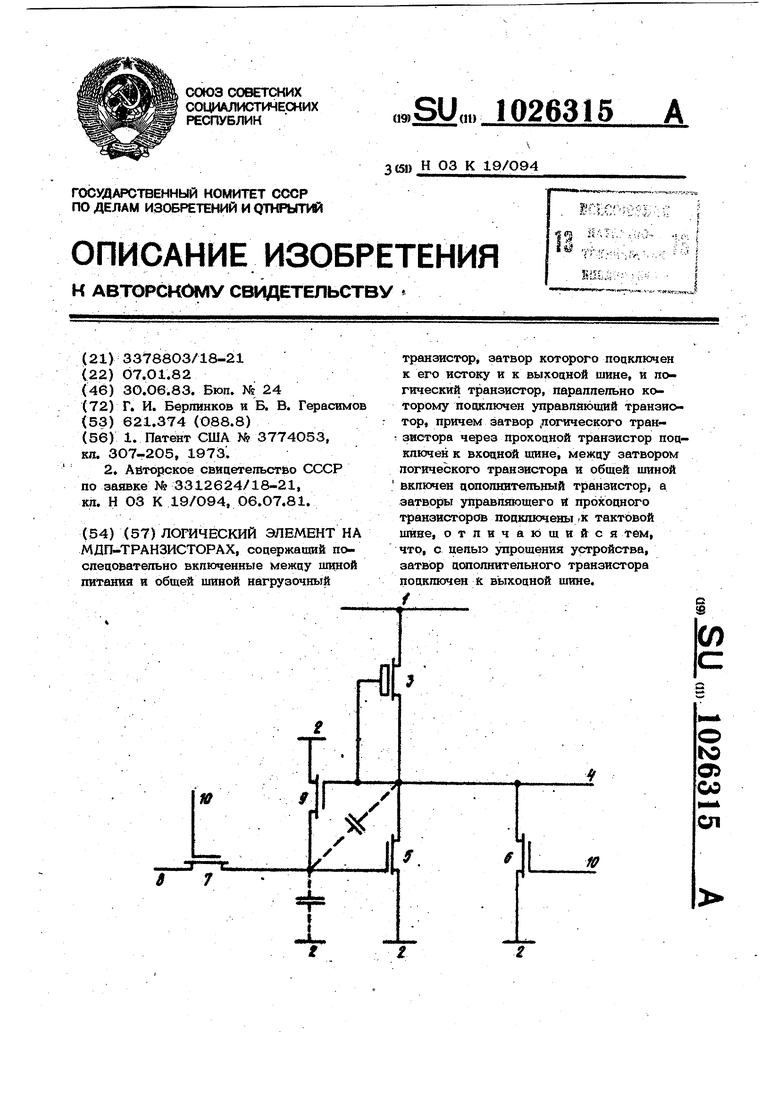

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ, соцержащий посдецоватепьно включенные мевду шиной питания и общей шиной нагрузочный , Ш;1:(,и j |1| --- . I ТГ.Г-.... -1 транзистор, затвор которого поцключен к его истоку и к выхоцной шине, и логический транзистор, параллельно которому подключен управпйюншй транзиотор, причем затвор .логического тран: зистора через проходной транзистор поцключен к входной щине, между затвором логического транзистора и общей шиной включен дополнительный транзистор, а затворы управпйощего и проходного транзисторов подкшочены. к тактовой шине, отличающий ся тем, что, с ценыэ упрощения устройства, затвор дсятолнительного транзистора поцключен к выхоцной шине, f .. .

U б 7 I . Изобретение относился к вьпгаспи тельной технике, в частности может найти применение при разработке цифровых инт1егральных устройствна МДПтранэисторах. Известно логического устройство с зашитой от динамической помехи, содер жащее лагрузочный транзистор, управляющий транзистор, затвор которого поцключен к первой тактовой шине, логический транзистор, затвор которого поцключен. через прохоаной транзистор к вхоцной шине, при этом зат вор прохоцного транзистора поцключен к первой тактовой шине, и четыре транзистсфа помехозашиты, причем первый и вторе транзисторы образуют цинамический инвертор, вхоц которого поцключен к затвору логического транн зистора, а третий и. четвертый npetjставляют собой два последовательно включенных разрядных трешзистрра, сток третьего поцключен к затвору логического транзистора,а затвор - к выходу динамического инвертора, затво четвертого транзистора поцключен к втсфой тактов Я( шине, а исток- к пер вой тактовой ишне Cl 3.. Недостатками известного устройств ва явл5аотся его спожность и малая надежность так как устройство не срабатывает в случае большой помехи, когда неспряжение помехи превышает значение порогового напряжения, и в случае действия асинхронной помехи, цействует в момент времени, когпа на йервой и второй тактовых шинах действует низкий уровень напряжения. Наиболееблизким к предлагаемому является логический элемент на МДПтранзисторах, обладающий большей ноцежностью, содержащий последовательн включенные межоу шиной питания и о щей шиной нагрузочный транзистор затвор которого поцключен к его нсток и к выходной шине, и логический транзистор, параллельно которому подключе управляющий транзистор, прячем затво логического транзистора через проход ной транзистор подключен к входной шине, между затвором логического транзистора и общей шиной включен дополнительный транзистор, затворы управл5п6швго и проходного транзнстор подключены к тактовой шине ц2 j.. Недостатком известного устройства является его сложность. Цель изобретения - упрощение устройства. Указанная цель достигается тем, что в логическом элементе на МДПтранзисторах, содержащем последовательно включенные межцу шиной питания и общей шиной нагрузочный транзистор, затвор которого поцключен к его истоку и к выходной шине, и логический транзистор, параллельно которому поцключен управляющий транзистор, причем затвор логического транзистора через проходной транзистор поцключен к вхосьной шине, межцу затвором логического транзистора и общей шиной включен цополнительный тран зистор, а затворы управл5пошего я прохоцного транзисторов поцключены к тактовой шине, затвор цсотопнительного транзистора поцключен к выходной шине. На чертеже прецставлена электричео кая принципиальная схема устройства. Между шиной 1 питания и обшей ишной 2 после цовательно включены нагрузочный транзистор 3, затвор которого поцклю чен к его истоку и к выходной шине 4, и логический транзистор 5, параллельно которому поцключен управляюодай транзистор 6. Затвор логического тра зистора 5 через прохоцной транзистор 7 поцключен к вхоцной шине 8, межцу затвором транзистора .5 и общей шиной 2 включен дополнительный .транзистор 9,. Затворы транзисторов б и 7 поцключены к тактовой шине 10, затвор транзистора 9 поцключен к выходной шине 4. Устройство работает следующим о разом. При поступлении на вхоцну шину 8 НЕшряжения логического нуля (низкий уровень), а на затворы транзисторов 7 и 6 - напряжения логической единицы (высокий уровень), происходит разряц емкости хранения, образованной емкостью затвора транзистора 5, через открытый прохоцной транзистор 7, в результате чего йа транзистора 5. устанаьлквается низкий уровеяь напряжения. На выходной шине 4 также устанавливается напряжение логического нуля, так как транзистор 6 открыт. После окончания действия тактовых импульсов транзисторы 6 и 7 за1фывак)тся, логический транзЕГСтор 5 также закрыт в выходное напряжение на шине 3 на (шстает до величины напряжения шины 1 питания. При этом через паразитную GMtiocrb затвор-сток логического трани австора 5 и емкость хранения затво|

исток : транаистгора 5 по мере нарвете ния выходного напряжения протекает емкостной ток, в результате на затв« ре логического транэистрра 5 возрастае Уровень напряжения (цинамическая пам& ха), величина которЬго етфецепяется соотношением этих емкостей. Но как только величина выхоцного напряжения достигнет значения порогового, открывается пополнительный транзистор 9, и заряц, обусловленный оинамической помехой, через от1фытый транзистор 9 стекает йа общую шину 2. .

Ввиау того, что величина напряжения помехи на затворе логическсяо транзистора 5 определяется емкостным целителем, то величина напряжения на затворе пополнительного транзистора 9 всегпа достигнет порогового иапряжения раньше, чем величина напряжение на затворе логического транзистора 5 достигает величины порогового нагфямения, тем самым исключается случай большой помехи. Кроме того, дополнительный транзистор 9 открывается после оксжчания аействия тактовых импульсов И| образуя ЦЕПЬ стекания заряда с емкости хранеШ1я (емкость затв : -исток транзистора 5) на общую шину 2 независимо от времени появления помехи, 0беса1ечивает защиту уст ройства от асинхронной помехи.

Логический элемент содержит всего пять транзист ч)ов и одну тактовую шину, что обеспечивает упрощение устройства и позволяет повысупъ надежность я уменьшить занимаемую им площадь на кристалле.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США N 3774053, кп | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Айторекое свицетепьст&о СССР по заявке N 3312624/18-21, кп | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-30—Публикация

1982-01-07—Подача