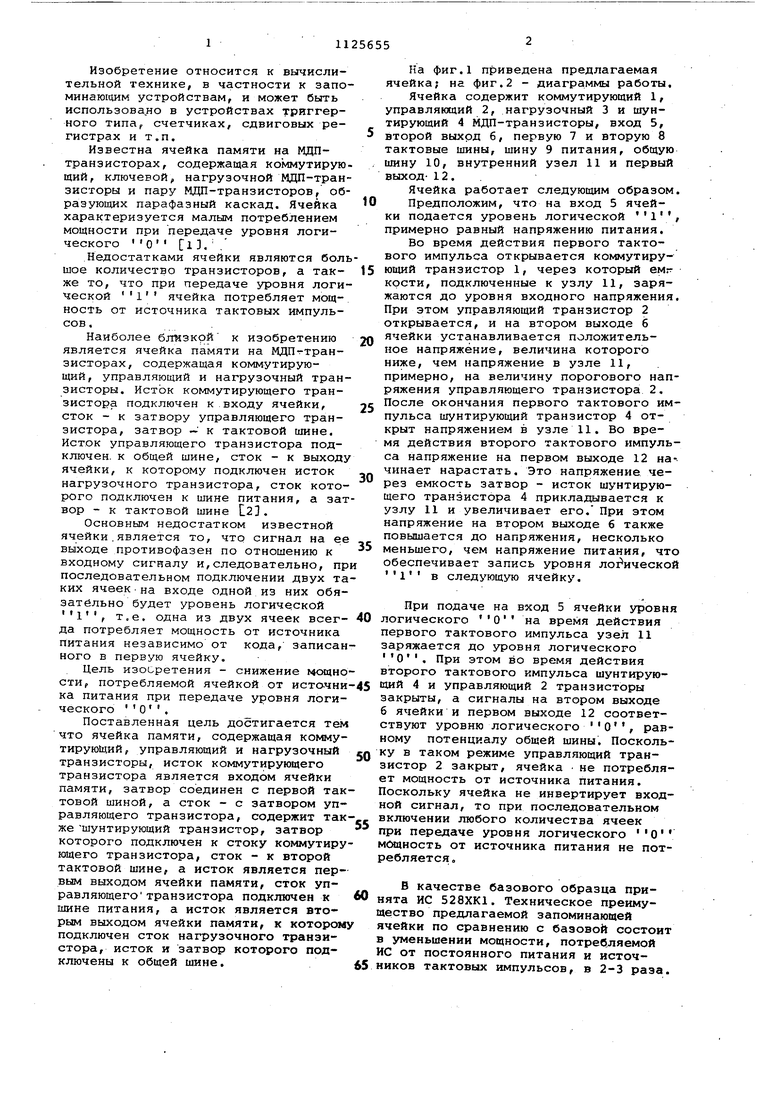

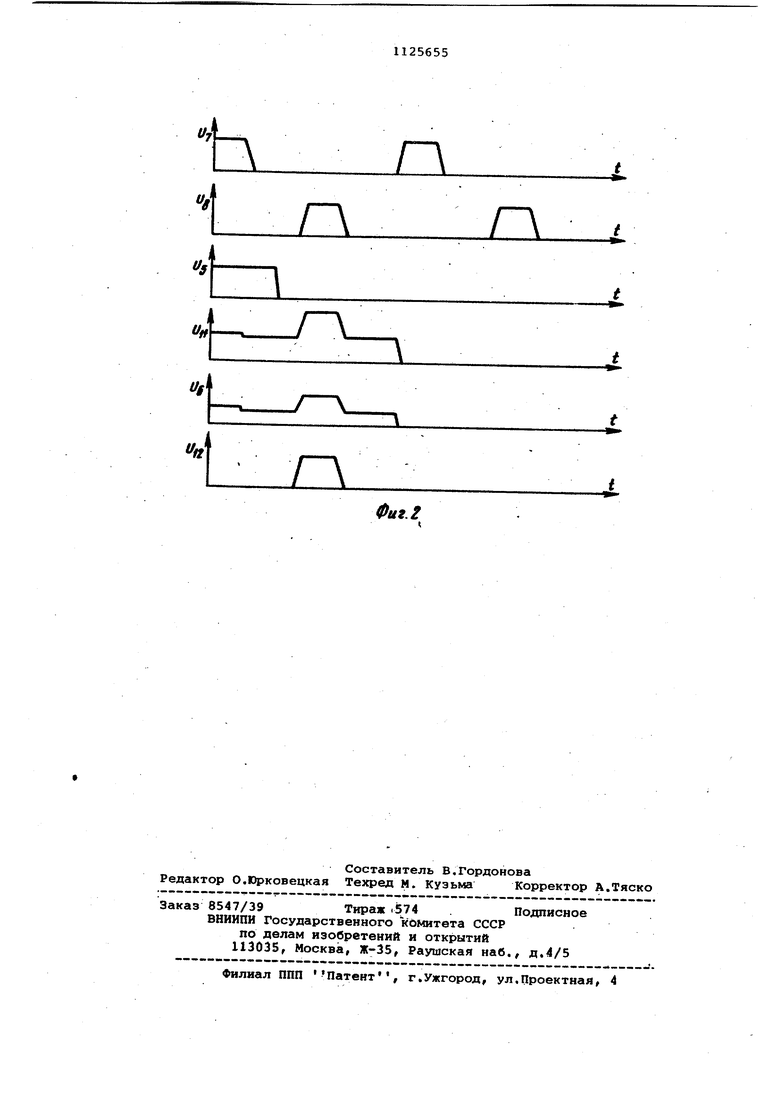

мг. f Изобретение относится к вычислительной технике, в частности к запо минаю1цим устройствам, и может быть использова.но в устройствах триггерного типа, счетчиках, сдвиговых регистрах и т.п. Известна ячейка памяти на МДПтранзисторах, содержащая коммутирую щий, ключевой, нагрузочной МДП-тран зисторы и пару МДП-транзисторов, об разующих парафазный каскад. Ячейка характеризуется малым потреблением мощности при передаче уровня логического О 1 . . Недостатками ячейки являются бол шое количество транзисторов, а также то, что при передаче уровня логи ческой 1 ячейка потребляет мощность от источника тактовых импульсов , Наиболее бл«зкрй к изобретению является ячейка памяти на МДПттранзисторах, содержащая коммутирующий, управляющий и нагрузочный тран зисторы. Исток коммутирующего транзистора подключен к входу ячейки, сток - к затвору управляющего транзистора, затвор к тактовой шине. Исток управляющего транзистора подключен, к общей шине, сток - к выход ячейки, к которому подключен исток нагрузочного транзистора, сток которого подключен к шине питания, а зат вор - к тактовой шине L23. Основным недостатком известной ячейки .является то, что сигнал на eie выходе противофазен по отношению к входному сигналу и,следовательно, пр последовательном подключении двух та ких ячеек.на входе одной из них обязательно будет уровень логической , т.е. одна из двух ячеек всегда потребляет мощность от источника питания независимо от кода, записан ного в первую ячейку. Цель изосретения - снижение 4oщнo сти, потребляемой ячейкой от исто-чни ка питания при передаче уровня логического О . Поставленная цель достигается тем что ячейка памяти, содержащая коммутирующий, управляющий и нагрузочный транзисторы, исток коммутирующего транзистора является входом ячейки памяти, затвор соединен с первой так товой шиной, а сток - с затвором управляющего транзистора, содержит так же шунтирующий транзистор, затвор которого подключен к стоку коммутиру ющего транзистора, сток - к второй тактовой шине, а исток является первым выходом ячейки памяти, сток управляющего транзистора подключен к шине питания, а исток является вторым выходом ячейки памяти, к котором подключен сток нагрузочного транзистора, исток и затвор которого подключены к общей шине. На фиг.1 приведена предлагаемая ячейка; на фиг.2 - диаграммы работы. Ячейка содержит коммутирующий 1, управляющий 2, нагрузочный 3 и шунтирующий 4 МДП-транзисторы, вход 5, второй выход 6, первую 7 и вторую 8 тактовые шины, шину 9 питания, общую шину 10, внутренний узел 11 и первый выход- 12. Ячейка работает следующим образом. Предположим, что на вход 5 ячейки подается уровень логической 1, примерно равный напряжению питания. Во время действия первого тактового импульса открывается коммутирующий транзистор 1, через который емг кости, подключенные к узлу 11, заряжаются до уровня входного напряжения. При этом управляющий транзистор 2 открывается, и на втором выходе б ячейки устанавливается положительное напряжение, величина которого ниже, чем напряжение в узле 11, примерно, на величину порогового напряжения управляющего транзистора 2. После окончания первого тактового импульса шунтирующий транзистор 4 открыт напряжением в узле 11. Во время действия второго тактового импульса напряжение на первом выходе 12 начинает нарастать. Это напряжение через емкость затвор - исток шунтирующего транзистора 4 прикладывается к узлу 11 и увеличивает его. При этом напряжение на втором выходе 6 также повышается до напряжения, несколько меньшего, чем напряжение питания, что обеспечивает запись уровня лог ической в следующую ячейку. При подаче на вход 5 ячейки уровня логического О на время действия первого тактового импульса узел 11 заряжается до уровня логического О . При этом во время действия второго тактового импульса шунтирующий 4 и управляющий 2 транзисторы закрыты, а сигналы на втором выходе б ячейки и первом выходе 12 соответствуют уровню логического О, равному потенциалу общей шины. Поскольку в таком режиме управляющий транзистор 2 закрыт, ячейка не потребляет мощность от источника питания. Поскольку ячейка не инвертирует входной сигнал, то при последовательном включении любого количества ячеек при передаче уровня логического О м Л1ность от источника питания не потребляется. В качестве базового образца принята НС 528ХК1. Техническое преимущество предлагаемой запоминающей ячейки по сравнению с базовой состоит в уменьшении мощности, потребляемой ИС от постоянного питания и источников тактовых импульсов, в 2-3 раза.

ъ

и.

Г

r

Г

%

гл

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Ячейка памяти для регистра сдвига | 1975 |

|

SU570108A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

ЯЧЕЙКА ПАМЯТИ ДЛЯ РЕГИСТРА СДВИГА, содержащая коммутирующий, управляющий и нагрузочный транзисторы, исток коммутирующего транзистора .является входом ячейки памяти, затвор соединен с первой тактовой шиной, а сток - с затвором управляющего транзистора, отличающая ся тем, что, с целью уменьшения потребляемой мощности ячейки памяти от постоянного источника питания при передаче уровня логического О, она содержит шунтирующий транзистор, затвор которого подключен к стоку коммутирующего транзистора, сток - к второй тактовой шине, а исток является первым выходом ячейки памяти, сток управ.ляющего транзистора подключен к шине питания, а исток является вторым выходом ячейки памяти, к которому подключен сток нагрузочного транзистора, исток и затвор которого под-§ ключены к общей шине. ю 1СЛ Од СП сд

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| М., Мир, 1975 с.299 (прототип) . | |||

Авторы

Даты

1984-11-23—Публикация

1983-01-18—Подача