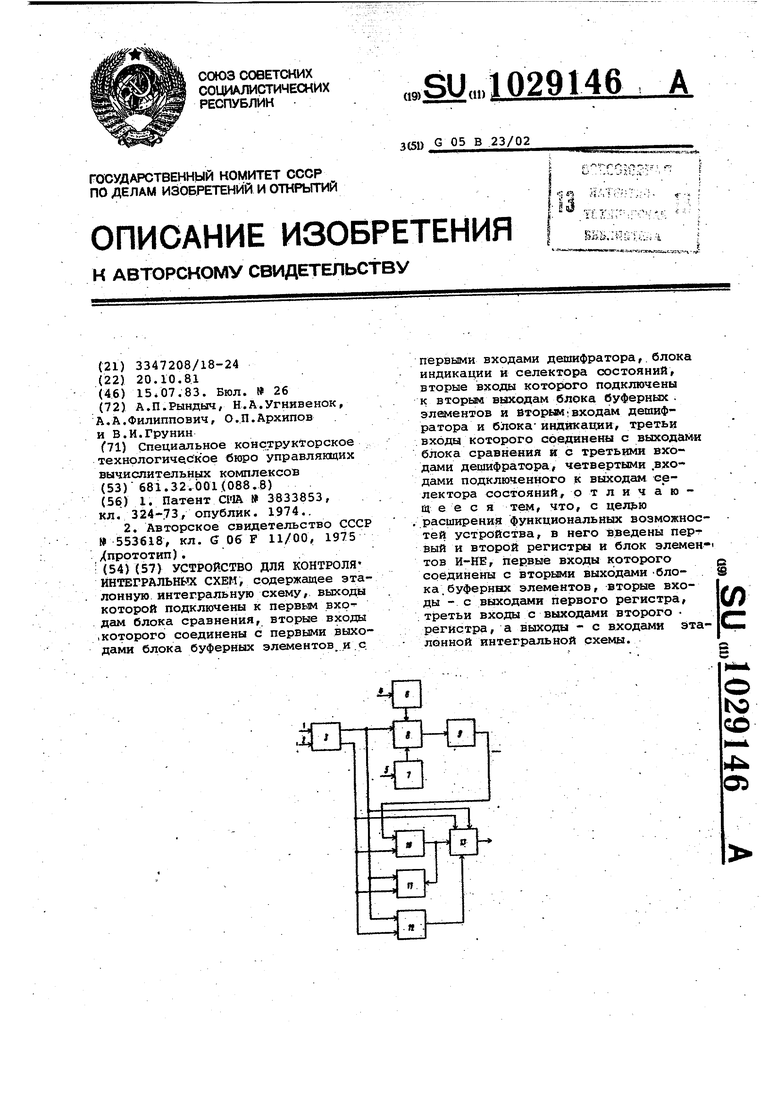

Изобрет.ение относится к вычислительной технике, в. частности к средствам контроля цифровых модулей и может быть использовано для целей функциональной проверки и диаг(ностики неисправностей средств вычислительной техники и автоматики в процессе их производства и тех ческого обслуживания. Известно устройство для контроля интегральных схем, содержащее этало ную интегральную схему, входы котор подключены к выходам буферных элеме тов, блок сравн-ения, соединенный с выходами буферных элементов и эталонной интегральной схемы, блок инд кадии, соединенный входами с выхода ми буферных элементов . и блока -сравн ния 1 . . Недостатком этого устройства является отсутствие возможности останова выдачи текста на.том набор в;;котором обнаружено несравнение сигналов обеих схем или останова при возникновении ожидаемой комбина .ции сигналов на выводах контролируе 1,мой схемы. , . Наиболее близким к изобретению является устройство для контроля ин тегральных схем,содержащее эталонну интегральную схему,выходы которой подключены к первым входам блока о сравнения,вторые..входы которой соед нены с первыми выходами буферных эл ментов и .первыми входами дешифратор блока индикации и селектора состояний вторые входы селектора состо ний соединены с вторыми выходами буферных элементов, вторыми входал и блока индикации и вторыми входами дешифратора, третьи входы которого соединены -с выходами блока сравнечк ния и третьими входами блока индикации, четвертый вход дешифратора соединен с выходом селектора состоя ний, выход дешифратора соединен.с выходом устройства, первые входы которого соединены с входами буферных элементов 2., Недостатком известного устройства являются.; ограниченные функциональные возможности. В устройствах цифровой вычислительной техники часто встречаетяя применение последовательностных интегральных микросхем таким образом, что выводы начальной установки этих микросхем, не используются или в схеме устройства используются микросхемы, у которых эти входы вообще ртсутствуют. При проверке блоков этих; устройств после выдачи питания на проверяемую и эталонную интегральные микросхемы они )ir установить ся в различные состояния. Вследстви этого исключается возможность проверки блоков с помощью устройств, использукяних принцип сравнени-я выходных сигналов микросхем без предвариг тельной установки этих микросхем в идентичные состояния. Однако в известном устройстве контроля отсутствует возможность такой установки, К недостаткам устройства следует отнести также низкую производительно ность при анализе качества и полнотытеста путем наблюдения состояния выводов контролируемой и эталонной микросхем, проводимое после останова вьщачи теста на каждом наборе, т.е. в шаговом режиме. В условиях промышенного производства средств цифровой вычислительной техники при разработке контрольных тестов для проверки цифровых блоков широкой и чистоизменякщейся номенклатуры этот фактор может быть решающим при выборе контрольного оборудования для анализа тестов. Предлагаемое устройство в значительной мере :устраняет недостатки известных устройств Целью изобретения является расширение функциональных возможностей устройства. Поставленная цель достигается тем, что в устройство для контроля интегральных схем, содержащее эталонную интегральную схему, выходы которой подключены к первым входам блока сравнения, вторые входы которого соединены с первыми выходами блока буферных элементов и первыми входами дешифратора, блока индикации и селектора состояний, BTOpbie входы котррого подключены к вторым выходам блока буферных элементов и,к вторым входам дешифратора и блока индикации, третьи входы которого соединены с выходами блока сравнения и с третьими входами дешифратора, четвертыми входами подключенного к выходам селектора состояний, введены первый и второй регистры и блок элементов И-НЕ, первые входы которого соединены с вторыми выходами блока буферных элементов , вторые входы.- с выходами первого регистра, третьи входы - с выходами второго регистра, а выходы с .входами.эталонной интегральной схемы. . . - . На чертеже представлена блоксхема предлагаемого устройства.. Устройство .содержит связанный с входами-1 и- 2 устройства блок. буферных элементов 3,.входы 4 и 5 устройства, связанные с вторым регистром 7, блок 8 элементов И-НЕ эталонную интегральную.схему 9, блок 10 сравнения, блок 11 индикаЦ.ИИ, селектор 12 состояний, дешифратор 13. Устройство работает следующим образом. Входы Г и 2 устройства подключаются к выводам выбранной интегральной схемы цифрового блока и к /входам этого блока прикладывается тест, вырабатываемый некоторым внешним устройством задания тестов. Сигналы, возникающие на входах контролируемой интегральной схемы в каждом такте теста поступают на входы 1 устройства и через элементы блока 3 на входы блока 8. В зависимости от состояния разрядов регистра 6 блок 8 коммутирует на вход эталонной интегральной схемы 9 сигналы с соответствующих этим разрядам выходов блока 3 или выходов регистра 7. Выходные сигналы контролируемой интегральной схемы через входы 2 устройства и блока 3 передаются в блок сравнения 10, который производит срав-. нение этих сигналов с выходными сигналами эталонной интегральной схемы 9 и вудает сигнал о результатах сравнения на один из входов дешифратора 13. С выходов блока 3 сигналы поступают также на входы селектора 12, который производит сопоставление их значений с значениями, установл ными в нем предварительно, и при со падении выдает сигнал на вход деши ратора 13. Кроме этого сигнала и сигнала блока 10 сравнения в дешиф . тор 13 поступают также сигналы с в дов блока 3, отражающие результат проверки сигналов контролируемой интегральной схемы на отклонение от допустимых значений потенциалов О. Дешифратор 13 анали зирует в каждом такте теста значеп ния всех указанных сигналов и при наличии условий вырабатывает сигна останова вьщачи теста. Условиями останова могут быть о клонение сигналов на выводах контро лируемой интегральной схемы .за пределы областей потенциалов и О, несовпадение логических значений выходных сигналов контролируемой и эталонной интегральных схем, совпадение логических значени сигналов; на выводах контролируемой интегральной микросхемы с значениями, предварительно заданными в селе торе 12. При каждом из указанных условий блок; 11 обеспечивает индикацию логических.значений сигналов выводов контролируемой интегральной схемы, результатов сравнения ее выходов и выходов.эталонной схемы, результатов .допускового контроля, ; При контроле с помощью предлагае мого устройства цифровых блоков с последовательностными интегральными микросхемами и при отсутствии у этих микросхем входов начальной ,установки или применении микросхем без использования входов начальной установки устройство осуществляет останов выдачи теста rto завершению начальной установки проверяемой микросхемы. Останов происходит при сравнении логических значений сигналов на выводах этой микросхемы со значениями, записанными в селектор 12. Затем с входа 4 устройства в регистр 61 заносится информация, определяющая прохождение информации от регистра 7 на те вы- воды эталонной схемы, воздействуя на которые определенным тестом можно привести эталонную схему в состояние, идентичное проверяемой. Занесение этого теста в регистр 7 осуществляется через вход 5 устройства. Достижение идентичного состояния эталонной и проверяемой схем фиксируется блоком 10 и регистр рируется блоком 11, после чего осуществляется запись информации с входа 4 устройства в регистр 6 для осуществления коммутации выходов буферных элементов блока 3 через блок S на входы эталонной схемы 9. Затем начинается выдача теста с набора, на котором осуществлен останов. При проверке качества теста дом моделирования неисправностей в регистр 6 производится запись инфор-. мации, коммути.рующейчерез блок 8 на исследуемый вывод {или выводы) эталонной интегральной схемы 9соответствующий ей выход (или выходы) регистра 7. Затем в этот разряд (или разряды) регистра 7 заносится в зависимости от моделируемой неисправности постоянная или О . Если тест позволяет обнаруживать смоделированную неисправность то блок 10 фиксирует несравнение реакций эталонной микросхемы9 и проверяемой, о чем выдает информацию в блок 11 и сигнал останова в дешифратор. Если при моделировании неисправно ности несравнение не наступает, этот факт говорит об отсутствии полноты теста. Тест считается некачественным и тоебукшим доработки. В тех случаях когда при включении питания микросхемы установились в различные состояния, введение регистра 7 -, регистра 6 и блока 8 позволяет установить эталонную схему 9 путем выдачи на нее определенного теста в состояние, идентичное проверяе-. мой, и тем самым исключить случаи ложной браковки интегральных микросхем при контроле цифровых объектов. При проверке качества теста вв.едение перечисленных признаков в устройство позволяет повысить произво- .

51029146

дител1 ность проверки путеммодели- Расвшрение класса контролируерования одиночных и груповых неисп« мых объектов и повышение производиравностей по выводам эталонной тельности при проверке качества мйкр осхемы, .при этом проверка тес- теста устройством с применением

та производится в автоматическом. изобретения позволяет получить

режиме.- значительный экономический эффект.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для контроля интегральных схем | 1975 |

|

SU553618A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1367015A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ, содержащее эталонную интегральную схему, выходы которой подключены к первым вхрдам блока сравнения, вторые входы .которого соединены с первыми выходами блока буферных элементов и .с. первыми входами дешифратора, блока индикации и селектора состояний, вторые входы которого подключены к вторым выходам блока буферных . элементов и вторым; входам дешифратора и блока- инд|1кации, третьи входы которого соединены с выходами блока сравнения и с третьими входами депшфратора, четвертыми .входами подключенного к вьЬсодам селектора состояний, отличающ е е с я тем, что, с целью .расширения функциональных возможностей устройства, в него введены и второй регистры и блок элемен тов И-НЕ, первые входы которого соединены с вторыми выходами блока, буферннх элементов, вторые вхо(Л ды - с выходами первого регистра :третьи входы с выходами второго с регистра, а выходы - с входами эталонной интегральной схемы. to :о о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент CllA 3833853, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля интегральных схем | 1975 |

|

SU553618A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-07-15—Публикация

1981-10-20—Подача