гйстра, инверсные выходы триггеров которого-соединены соответственно с первыми входами элейентов ИЛИ, вто рые входа 1 которых подключены соответственно к инверсным выходам триггеров первого регистра, а выходы элементов ИЛИ и инверсные выходы триггеров первого и второго регистров являются выходами анализатора неизменных значений О или 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля неисправностей интегральных схем | 1974 |

|

SU528517A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| Устройство для контроля цифровых модулей и проверки качества тестов | 1974 |

|

SU519713A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля интегральных схем | 1981 |

|

SU1029146A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для автоматического контроля цифровых объектов | 1977 |

|

SU656063A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

1. УСТРОЙСТВО ДЙЯ КОНТРОЛЯ НЕИСПРАВНОСТЕЙ ИНТЕГРАЛЬНЫХ СХЕМ, содержащее блок контактирования, первая rpyftna входов которого соедннеиа с группой информационных входов устрой.стйа, вторая группа входов с выходами блока выходных вентилей и первой группой входов блока сравнения, а выходы -;с входами блоков дискриминаторов потенциалов и блока развязывающих усилителей,. выходы которого подкшочёны. к первой груйпе входов блока входных вентилей, вт) рая rpynfia входов которого совдин Ёна с первой группой входов блока выхед ных веятилей и выходами дешифратора а вЫхрды - с эталонной схема причём выходы эталонной соединены с второй группой входов блока выходных вентилей, блок регистрации, выход которого являетсх въйсо дом устройства, первьШ вход соедняём . с первьгм управляющим входом устройства, первая группа входов - с выходами блока сравнения, вторая группа входов - с первой группой выходов блока дискриминаторов потенциалов, а третья группа входов - с входами дешифратора и выходами счетчика, вход которого является вторым управляющим входом устройства, вторая группа входов, блоке сравнения соединена с BfoifoH группой выходов блока дискри-, минаторов потенциалов, отличающ е ее я тем, что, с целью расширения класса обнаруживаемых неисправностей и сокращения времени проверки качества теста, в йего введен анализатор-неизменных значений 1 или О, управляющий вход которого (Л соедине;н с дополнительным управляющим входом устройства, информационные входы соединены с выходами блока раэвязывамяцих усилителей, а выходы S е с дополнительной группой входов блока регистрации О 36 2. Устрбйство по п. 1 от л и:«э :о ч а ю щ е е с я тем, что анализатор неизменных значений О или 1 содержит первый и второй регистры и эле- i менты ИЛИ н НЕ, причем вход установза ки в нулевое состояние триггеров первого и второго регистров соединен с дополнительным управляющим входом анализатора нейдмептлх значений О или 1, вхо|$ы установки в единичное состояние триггеров первого регистра соединены соответственно с . информационныйи входами анализатора неизменных значений 0 или 1 а через элементы НЕ - с входами установки в единичное состояние триггеров второго ре-:

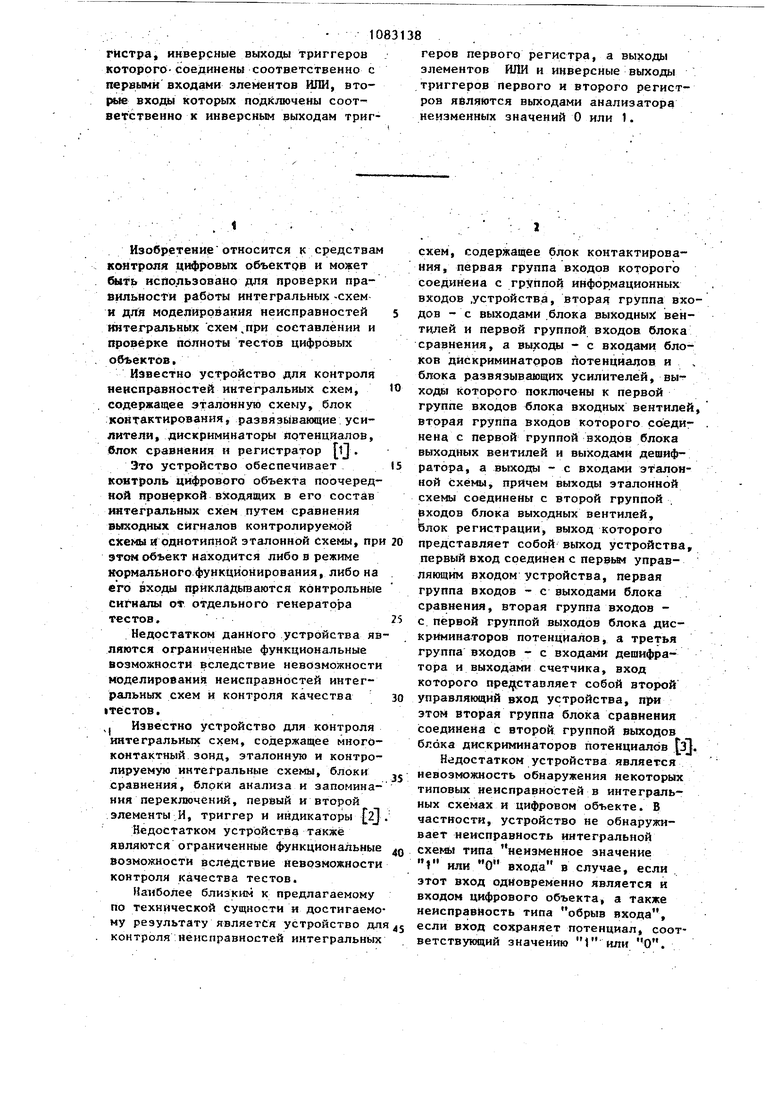

- ..-. Изобретение относится к средствам контроля цифровых объектов и может Сыть использовано для проверки правильносГй работы интегральных -схем и для моделирования неисправностей интегральных схем,при составлении и проверке полноты тестов цифровых объектов. Известно устройство для контроля неисправностей интегральных схем, содержащее эталонную схему, блок контактирования, развязывающие усилители, дискриминаторы потенциалов, блок сравнения и регистратор lj. Это устройство обеспечивает контроль цифрового объекта поочередной проверкой входящих в его состав интегральных схем путем сравнения выходных сигналов контролируемой скемы и однотипной эталонной схемы, пр этом объект находится либо в режиме нормального функционирования, либо на его Bxoffid прйкладьгеаются контрольные сигналы о отдельного генератора тестов, Недостатком данного устройства яв ляются ограниченные функциональные ВОЗМОЖНОСТИ вследствие невозможности моделирования неисправностей интегральных схем и контроля качества тестов. ,. Известно устройство для контроля интегральных схем, содержащее многоконтактный зонд, эталонную и контролируемую интегральные схемы, блоки сравнения, блоКй анализа и запоминания переключений, первый и второй элементы И, триггер и индикаторы 2J Недостатком устройства также являются ограниченные функциональные возможности вследствие невозможности контроля качества тестов. Наиболее близким к предлагаемому по технической сущности и достигаемо му результату является устройство дл контроля неисправностей интегральны схем, содержащее блок контактирования, первая группа входов которого соединена с группой информационных входов .устройства, вторая группа входов - с выходами .блока выходных вентилей и первой группой входов блока сравнения, а выходы - с входами блоков дискриминаторов потенциалов и блока развязывающих усилителей, выходы Которого поключены к первой группе входов блока входных вентилей, вторая группа входов которого соединена с первой группой входов блока выходных вентилей и выходами дешифратора, а выходы - с входами эталонной схемы, причем выходы эталоиной схе№ соединены с второй группой . входов блока выходных вентилей, блок регистрации, выход которого представляет собой выход устройства, первый вход соединен с первьм управляющим входом устройства, первая группа входов - с выходами блока сравнения, вторая группа входов с первой группой выходов блока дискриминаторов потенциалов, а третья группа входов - с входами дешифратора и выходами счетчика, вход которого пре;1)1ставляет собой второй управляющий вход устройства, при этом вторая группа блока сравнения соединена с второй группой выходов блока дискриминаторов потенциалов . Недостатком устройства является невозможность обнаружения некоторых типовых неисправностей в интегральных схемах и цифровом объекте. В частности, устройство не обнаруживает неисправность интегральной типа неизменное значение 1 или О входа в случае, если этот вход одновременно является и входом цифрового объекта, а также неисправность типа обрыв входа, если вход сохраняет потенциал, соответствующий значению 1 или О. 310 Недостатком устройства является также значительное время, затрачиваемое при проверке качества теста. Цель изябретения - расширение класса обнаруживаемых неисправносте и сокращение времени проверки качест ва теста. Указанная цель достигается тем, что в устройство для контроля неисправностей интегральных схем, содержащеё блок контактирования, первая группа входов которого соединена с группой информационных входов устрой ства, вторая группа входов - с выходами блока выходных вентилей и первой группой входов блока сравнения, а выходы - с входами блоков дискрими наторов потенциалов и блока развязывающих усилителей, выходы которого подключены к первой группе входов блока входных вентилей, вторая группа входов которого соединена с первой группой входов блока выходных вентилей ивыходами дешифратора, , а выходы - с входами эталонной схемы причем выходы эталонной схемы соединены с второй группой входов блока выходных вентилей, блок регистрации, выход которого является выходом устройства, первый вход соединен с первым; управляющим входом устройства первая группа входов - с выходами блока сравнения, вторая группа входов - с первой группой выходов блсгка дискриминаторов потенциалов, а треть группа входов - с входами дешифратора и выходами счетчика, вход которог является вторым управляющим-входом устройства, вторая группа входов бло ка сравнения соединена с второй груп при выходов блока дискриминаторов потенциалов, введен- анализатор неизменных значений 1 и О, управляющий вход которого соединен с дополнитепь ным управляющим входом устройства, информацнонныё входы соединены с выходами блока развязывающих усилителей., а выходы - с дополнительной группой входов блока регистрации. I .. При этом анализатор неизменных значений О или 1 содержит первый и втгорой регистры и элементы ИЛИ И НЕ, пр чем вход установки в нулевое состоя- ийе триггеров первого И второго рвгистров соединен с дополнительным управляющим входом анализатора менных. значений О или 1, вхОды устаиовки в единичное состояние 84 триггеров первого регистра соединены соответственно с информационными входами анализатора неизменных значений О и 1, а через элементы НЕ с входами установки в единичное cocfтояние триггеров второго регистра, инверсные выходы триггеров которого соединены соответственно с первыми входами элементов ИЛИ, вторые входы которых подключены соответственно к инверсным выходам триггеров первого регистра, а выходы элементов ИЛИ и инверсные входы триггеров первого и второго регистров являются выходами анализатора неизменных значений О или 1 . На фиг. 1 представлена структурная схема предлагаемого устройстваJ на фиг. 2 - функциональная схема анализатора неизменных значений О или 1. Устройство содержит блок 1 контактирования, блок 2 развязывающих усилителей, блок 3 дискриминаторов потенциалов, блок 4 входных вентилей, эталонную схему 5, блок 6 выходных вентилей, блок 7 сравнения, счетчик 8, дешифратор 9, блок 10 регистрации, анализатор 11 неизменных значений О Ш1И 1, информационные входы t2 устройства, соответственно первый, второй и дополнительный управляющие вХоды 13, 14 и 15 устройства И выход 16 устройства. С помощью первой rpynifti входов блока 1 контактирования информационные входы 12 устройства подключаются к выводам интегральных схем объекта контроля или соединяются с монтажом объекта контроля в тех случаях, когда оно включается вместо какой либо интегральной схемы. Блок 1 контактирования связан, с входами блока 2 развязывающих усилителей и блока 3 дискриминаторов потенциалов. Эти блоки служат для Снижения нагрузки на цепи объектов, к которым подключается устройство, а блок 3 дискриминаторов потенциалов, кроме того, обеспечивает распознавание отклонения логических значений 1 И О на входах и.выходах контролируемой интегральной схемы. Выходы блока 2 развязьгаающик усилителей соединены с первой группой входов блока 4 .входных вентилей, предназначенного для имитации неисправностей вхойов интегральных схен. Выходы; блока 4 входHBIX вентилей. связаны с входами эталонной схемы 5 выходы которой подключены к второй группе входов блока 6 выходных вентилей, предназначенного для да«нтации неисправностей выходов интегральных схем. Выхода блока 6 выходных вентилей подключены к втйрой группе входов блока 1 контактирования и к первой группе входов блока 7 сравнения, к второй группе входов которого подключена вторая группа выходов блока 3 дискриминаторов потенциалов. Блок t сравнения предназначен для сравнения значений сигналов с выходов контролируемой интегральной схемы со знаЧениями сигналов с 0ЫХОДОВ эталонной схемы 5. Счетчик 8, вход которого соединен с вторым управляющим входом Н устройства а . выход - с третьей группой входов : блока 10 регистрации и выходами дешифратора .9, предназначен для обраэования и запоминания кода (номера) имитируемой неисправности. Управление счетчиком 8 осуществляется либо с помощью органов ручного управления, либо по сигналам от а:ппаратуры, совместно с котороЦ используется устройство. Анализатор 11 неизменных значений О или t состоит из триггеров 17 первого регистра, триггеров 18 второго регистра, элементов НЕ 19 и элементов ИЛИ 20 и предназначен для обнаружения на входах или выходах интегральных схем сигналов, логические значения 1 или О которых не иэмейялись за время испытания. Управлякяций вход 21 анализатора 11 связан с дополнительным управляющий входом 15 устройства, информационные входь 22.- с выходами блока 2 развязьшающих усилителей, а выходы 23 - с дополнительной группой входов блока 10 регистрации. Первый вход блока 10 регистрации соединен с первым управляющим входом 13 устройства, певая группа входов - с выходами блока 7 сравнения, вторая группа входов с первой группой выходов блока 3 дискриминаторов потенциалов, третья группа входов - с выходами счетчика 8

Блок 10 регистрации предназначен для индикации результатов сравнения выходных сигналов контролируемой интегральной схемы и эталонной cxeMd 5, результатов контроля значений сигналов 1 и Опо напряжению, результатов анализа неизменных значений 1 или О на В5{одах и выходах интегральной cxefat, а также номера

имитируемой неисправности. Блок 10 регистрации управляется от органов ручного управления и при необходимости с его выходов также формируют сигналы на выход 16 устройства для управления внешней аппаратурой. Для обеспечения контроля и моделировани не исп:равностей различных типов интегральных схем эталонная схема 5 должна быть сменной. В п ростейшем случае она мржет устанавливаться на плате, имеющей необходимые соединительные элементы для ее подключения к устройству. В качестве эталонной cxetJb 5 может использоваться иктег-: ральная схема того же типа, что и контролируемая...

.Устройство работает следующим .образом. :..;

При контроле какого-либо объекта блок. 1 контактирования подключается к выводам выбранной для контроля интегральной схемы. В устройство устанавливается эт алрнная схема 5, тип которой соответствует контролиг , при этом ее входы подключаются к соответствующим выходам блока 4 входных вентилей, а выходы - к соответствующим входам блока 6 выходных вентилей. Счетчик устанавливается сигналом с второго управля мцего входа 14 устройства в исходное состояние, при котором неисправности не имитируются. После этого к контролируемому объекту прикладывается тест, .при этом в первом такте теста на дополнительньйуправляющий вход 1 устройства от внешних органов управления подается импульсный сигнал для установки в нулевое состояние триггеров 17 и 18 первого и второго регистров анализатора 11 неизменных значений О или 1, Сигналь, возникающие в процессе выполнейия теста -на входах и въгходах проверяемой интегральной схемы,.поступаютчерез блок 1 контактирования и блок 2 развязывающих усилителей на информационные входы 22 анализатора .11 неизменных значений V или О, а через блок 4 входных вентилей - на входы эталонной схемы 5 . Блок 7 сравнения в каждом такте теста С11авнивает .. выходные сигналы контролируемой интегральной схеьа 1, поступакйиие через блок 3 дискриминаторов потенциалов, с ввжодными сигналами эталонной схе№1 5, поступающими через блок 6 71 выходных вентилей. Если в некотором такте теста блок 7 сравнения обнаружива ет неравенство значений этих сигналов, то этот факт фиксируется блоком 10 регистрации как.неправильное функционирование контролируемЪй интегральной схемы (логическая неиспр авность) Если в каком-либо такте дискриминаторы потенциалов блока 3 обнаруживакзт отклонение потенциалов на выходах контролируемой интегральной схемы, то блок 10 регистрации фиксирует эту неисправность (парамет)ическая неисправность). Если после прохождения всего теста анализатор 11 неизменных значений О ИЛИ.1 обнаруживает, что хотя бы йа одном из входов контролируемой интегральной схемы сигнал сохранял неизмейное значение 1 или О, о чем сигнализируют триггеры 17 и 18 и элементы ИЛИ 20, то блок 10 регистрации сигнализирует об этом. Если на этом входе в соответствии со схемой объекта контроля и контрольным тестом не предусмотр1ена подача постоянного сигнала и этот вход ий, тегральной схемы является одновремен но входом объекта контроля, то этот факт фиксируется как логическая неисправность. В том случае, если этот вход интегральной схемы не является входом объекта контроля, а , соединен е выходом акой-либо йттегральной схемы объекта контроля, то ; блок 1 контактирования подключают - к въгаодам этой инт1егральной схемы с целью определения значения сигна лов на.этом.выходе. Эталонная схема заменяется в соответствии с типом . новой выбранной интегральной схемы после чего к объекту повторно прикладьшается тест. Дри повторном приложении теста устройство рабо- тает также, как и в предыдущей чае. Если при этом после прохождений всего теста блок 10 регйстращ и не фиксирует на исследуемой выходе MiBHHoe значение t или О, соответству кяцее значение на входе первоначальйо контролируемой интегральной схемы то это интерпретируется как нейспрйв ность типа обрыв входа. Проверка качества тестов для циф ровых объектов может выполняться двумя способами. Первый из них ппедназначен дли : случа;я когда контроль объекта с 388 помощью выбранного теста осуществляется по сигналам на выводах интегральных схем. Проверка теста осуществляется на любом заведомо исправном образце, а данное устройство обеспечиваетмоделирование поведения его интегральных схем при наличии неисправности. Функции схемы - модели для выбранной интегральной схемы - объекта в устройстве выполняет однотипная ей эталонная схема 5 вместе с блоками 4 и 6 входных и выходных вентилей. Для проверки качества теста блок 1 контактирования подключается к вьгоодам выбранной интегральной схемы. Счетчик 8 приводится с помощью органов ручного.управления в определенное состояние, имитирукицее неисправность, после чего к объекту прикладывается проверяемый тест. : ,. Работа устройства при проверке качества теста происходит также, как и йри контроле неисправностей интегральной схемы, и отличается только тем, что сигнал с одного из выходов дешифратора 9 через один ид входных вентилей блока 4 или выходных вентилей 6 устанавливае± на одном из выводов эталонной схемы 5 неизменное значение 1 или О, имитирующее неисправность. Факт обнаружения блоком 7 сравнения неравенства сравниваеъв 1х сигналов рассматривается в этом случае как положительный результат проверки теста на за-, данную неисправность. После окончания п риложения теста на индикацию блока 10 регистрации выводятся сведения о неизменных значениях 1 или О на выводах интеграпь ной схемы объекта. Их наличие свидетельствует о непригодности теста и необходимости его корректировки. Если например, на одном из выводов интегральной схемы зафиксировано, неизменное значение это свидетельствует о том, что проверяемый тест не обнаруживает на этом выводе Неисправность неизменное значение 1, В случае, е. неизменвых значений 1 или О не зарегистрировано имитируется следующая неисправность путем изменения состЬяния Счетчика 8,, и процесс npoisepKii теста |фОдолжаетсЯ повторным запуЬком теста. . . - . / , Второй способ проверки качества теста предполагает, что контроль объекта с 1пм«ощыо выбранного tecta осуйестаяйется по сигналам с выходов овъеклга. В э-гой случае при проверке теста используется специальный обраgfeft otJbeitTS в Котором каждая интегральная схеиа имеет разъемное соединение с моягажом. Для моделирования ненсправяосте(1 какой-либо нитегральHtxtt схем та схема 1зынимается из ра:|ъеиа н вместо нее к этому разъему подключается блок t кон тактирования. В уст|кз(йстве устанавливается эталонная схема 5, однотипная той схеме объекта, которую заменяет, йа штате, raft размечается эталонная схема 5, устанавл гиот пере агчки, обеспечит 0ающие соединение выходов вентилей 6 через блок 1 контактирования с контакта разъема интегральной схемы объекта, которые соответствуют выходам этой схемы. В результате вместо интегральной схемь объекта оказывается подключенной к объекту так)ая же интегральная схема (зталонная схема 5), но при этом ее входы подкл1бчены к объекту через блок А 1

Фиг.1 3810 входных-вентилей, а выходы - через выходные вентили блока 6, Такое включение эталонной схемы позволяет обеспечить имитацию ее неисправностей непосредственно в объекте. Само устройство работает также, как и при предьщущем .способе проверки качества теста, но блок 7-сравнейия блокируется, а оценка качества теста устанавливается по сигналам с выходов о&ьекта контроля вне устройства и по индуцируемым блокам to регистрации . неизменнь зНачейиям 1 или О, зафикскровДнным на выводах эталонной схемы. . В предлагаемом устройстве имеется возможность обнаружения дополнительных типов неисправностей как самой интегральной схеьш в объекте так и монтажа объекта, чТо позволяет однозначно определить исправность или неисправность всего цифрового объекта Кроме того, устройство позволяет значительно сократить время моделиррвания неисправностей при оценке качества теста.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника | |||

| Пер, с англ., 1973 | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

Авторы

Даты

1984-03-30—Публикация

1980-12-15—Подача