1

Изобретение относится к области вычислительной техники, и в частности, к средствам контроля цифровых модулей. Оно может быть использовано для целей функциональной проверки и диагностики неисправностей средств вычислительной техники и автоматики в процессе их производства и технического обслуживания.

Известно устройство для контроля интегральных схем, установленных в различных цифровых модулях, которое обеспечивает поочередную проверку каждой интегральной схемы, входящей в состав объекта контроля, путем сравнения ее выходных сигналов с выходными сигналами однотипной эталонной схемы, на входы которой прикладываются сигналы, снимаемые со входов контролируемой интегральной схемы объекта. Для задания сигналов на входы контролируемой интегральной схемы используется внешний по отношению к устройству генератор тестов, подключаемый ко входам объекта 1.

Наиболее близким техническим решением к данному изобретению является устройство II для контроля интегральных схем, содержаш;ее эталонную интегральную схему, входы которой подключены к выходам буферных элементов, блок сравнения, соединенный с выходами буферных элементов и эталонной интегральной схемы, блок индикации, соединенный входами с выходами буферных элементов и блока сравнения.

Недостатком известных устройств являются ограниченные функциональные возможности. Они позволяют зафиксировать неисправность контролируемой интегральной схемы только при условиях полноты и корректности используемых тестов.

Указапные условия далеко не всегда удовлетворяются на практике, и поэтому для обнаружения неисправностей интегральных схем в объектах требуется проверять как полноту и корректность тестов, так и поведение контролируемой и эталонной схем в различных тактах теста. Такая необходимость возникает, например, в случаях, когда устройство обнаруживает различие выходных сигналов контролируемой и эталонной схем. Если последовательность входных сигналов контролируемой схемы некорректна, то это различие возможно и при полной исправности контролируемой схемы и является результатом неоднозначного поведения обеих схем из-за разброса собственных задержек их элементов.

Для анализа тестов и поведения контролируемой и эталонной схем путем наблюдения состояния их выводов, а также выводов других интегральных схем объекта требуется обеспечить возможность останова теста (с

фиксацией состояния объекта) непосредственно в том такте, в котором обнаружено различие выходных сигналов обеих схем, и возможность останова теста при возникновении определенных (заданных) значений снгналов на входах контролируемой и эталонной схемы или определенных значений выходных сигналов контролируемой схемы. Известные устройства не имеют таких возможностей, что сильно затрудняет обнаружение многих неисправностей интегральных схем и может приводить к ошибочной браковке исправных интегральных схем.

Предлагаемое устройство в значительной степени устраняет этот недостаток известных устройств.

Целью изобретения является повышение достоверности процесса обнаружения неисправностей цифровых модулей путем обеспечения следуюш,их режимов останова теста: при обнаружении устройством отклонения входных нли выходных сигналов контролируемой схемы за пределы областей потенциалов, соответствуюш;их логическим значениям «1 и при обнаружении неравенства логических значений выходных сигналов контролируемой и эталонной схем; при появлении заданной комбинации значений сигналов на входах или выходах контролируемой схемы.

Эта цель достигается тем, что устройство содержит селектор состояний выводов интегральной схемы, входы которого соединены с выходами буферных элементов, и дешифратор условий останова теста, входы которого подключены к выходам буферных элементов, блока сравнения и селектора состояний выводов интегральной схемы.

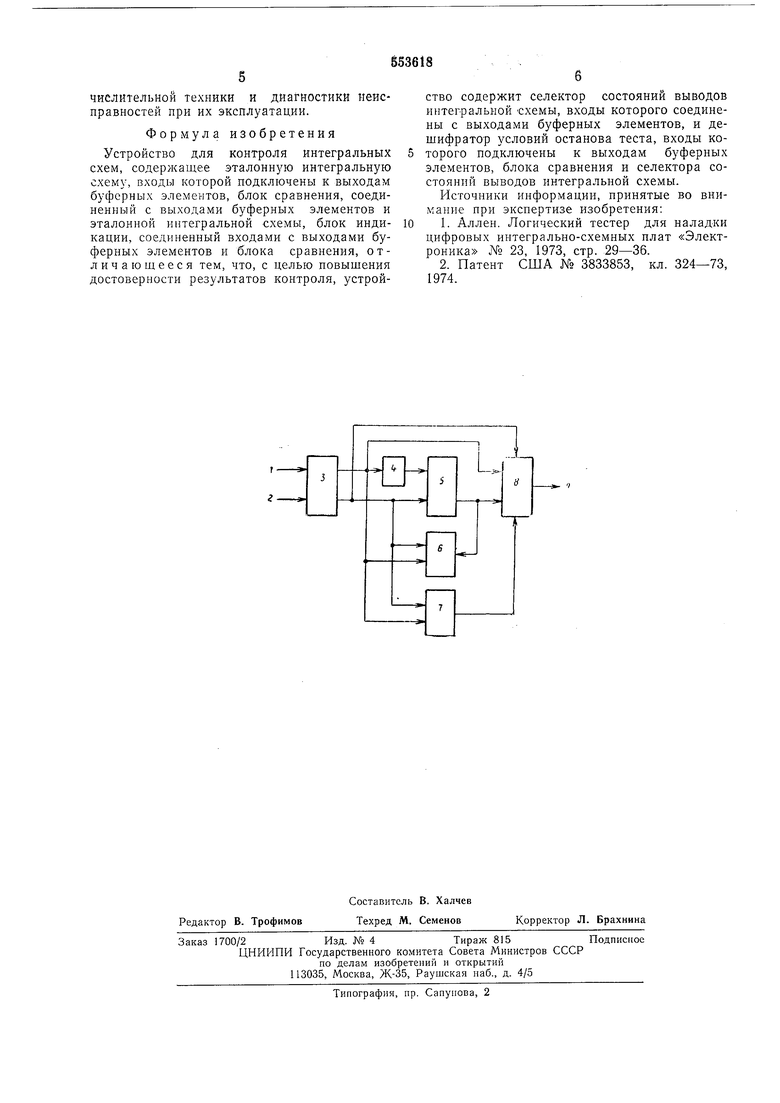

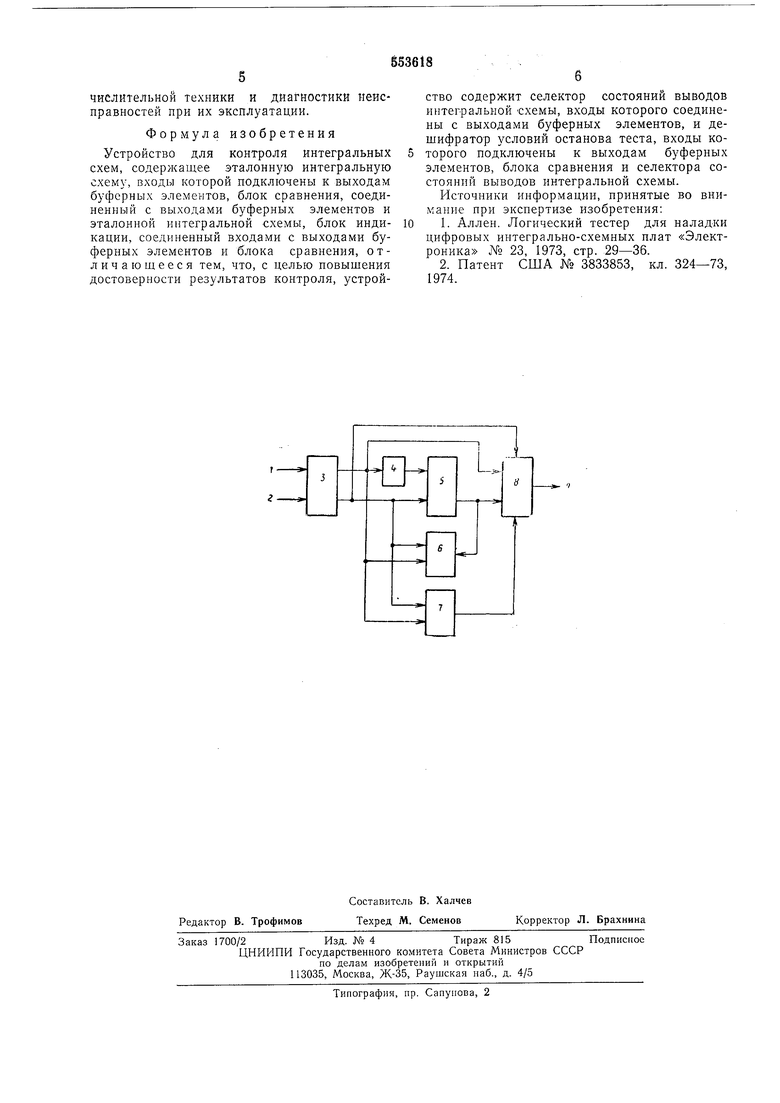

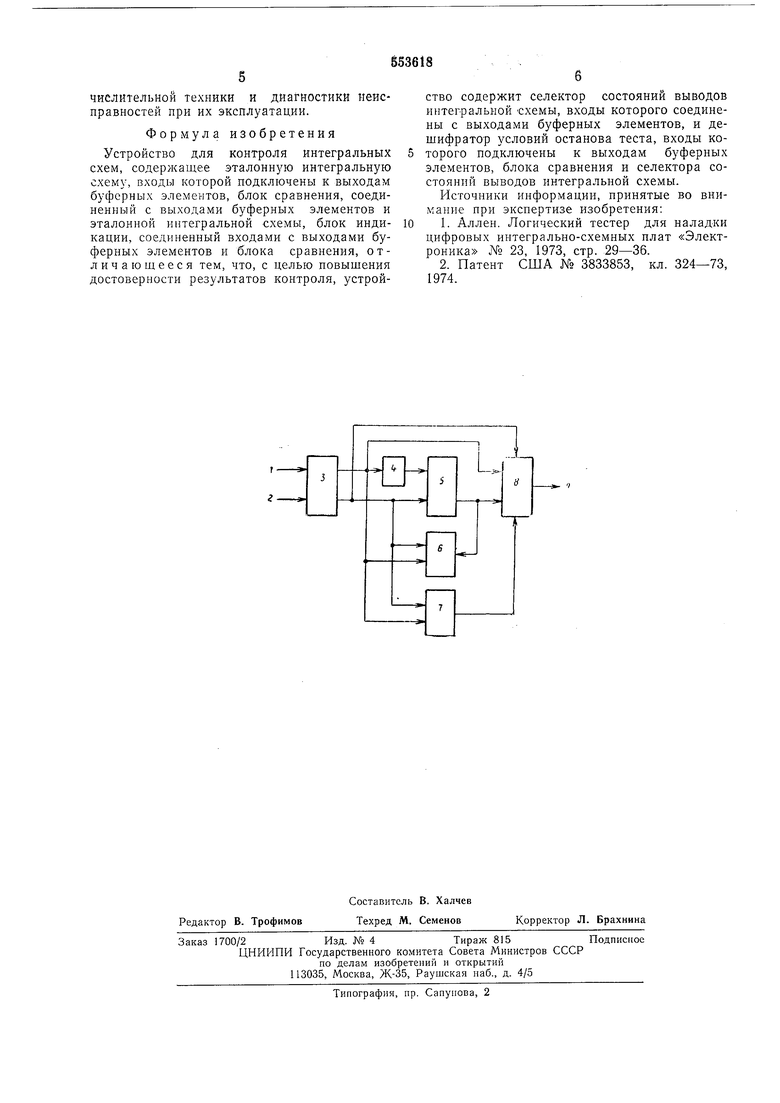

Блок-схема устройства представлена на чертеже.

Устройство содержит связанные со входами 1 и 2 буферные элементы 3, которые обеспечивают его развязку от контролируемой интегральной Схемы и допусковый контроль потенциалов «1 и «О на выводах этой схемы; эталонную интегральную схему 4 однотипную контролируемой схеме, блок сравнения 5, обеспечивающий сравнение выходных сигналов контролируемой и эталонной интегральных схем; блок индикации 6, который осуществляет отображение результатов сравнения, а также логических состояний («1 и «О) выводов контролируемой интегральной схемы; селектор 7 состояний выводов интегральной схемы, предназначенный для задания и обнаружения состояния, при котором требуется произвести останов теста; дешифратор 8 условий останова теста, который служит для формирования сигналов на выходе 9 устройства, вызывающих останов теста при отклонении входных или выходных потенциалов контролируемой интегральной схемы за пределы допусков для «1 и «О, при несовпадении состояний выходов контролируемой и эталонной интегральных схем, или при наличии сигнала от селектора 7,

фиксирующего СОйпадение состояния выводов контролируемой схемы с заданными.

Устройство работает следующим образом.

Входы 1, 2 устройства подключаются к выводам выбранной интегральной схемы цифрового модуля и ко входам этого модуля прикладывается тест, вырабатываемый некоторым внешним устройством задания тестов. Сигналы, возникающие на входах контролируемой интегральной схемы, в каждом такте теста поступают на входы 1 предлагаемого устройства и далее, через буферные элементы 3, на входы эталонной интегральной схемы 4. Выходные сигналы контролируемой интегральной схемы через входы 2 и элементы 3 передаются в блок 5, который сравнивает их в каждом такте теста с выходными сигналами схемы 4 и выдает сигнал о результате сравнения на один из входов дешифратора 8.

Сигналы, действующие на выводах контролируемой интегральной схемы, с выходов элементов 3 передаются также на входы селектора 7 состояний выводов. Селектор 7 производит сопоставление логических значений этих сигналов со значениями, записанными в него предварительно, и при их совпадении выдает сигнал на вход дешифратора 8. Кроме этого сигнала и сигнала блока сравнения 5 ,в дешифратор 8 поступают также сигналы с выходов буферных элементов 3, отображающие результат допускового контроля сигналов на выводах контролируемой интегральной схемы на нахождение в границах областей потенциалов «1 и «О. Дешифратор 8 анализирует в каждом такте теста значения всех указанных сигналов и при соответствующих их значениях вырабатывает на выходе 9 устройства сигнал останова теста непосредственно в том его такте, в котором возникли условия останова. Предлагаемое устройство обеспечивает следующие режимы останова (задаются органами ручного управления, входящими в состав дешифратора 8): при отклонении сигналов на выводах контролируемой интегральной схемы за пределы областей потенциалов «1 и при несовпадении логических значений выходных сигналов контролируемой и эталонной интегральных схем; при совпадении логических значений сигналов па выводах контролируемой интегральной схемы с значениями, предварительно заданными в селекторе состояний выводов.

При каждом из указанных остановов блок индикации 6 обеспечивает индикацию логических значений выводов контролируемой интегральной схемы, результатов сравнения значений ее -выходов и выходов эталонной схемы, результатов допускового контроля сигналов.

Основной эффект, достигаемый в результате использования изобретения, заключается в повышении достоверности контроля и ускорении процесса наладки цифровых устройств в условиях производства средств вычислительной техники и диагностики неисправностей при их эксплуатации.

Формула изобретения

Устройство для контроля интегральных схем, содержащее эталонную интегральную схему, входы которой подключены к выходам буферных элементов, блок сравнения, соединенный с выходами буферных элементов и эталонной интегральной схемы, блок индикации, соединенный входами с выходами буферных элементов и блока сравнения, отличающееся тем, что, с целью повышения достоверности результатов контроля, устройство содержит селектор состояний выводов интегральной схемы, входы которого соединены с выходами буферных элементов, и дешифратор условий останова теста, входы которого подключены к выходам буферных элементов, блока сравнения и селектора состояний выводов интегральной схемы.

Источники информации, принятые во внимание при экспертизе изобретения: 1. Аллен. Логический тестер для наладки цифровых интегрально-схемных плат «Электроника № 23, 1973, стр. 29-36.

2. Патент США № 3833853, кл. 324-73, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных схем | 1981 |

|

SU1029146A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1141414A1 |

| Устройство для контроля неисправностей интегральных схем | 1974 |

|

SU528517A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1984 |

|

SU1264182A2 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Тестер для контроля цифровых блоков | 1986 |

|

SU1555704A1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

Авторы

Даты

1977-04-05—Публикация

1975-11-06—Подача