(54) УСТРОЙСТВО ДЛЯ ПРИЕМА САМОСИНХРОНИЗЛРУЩЕЙСЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1080252A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1980 |

|

SU924902A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1030989A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1984 |

|

SU1228296A2 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Устройство цикловой синхронизации для внешней памяти | 1983 |

|

SU1092510A1 |

| Автокорреляционный приемник сигналов с относительной фазовой модуляцией | 1981 |

|

SU1021015A1 |

1

I Изобретение относится к средствам связи и может использоваться в каналах связи в составе аппаратуры передачи данных.

Известно устройство для приема самосинхронизирующейся дискретной информации , содержащее блок коммутации, регистр сдвига, селектор синхросигнала, накопитель, блок обработки сигналов и приемник, вход которого соединен с входом блока обт работки сигналов, выход приемника подключен к входу - накопителя, выходы регистра сдвига соединены с соответствующими входами блока коммутации l .

Однако известное устройство .не позволяет эффективно использовать пропускную способность используемого канала связи, прскольку оно предполагает разделительную передачу синхронизирующей кодовой комбинации и информационной.

Цель изобретения - повышение объема принимаемой информации.

Для этого в устройство для приема самосинхронизирующейся дискретной информации, содержащее блок коммутаНИИ, регистр сдвига, селектор синхросигнала, накооитель, блок обработки сигналов и приемник, вход которого соединен с входом блока обработки сигналов, выход приемника подключен к входу накопителя, выходы регистра сдвига соединены с соответствующими входами блока коммутации, введены элемент памяти и декодер,-входы которого соединены с соответствующими выходами блока коммутации,

0 вход регистра сдвига соединен с выходом Элемента памяти, входы которого соединены с соответствующими выходами блока обработки сигналов, выходы накопителя соединены с соответ5ствующими входами селектора синхросигнала, выход которого подключен к управляющему входу блока коммутации.

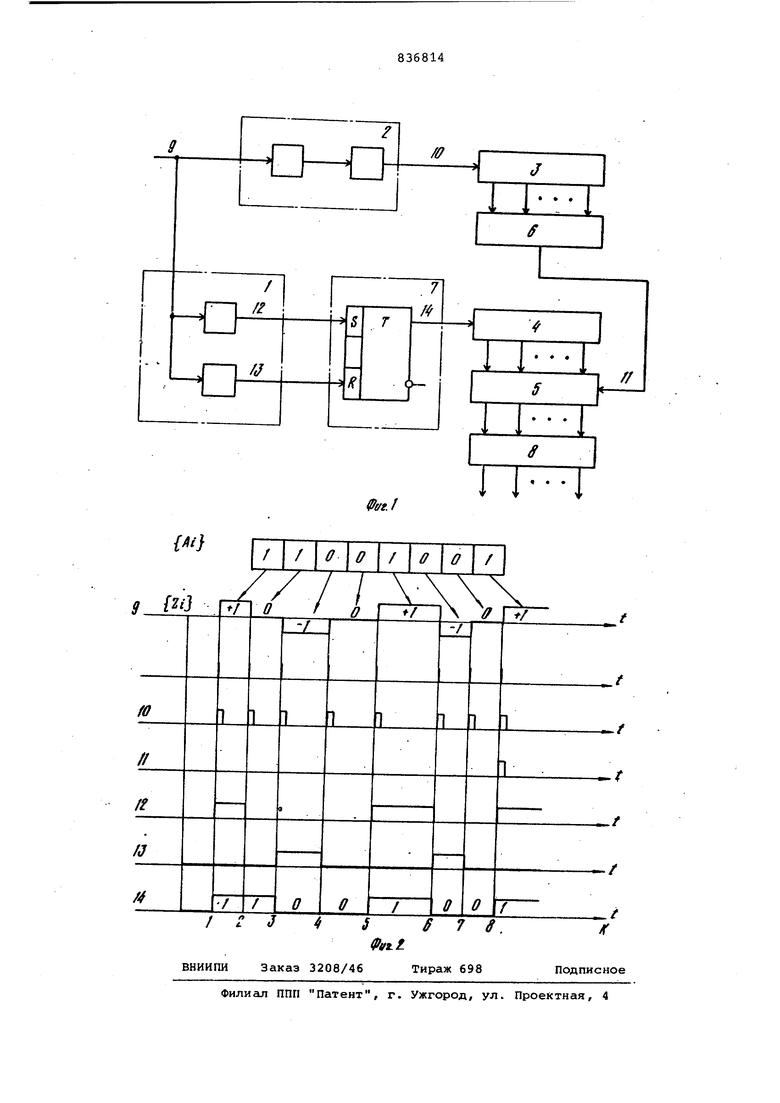

На фиг. 1 представлена структурная электрическая схема предложенно0го устройства; на фиг. 2 - эпюры напряжения, поясняющие работу устройства.

Устройство содержит блок 1 обработки сигналов, состоящий из селек5торов положительной и отрицательной посылки, приемник 2, содержащий блок выделения значащих характеристических моментов восстановления сигнала и формирователь импульсов заданной дли0тельности, накопитель 3, регистр 4

сдвига, блок 5 коммутации, селектор синхросигнала, элемент 7 памяти и декодер 8.

Устройство для приема сгииосинхронизирунгщейся дискретной информации работает следующим образом.

Самосинхрониэирующаяся импульсная троичная последовательность {2.1 (фиг. 2), сформированная на передатчике из двоичной последовательности JAi по следующему закону: Zk « Xk -jrj, Xk « Ak Xk - 1 , Yk « Ak Yk - 1 , где k « 1 , TT соответствует порядковому номеру значащего характеристического.момента мо.дуляции передаваемого сигнала , поступает на входы 9 приемника 2 и блока 1 обработки сигналов. В приемнике 2 происходит вьаделение фронтов приходящего сигнала и формирование сигналов. На выходе приемника 2 формируются импульсы заданной длительности, .которые подаются на вход 10 накопителя 3. При окончании записи рабочей кодовой комбинации в накопит ,тель 3, селектор б синхросигнгша ее фиксирует и выдает на вход 14 блока 5 коммутации сигнал разрешения выдачи информации, записанной в регистре 4 сдвига.

Блок 1 выделяет в принимаемой последовательности положительные и отрицательные посылки. На выходе 12 блока 1 импульс появляется при наличии положительной посылки в самосинхронизирукщейся последовательности, .а на выходе 13 блока 1 - при наличии отрицательной посылки. Сигналы с выходов 12 и 13 поступают соответственно на S и R входы элемента 7 памяти, выполненного на R-S-триггере С выхода 14 элемента 7 памяти двоичная информационная последовательност поступает на вход регистра 4 сдвига. По сигналу с выхода 11 селектора б синхросигнала эта информационная последовательность через блок 5 комму,тации поступает в декодер 8, выполненый на регистре с параллельной записью, где преобразуется в знак сообщения.

Предложенное устройство, входящее в состав аппаратуры передачи данных при передаче коротких сообщений позволяет обеспечить более высокую скорость по сравнению -с прототипом. Выигрыш, в зависимости от длины сообщения, изменяется в пределах от 10100%.

Формула изобретения

Устройство для приема самосинхронизирующейся дискретной информации, содержащее блок коммутации, регистр сдвига, селектор синхросигнала, накопитель, блок обработки сигналов и приемник, вход которого соединен с входом блока обработки сигналов, выход приемника подключен к выходу накопителя, выходы регистра сдвига соединены с соответствующими входами блока коммутации, отличающес я тем, что, с целью повышения объема принимаемой информации, введены элемент пгшяти и декодер, входы которого соединены с соответствующими выходами блока коммутации, вход регистра сдвига соединен с выходом элемента памяти, входы которого соединены с соответствующими выходами блока обработки сигналов, выходы накопителя соединены-с соответствующим входами селектора синхросигнала, выход которого подключен к управляющему входу блока коммутации.

Источники информации, принятые во внимание при экспертизе

9

--J n

/ //

fj

f

у

//

11

0i/t.J

Авторы

Даты

1981-06-07—Публикация

1979-06-04—Подача