первого и второго триггеров результата, выход первого элемента ИЛИ соеди.нен с информационным входом второго блока памяти и вторым входом седьмого элемента И, выход которого соедине1| с информационным входом третьего блока памяти, выход второго элемента

ИЛИ соединен с нулевым входом триггера пуска, единичный вход которого является входом запуска устройства, выходы третьего и четвертого элементов И являются соответственно первым и вторым выходами ошибки устрой-ства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

.УСТРОЙСТВО ДЛЯ КОНТР01И. ; МИКРОПРОГРАММ , . содержащее первый- ., блок памяти, perHCTJp микрокоманд, . первый и;ВТОРОЙ триггеры.результата, триггер управления, первый, второй, третий и четвертый элементы И,, пер- ВЫЙ и второй элементы ЙЛИ, элемент задержки и блок элементов И,при« ем ВЫХОД первого элемента И соединен/ / с ВХОДОМ считывания перЕГого блока памяти, ВЫХОД которого соединен .. с ВХОДОМ регистра микрокоманд, вы- : ходы поля микроопераций и адресного поля регистра микрокоманд соединены с входами первого элемента ИЛИ, выход первого элемента задержки и ну:лёвой ВЫХОД триггера управления сое-. динены соответственнос первим и . вторым входами, второго элемента И, единичные выходы первого и второго триггеров результата соединены с первыми входами третьего и четвертого элементов И соответствеяно нулевые выходы первого и вхорог триггеров результата соединены с вторыми входами четверФого и fp&тьего элементов И соотвётетвеннй, .. рыходы которых соединены с первым и вторым входами второго элемента |ИЛИ соответственно, от ли ч a юИ её с я тем, что, с целью повы.шения надежности контроля в него .введены триггер пуска, одновибратор,- ; ,счетчик, второй и третий блоки памяти, коммутатор, пятый; шестой и седь.- : :мой -элементы :И, второй и третий .. -: .; .элементы задержки, причем вход синх:роимпул ьсов устройства и едиЙ11ЧН1 1й . V . ,ВЫХОД триггера пуска соединены со ответственно с. первым и вторьш вхо- : ;дами; пятого И, выход которо.го соединён спервыми входамц йер-; .;вого и шестого элементов И и через . первьай й- второй;, элеменч Ц) задержки v. е6 счетным вход(эм счетчика, гшкод-; . переполнения счетчика соединен со .. .счётным вх6дс л триггера управленид/- . информационные выходы счетчика соеди . яёны с ,адрееными входами; второго блр-S ка п алцтя, первыми йнформадаонными : .-.входами:.кс1ммутатора и первыми: входа:-: f/1| :г -,ми блока элементо:в И; .выходы которо- У,. .го соединены е информационными входа f /ми nepspEo блока памяти, единичный - :выход триггера управления. сое,Е йенч- g. :С первым управляющим входом , . тора ..ис вторда входом шестого ;элемей та И, йшсЬд Которого соединен с вхог дами Считывания второго и третьего/-: .блоков памяти и с входами синхррйи-зации Триггеров результата и через..,-: - третий элемент з адержки с третьими ; .входами третьего и четвертого э;лёментов И, нулевой ВЫХОД триггера -управ:Яения соединен с вторыми, входами . блока .элементов и, вторым входом пер..Вогй элемента И, вторым упра.влякадим ;звходон; коммутатора и через одновиб-. ;ратоЕ1.- с третггюв входом второгоэлемента ИЛИ выхрд адресного поля регистра мнк-Ё(Окоманд соединен с вторш .информационным входом коммутатора, ЭБКод KoTogfoFo соединвн с адресным Входом Фретьёго блока памяти, вы- . ход второго; элемента И соединен с первым входом седьмого.элемента и не ;входами записи второго и третьего блоков памяти, выходы которых сое;дкнены соответственно с D-входами

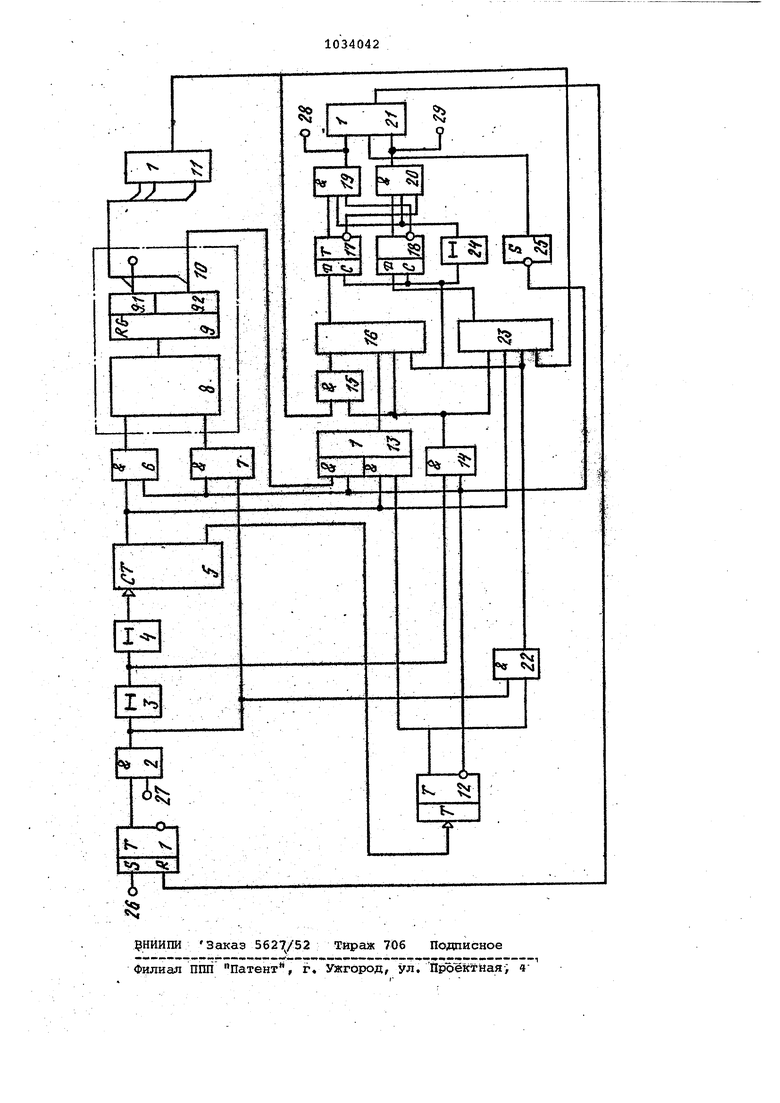

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке аппарату ры систем контроля программного обес печения. Известно устройство для контроля микропрограмм, содержащее контролиру мый микропрограммный автомат, элемен ты- И, ИЛИ, триггер, элемент задержки 1 . Недостатком указанного устройства является низкая полнота контроля, вызванная отсутствием средств контро ля субъективных ошибок. . Известно устройство для контроля выполнения программ, содержащее триг геры, элементы И, ИЛИ, элег1енты задержки, блок оперативной (динамической) памяти Сз}. .Недостатком данного устройства является большой объем средств кон-тро-; ля, обусловленный тем, что в устройстве должна храниться информация о всех разрешенных последовательностях модулей .программы. НаиболееблизКИМ к предлагаемому по. технической сущности и достигаемому положительному эффекту является устройство, содержащее блок памяти микропрограмм, регистр микрокоманд, регистр результата, триггер управления, первый, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, элемент задержки и блок элементов И, причем выход, первого элемента И соединен с входом считывания блока памяти микропрограмм выход которого соединен с входом регистра микрокоманд, выходы поля микроопераций и адресного поля регист- ра микрокоманд соединены с вх.одамй; п ервогЬ элемента ИЛИ, выход первого эл мента задержки и нулевой выход триггера управления .соединены соответственно с первым и вторым входами второго элемента И, единичные выходы f первого и.второго триггера результата соединены с первыми входами третьего и четвертого элементов И соответственно, нулевые выходы первого и второго триггера регистра результата соединены с вторыми входами четвертого и третьего элементов И соответственно, выходы которых соединены с первым и вторым входом второго элемента ИЛИ соответственно 3. Недостатком устройства является узкая область применения вследствие Низкой полноты контроля, субъективных ошибок,. в указанном устройстве осуществляется контроль cyбъekтивньD{, ошибок типа тупик, т.е. ошибок, допущенных на этапе проектирования и приво дящих к тому, что в микропрограмме (программе) существуют микрокоман,ды команды), не имеющие последователей. Таким образом, низкая полнота. контроля обусловлена ограниченным классом обнаруживаемых ошибок. Кроме того, указанное устройство ориентировано на испольэование в режиме основного функционирования контролируемого микропрограммного программного автомата, т.е. в режиме оперативного Контроля, что снижает надежность контроля автомата. Цель изобретения - повышение надежности контроля. Поставленная цель достигается тем, что в устройство для контроля микройрограмм:,- содержащее первый блок памяти, регистр, микрокоманд, первый и второй триггеры результата, триггер управления, первБй, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, элемент задержки и блок элементов И, причем выход первого элемента И соединен I. . . -. , с входом считывания, первого блока памяти микропрограмм, выход которого соединен с входом регистра микрокоманд, выходы поля микроопераций и адресного поля регистра мик:рокоманд соединены с входами первого элемента ИЛИ, выход первого элемента з лержки и нулевой выход триггера управления соединены сЬответственно с первым и вторым входами второго элемента И, единичные выходы первого и второго триггеров результата соединены с первыми входами третьего и четвертого элементов И соответственно, нулевые выходы первого и второго триггеров результата соединены с вторыми входами четвертого и третьего элементов И соответственно, выхо1ДЫ которых соединены с первьом и вторым входами второго элемента ИЛИ соответственно., введены триггер, пуска, одновибратор, счетчик, второй и, третий блоки памят, коммутатор, пятый, шестой и седьмой элементы И, второй и третий элементы задержки, причем вход синхроимпульсов устройст ва и единичный выход триггера пуска соединены соответственно с первым и вторым входами пятого элемента И, выход которого соединен с первыми входами первого и шестого элементов И и через первый и второй элементы задержки со счетным входом счетчика, выход переполнения счетчика соединен со счетным входом триггера управления, информационные выходы счетчика соединены с адресными входами второг блока памяти, первыми информационным вkoдaми .коммутатора и первьоти входами блока элементов И, выходы которого соединены с информационными входами первого блока памяти, единичный выход, триггера управления соединен с первым управляющим входом коммутатора и вторым. входом шестого элемеН та И, выход которогосоединен с входами считьтания второго и трЪтьего блоков памяти, с входами синхронизации триггеров результата и через третий элемент задержки с третьими входами третьего и четвертого элемен тов И, нулевой выход триггера управления соединен с вторыми входами бло ка элементов И, вторым входом первого Элемента И, вторьам управляющим входом коммутатора, и через одновибратор - с т ре-Гь им входом второго эле мента ИЛИ, выход адресного поля гистра микрокоманд соединен с вторым информационным входом коммутатора, выход которого соединен с адресным входом третьего блока памяти, выход второго элемента И соединен с первым входом седьмого элемента И и с входами записи второго и третьего блоков памяти, выходы которых соединены соответственно,с D-входами перво.го и второго триггеров результата, выход первого элемента ИЛИ соединен с информационным входом второго блок памяти и вторым входом седьмого элемента И, выход которого соединен с информационным входом третьего блока п:амяти, выход второго элемента ИЛИ соединен с нулевым входом тригге ;ра пуска, единичный вход которого является входом запуска устройства, выходы третьего и четвертого элементов И являются соответственна первым и вторым выходами ошибки устройства. Каждому слову (линейке)$,хранимоу в блоке памяти, ставится в соответствие двухразрядный признак 7(R,-, PI), причем ( О, если в линейке S информация {отсутствует,1, если в линейке 5у записана ненулевая информация. 1, если в адресной зоне блока памяти записан, адрес линейки S-f ; О, в противном случае. ,М - число линеек в блоке памяти. Тогда справедливо i следующее выраение00, если линейка не используется в микропрограммах, для записи микрокоманд; , 10,если в линейке записан а недостижимая микрокоманда, . (Ц) t; 03. если в линейке записана тупиковая микрокоманда, адресная часть которой является адресом линейки 5 , 11,если в линейке S.,- записана микрокоманда, которая не являет:Ся недостижимой и не является ;конечной микрокомандой тупико-. вого участка. Признаки формируются путем последовательного считывания информации из блока памяти и анализа адресных частей. Если ,10, то это свидетельствует о некорректности микропрограммы, т.е. .и в ней ошибок типа тупик или недостижимая- вершина. Комбйна ции f; С (О 0,11 являются раз рещенньми. Введение в устройство счетчика и обусловленных им связей позволяет формировать адреса линеек блоков памяти, а при выходе на последнюю линейку формировать сигнал управления режимом работы. Введение коммутатора и обусловленных им связей позволяет управлятьадресными цепями третьего блока памяти.- . Введение второго и третьего блоков пагляти и обусловленных связей необходимо для хранения признаков Р иР|г .. Введение триггера пуска, пятого элемента И и обусловленных, ими связей позволяет управлять подачей синхроимпульсов в устройство. Введение шестого элемента И и, обусловленных им связей необходимо управления подачей импульсов считывания во второй и третий блоки, памя- ти. , . . . - . Введение седьмого элемента И и обусловленных им связей позволяет управлять записью признака V, в тре- . тий блок памяти. Введение одновибратора и обусловленных им связей.позволяет формироIвать сигнал останова устройства посл окончания проверки. Соединение выходов третьего и чет вертого элементов И с выходами ошиЬкп устройства,а выхода второго эле мента ИЛИ с нулевым входом триггера пуска.позволяет формировать сигналы ошибки и блокировать при их появле- НИИ работу устройства. Введение второго элемента з.адержки и обусловленных им связей необходимо для задержки импульса на время записи информации во второй и третий блоки памяти. Введение .третьего элемент задерж ки и обусловленных им связей позволя ет задержать импульс опроса .тригг ров результата на время считывания. Информации из второго и/тре«ьего бло ков памяти. : На чертеже представлена функцио нальНая схема устройства для контроля микропрограмм . . . Устройство содержит триггер-. 1. пус . к.а, пятый элемент И 2, .первый 3 и .эт ррй 4 элементы задержки, тзчетчик 5, ;блок б элементов И, первый элемент И 7, первый блок 8 памяти микрокома;нд й-регистр 9 микрокоманд с Поля 1 и .адресным ,9,1 и микроопераций .§.,2, обрйзующие. контролируемый автомат . . .itO-, первый элемент-ИЛИ 11, трй-ггёр 12 управления, коммутатор 13, второй элемёнт-И 14, седьмой элемент И 15,.втдрой блок 16 памяти, первый:триггер 17 результата -и .второй .триггер . 18 результата, третий .19 и чет;ве: уы 1 20,элементы И, второй 21 и шестой 22 элементы И, третий блок 23 nateти.,-третий элемент 4 .заде.рж-ки и одно вибрато.р 25. Кроме тбго, символами 26-29 обозначены соответственно вход пуска и синхроимпульсювд: первый и второй выходы ошибки устройства. . ; В блоке 8 памяти хранится информация о микропрограммах (программах) которая считывается в регистр 9. Счетчик 5 осуществляет формирова.-вне адреса при считывании информации из блоков 8,16 и 23 памяти. Триггер 12 управляет режимом работы устройства, а триггер 1 - его .пуском и остановом.Блоки 16 и 23 памяти предназначены для хранения признаков Р Триггеры 17 и 18 осуществляют их поминание после считывания из блоков -16 и 23 памяти. Элементы И 22,14 и 15 управляют записью, считыванием информации из этих блоков. Коммутатор 13 адреса в зависимости от режима работы осуществляет коммутацию адресных цепей блока 16 памяти. ., Элемент ИЛИ 11 фиксирует ненулевой код, записанный в регистр 9. Элементы И 19 и 20 формируют сигналы ошибки на основе кода в триггерах 17 и 18, Элемент ИЛИ- 21 при появлении сигналов ошибки или окончании работы подает сигнал останова на триггер 1. Предлагаемое устройство функционирует в двух режимах.: режиме формирования признаков к режиме анализа признаков ,A/. Режим формирования признаков TL-IВ исходном состоянии все триггеры и счетчик обнулены, в блоках 16 и 23 памяти записана ну;левая, информация. В блоке 8 памяти записаны контролируемые микропрограммы (программы). В поле адреса последних микрокоманд записаны начальные адреса соответствующих микропрограмм. После прихода на выход.: 26 сигнала Пуск триггер 1 устанавливается в единичное состояние и первый импульс с входа 27 устройства проходит на выход элемента И 2. По этому импульсу прои.сходит считывание информации, хранимой в нулевой (начальной) линейке блока 8 памяти. С задержкой, равной времени считывания информации из блока 8., импульс появляется на выходе элемента 3 и разрешает запись информации- в блоки 16 и 23. Адрес в блок 16 подается с выхода поля 9.2 через коммутатор 13, а в блок 23 непосредственно с выходов счетчика 13.Если.по начальному адресу в блоке 8 записан ненулевой код, то .в блоки 16 и 23 по соответствующим адресам запишется единица, в противном случае -.нуль.: После записи информации в блоки 16 и 23 импул: с с выхсэра элемента 4задержки увеличив ает-.. на единицу содержимое счетчика 5, .формируя в нем адрес следующей линейки. С приходом очередного синхроишульса на вход. 27 цикл функционирования повторяется в соответствии с описанным: алгоритмом. С появлением на выходе счетчика 5сигнал-а переполнения, триггер 12 устанавливается в единичное соЬтояние и устройство переходит во второй режим. Режим анализа признаков 7f/ . Исходное состояние устройства пеед началом работы в этом режиме слеующее:; триггеры 1 к 12 находятся единичном состоянии, счетчик 5 и триггеры 17 и 18 обнулены., в блоках 16 и 23 памяти записаны признаки . . По первому импульсу, проходящему ерез элементы И 2 и ИЛИ. 22, происодит считывание информации из блоов 16 и 23 втриггеры 17 и 18. Адрес

ячейки, из которой считывается инфор мация из обоих блоков, определяется .кодом в счетчике 5. Посколькув нем записан нулевой код, то из блоков 16 и 23 считывается признак Kf , Тогда в соответствии с выражением (4) осуществляется его дешифрация: если . OOVll, то сигналы, стробируемые задержанным на время считывания информации сигналом с выхода1 элемента. 24 задержки,на выходах элементов И 19 и И 20 отсутствуют, и разражается прохождение следующего синхроимпульса; если 1fc 01V10, то появляется сигнал на выходе 28 или 29, котоЕ«й проходит через элемент ИЛИ 21 к обну ляет триггер пуска, информируя одновременно о типе ошибки.

При 12 OOV11 очередной импульс осуществляет считывание из блоков 16 и 23 признака IZ анализ которого

осуществляется аналогично описанному выше алгоритму.

Если после считывания последнего признака Т) ошибка не обнаруживается то По сигналу переполнения счетчика 5 триггер 12 устанавливается в нулевое состояние, а одновибратор 25 формирует .импульс обнуления триггера 1 пуска.

г ФакЕИМ образом, технические преимущества предлагаемого устройства по С1равнению с прототипом и базовым объектом .состоят в более высокой полноте контроля (в 2-3 раза) и более низкой Язбытбчности- программ и микропрограмм за счет вьствления и удаления нереализуемых участков.

Использование предлагаемого изобретения позволяет сократить сроки разра06тки/повысить надежность и каlecT bb программного обеспечения.

Авторы

Даты

1983-08-07—Публикация

1982-03-26—Подача