1

Изобретение относится к вычислительной технике и может быть использова1|О i-; буферных запоминающих чччройствах систем ввода информации многоканальи).1х измерительных комплексов.

Известное буферное запоминаю:асе устройство, содержащее накопите.чь, блоки ввода и вывода, и в нем испо:1ьзуется метод перекрестно-последовательного обращения. позволяющий осуществлять двухсторонний обмен информацией и совмещать ироиесс.ы ввода и вывода информации из нсмо 1|.

Однако использование данногс; ycTpoiicrва в системах ввода информацш; многчжанальных измерительных комплексов, когда последовательность опроса кана.юн; неизменна, а их количество равно или кратно и превышает количество ячеек буферного заноминающего устройства, отка;-; одной или нескольких ячеек нако11ите,1я нриводит к потерям информации от одного или нескольких каналов.

Наиболее близким к нpeдлaгaeмo.4y являетея буферное запоминающее устройство, содержащее наконит&ть, адресные входы которого соединены с выходами первого сумматора, первые входы которого нодключены к выходам элементов И-ИЛИ первой грунны, первые входы которых соединены с выходом первого элемента НЕ и нервы.м входом э.чсмента И, вход первого элемента НЕ подключен к вторы.м входам элементо:; И И.ЛИ первой группы, третьи и четвертые вхо:Ц)1 первой групгц э,1ементов И-И,1И COOTRCTственно соединены с выходами не)во1о и второго счетчиков, выходы переполнения первого и второго счетчиков соедигсны соответственно с первым и иторы.м входамм триггера, выход которого 11о;,кл 0че1-, к ггорому входу элемента И 2|.

Известное устройство отка;-;йх cj/uioP: или нескольких ячеек накопителя обссномивает равномерное распределение поч);. ко каждому из каналов в измерите.ль.1П;,1.х системах, формат данных которых .не njxiibrщает формата ячейки накопите,::.) бут:}орного заноминаюи;его устройства. Однако npi; невыполнении этого уеловия, кг)1да форми/г данных измерительных капа,п)в (.вы1пает формат ячейки накопителя и этом ycTpoiicTве нри отказе ячеек нако(щте,чя нозможнь) потери последовательно ностунающих измерений информационных кана.нзв, что в некоторых случаях недопустимо, несмотря ;ia избыточность постунаюн1,ей 11П(№рмацпи,

Цель изобретения -- иовьпнение надежности устройства за счет выран1-: П5;:1|ия вероятности нотерь по каждому из КоНа„чо 3 измерительной систе.мы.

Поставленная цель дос гигается тем, ч го в буферное зано.минающее устр(1Йство, содержащее накопитель, информа1.;ионн11 е nxfiды и выходы которого соответственно являются информационными входами и выходами устройства, вход управления --- пе|)вым ун;;.::45ляю1цим входо.м устройства, а адpeci:i ic входы накопителя соединены с выхо;|,ал;и первого сумматора, одни из входов которого 11одк;1ючены к в)1ходам э.пементов И-ИЛИ первой группы, первые входы которых соединены е выходом нервого элемента HF; и нервьгм нходо.м эле.мента И, вторые входы объединены с входом первого элемента НЕ и яв.чяются вторым управляющим входом устройства, третьи и четвертые входы

0 элементов И-ИЛИ первой группы соответственно соединены с информационными выходами первого и второго счетчиков, счетные входы которых являются соответственно третьим и четвертым управляющи.ми входами уетройства, выходы переполнения первого и второго счетчиков соединены соответственно с первым и вторы.м входами триггера зыход которого подключен к второму входу э;1е.мента И, установочные входы счетчиков и триггера об1зединены и являются пятым

0 унравляюп1им входом устройства, введены регистр, второй сумматор, второй элемент НЕ и вторая группа элементов И-ИЛИ, первые входы которых соединены с выходом второго элемента НЕ, вход которого подключен к выходу элемента И и вторы.м вхо5 дам элементов И-ИЛИ, второй группы, треТпИ входы которых соединень с выхода.ми второго сумматора информационными входа.л;и регистра, выходы которого подклю-юны к одпим из входов втор,ого сумматора : четвертым входам элементов И-ИЛИ вто :Сй группы, выходы которых соединены с друг.чми вхо.1,ами первого сум.матора, вход .записи регистра соединен с выходом пере1К).; 1 е:п-1я второго счетчика, другие входы иторОГо сумматора являются щесты.м упра1, входом устройства, вход управ- леняя регистра подключен к пятому управля ionieMv входу устройства.

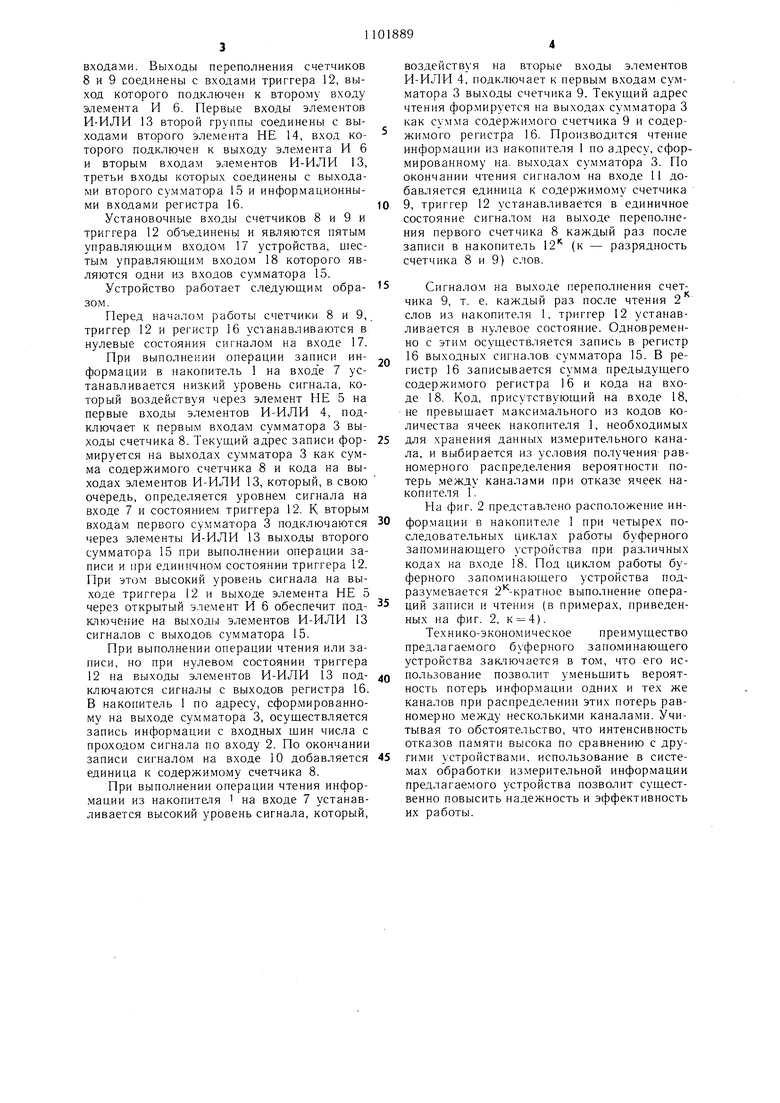

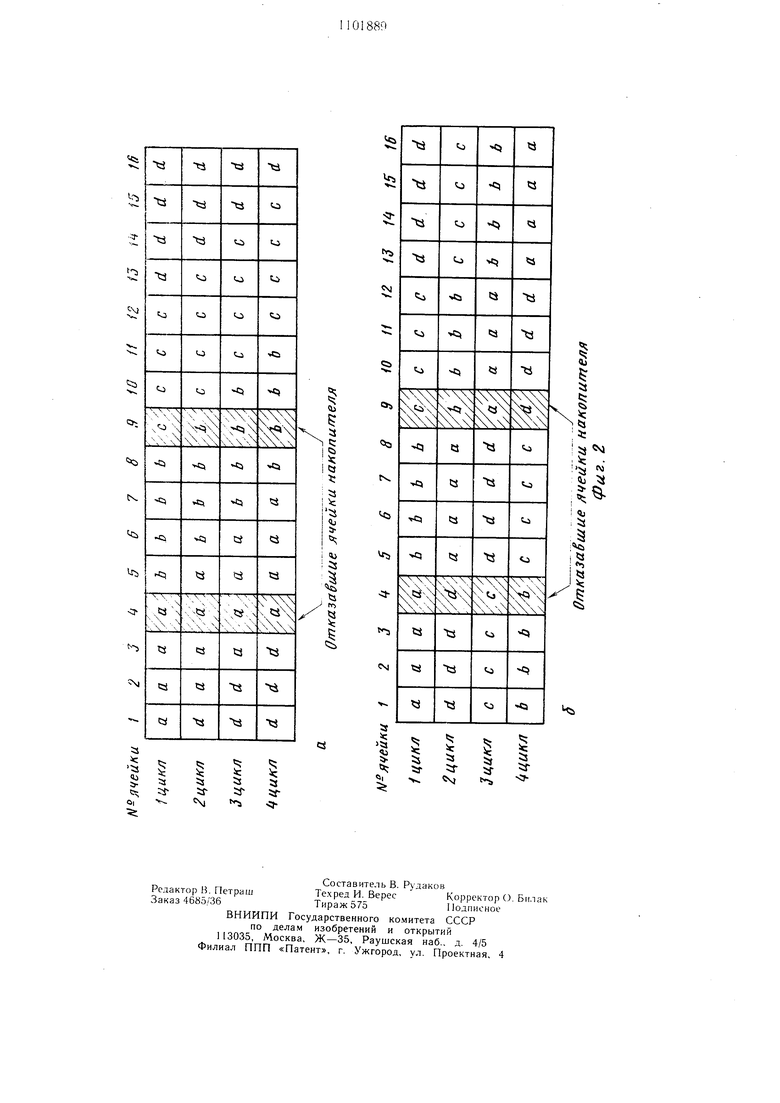

ila фиг. i представлена структурная схема б ферного запоминающего устройства; на фиг. 2 -- распределение инс|)0рмации в

0 ;1.: конителе при коде sia входе 18. равном 1 la, ), с, d -- данные измериге.1ьн:ых каналов), и при коде на входе 18, равном 4. Буферное запоминающее устройство (фиг. 1) содержит накопитель 1, вход управ;1е|гия которого является первым управ- .1ЯЮ1ЦИМ входом 2 устройства, адресные .)1 которого подключены к выходам перlioio сумматора 3, первые входы которого подключены к выхода.м элементов И-ИЛИ 4 первой группы. Первые входы элементов И-ИЛИ 4 соединены с выходом первого элемента НЕ 5 и первым входом элемента И 6. Вход элемента НЕ 5 подключен к вторым входам элементов И-ИЛИ 4 и к второму управляюнхему входу 7 устройства. Третьи и четвертые входы элементов И-ИЛИ 4 сое,j5 динеьП) соответственно с выходами первого счетч жа 8 и второго счетчика 9, счетные которых являются соответственно третьим 10 и четвертым 1 управляющими

входами. Выходы переполнения счетчиков 8 и 9 соединены с входами триггера 12, выход которого подключен к второму входу элемента И 6. Первые входы элементов И-ИЛИ 13 второй группы соединены с выходами второго элемента НЕ 14, вход которого подключен к выходу элемента И 6 и вторым входам элементов И-ИЛИ 13, третьи входы которых соединены с выходами второго сумматора 15 и информационными входами регистра 16.

Установочные входы счетчиков 8 и 9 и триггера 12 объединены и являются пятым управляюилим входом 17 устройства, шестым управляющим входом 18 которого являются одни из входов сумматора 15.

Устройство работает следующим образом.

Перед началом работы счетчики 8 и 9, триггер 12 и регистр 16 успанавливаются в нулевые состояния сигналом на входе 17.

При выполнении операции записи информации в накопитель 1 на входе 7 устанавливается низкий уровень сигнала, которь й воздействуя через элемент НЕ 5 на первые входы элементов И-ИЛИ 4, подключает к первым входам сумматора 3 выходы счетчика 8. Текущий ад,рес записи формируется на выходах сумматора 3 как сумма содержимого счетчика 8 и кода на выходах элементов И-ИЛИ 13, который, в свою очередь, определяется уровнем сигнала на входе 7 и состоянием триггера 12. К вторым входам первого су.мматора 3 подключаются через элементы И-ИЛИ 13 выходы второго сумматора 15 при выполнении операции записи и при единичном состоянии триггера 12. При этом высокий уровень сигнала на выходе триггера 12 и выходе элемента НЕ 5 через открытый элемент И 6 обеспечит подключение на выходы эле.ментов И-ИЛИ 13 сигналов с выходов сумматора 15.

При выполнении операции чтения или записи, но при нулевом состоянии триггера 12 на выходы элементов И-ИЛИ 13 подключаются сигналы с выходов регистра 16. В накопитель 1 по адресу, сформированному на выходе сумматора 3, осуществляется запись информации с входных щин числа с проходом сигнала по входу 2. По окончании записи сигналом на входе 10 добавляется единица к содержимому счетчика 8.

При выполнении операции чтения информации из накопите 1я 1 на входе 7 устанавливается высокий уровень сигнала, который.

воздействуя на вторые входы элементов И-ИЛИ 4, подключает к первым входам сумматора 3 выходы счетчика 9. Текущий адрес чтения формируется на выходах сумматора 3 как сумма содержимого счетчика 9 и содер жимого регистра 16. Производится чтение информации из накопителя 1 по адресу, сформированному на, выходах сумматора 3. По окончании чтения сигнало.м на входе И добавляется единица к содержимому счетчика 0 9, триггер 12 устанавливается в единичное состояние сигналом на выходе переполнения первого счетчика 8 каждый раз после записи в накопитель 12 (к - разрядность счетчика 8 и 9) слов.

5Сигнало.м на выходе переполнения счетчика 9, т. е. каждый раз после чтения 2 слов из накопителя 1, триггер 12 устанавливается в нулевое состояние. Одновременно с этим осуществляется запись в регистр

Q 16 выходных сигналов сумматора 15. В регистр 16 записывается сумма предыдущего содержимого регистра 16 и кода на входе 18. Код, присутствующий на входе 18, не превышает максимального из кодов количества ячеек накопителя 1, необходимых

5 для хранения данных измерительного канала, и выбирается из условия получения равномерного распределения вероятности потерь .между канала.ми при отказе ячеек накопителя 1.

На фиг. 2 представлено расположение ин0 формации в накопителе 1 при четырех последовательных циклах работы буферного запоминающего устройства при различных кодах на входе 18. Под циклом работы буферного запоминающего устройства подразумевается 2 -кратное выполнение операции записи и чтения (в примерах, приведенных на фиг. 2, к 4).

Технико-экономическое преимущество предлагаемого буферного запоминающего устройства заключается в том, что его использование позволит уменьшить вероятность потерь информации одних и тех же каналов при распределении этих потерь равномерно .между несколькими каналами. Учитывая то обстоятельство, что интенсивность отказов памяти высока по сравнению с дру5 гими устройствами, использование в системах обработки измерительной информации предлагаемого устройства позволит существенно повысить надежность и эффективность их работы.

s:

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1034069A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361633A2 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1981 |

|

SU982095A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, информационные входы и выходы которого соответственно являются информационными входами и выходами устройства, вход управления - первы.м управляющим входом устройства, а адресные входы соединены с выходами первого сумматора, одни из входов которого подключены к выходам элементов И-ИЛИ первой группы, первые входы которых соединены с выходом первого элемента НЕ и первым входом элемента И, вторые входы объединены с входом первого элемента НЕ и являются вторым управляющим входом устройства, третьи и четвертые входы эле.ментов И-ИЛИ первой группы соответственно соединены с информационными выходами первого и второго счетчиков, счетные входы которых являются соответственно третьи.м и четвертым управляюн1ими входами устройства, выходы переполнения первого и второго счетчиков соединены соответственно с первым и вторым входами триггера, выход которого подключен к второму входу элемента И, установочные входы счетчиков и триггера объединены и являются пятым управляющим входом устройства, отличающееся те.м, что, с це,:ыо повышения надежности устройства, в него введены )егистр, второй сумматор, второй элемент 111г и вторая группа элементов И-ИЛИ, первые входы которых соединены с выходом второго элемента НЕ, вход которого подк.почен к выходу элемента И п вторы.м входам эле.ментов И-ИЛИ второй г)уппы, третьи в.ходы которых соединены с выходами второго сумматора и информационными входами гистра, выходы которого подключены к од(Л ним из входов второго сумматора и четвертым входам элементов И-ИЛИ второй группы, выходы которых соединены с другими входами первого сумматора, вход записи регистра соединен с выходом переполнения второго счетчика, другие входы второго сумматора являются щестым управляющи.м входом устройства, вход управления регистра подключен к пятому управляюще.му входу устройства. ОС 00 ;о

b

3

1 С I

|

: :s

Li i J

; 5s

1

.S

I I

I

a 5:

1 M

Uxj ()

«:

Cj

,td. I ij

5s

:l

S

,S

I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Буферное запоминающее устройство | 1979 |

|

SU822287A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3411800/24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-07—Публикация

1983-04-08—Подача