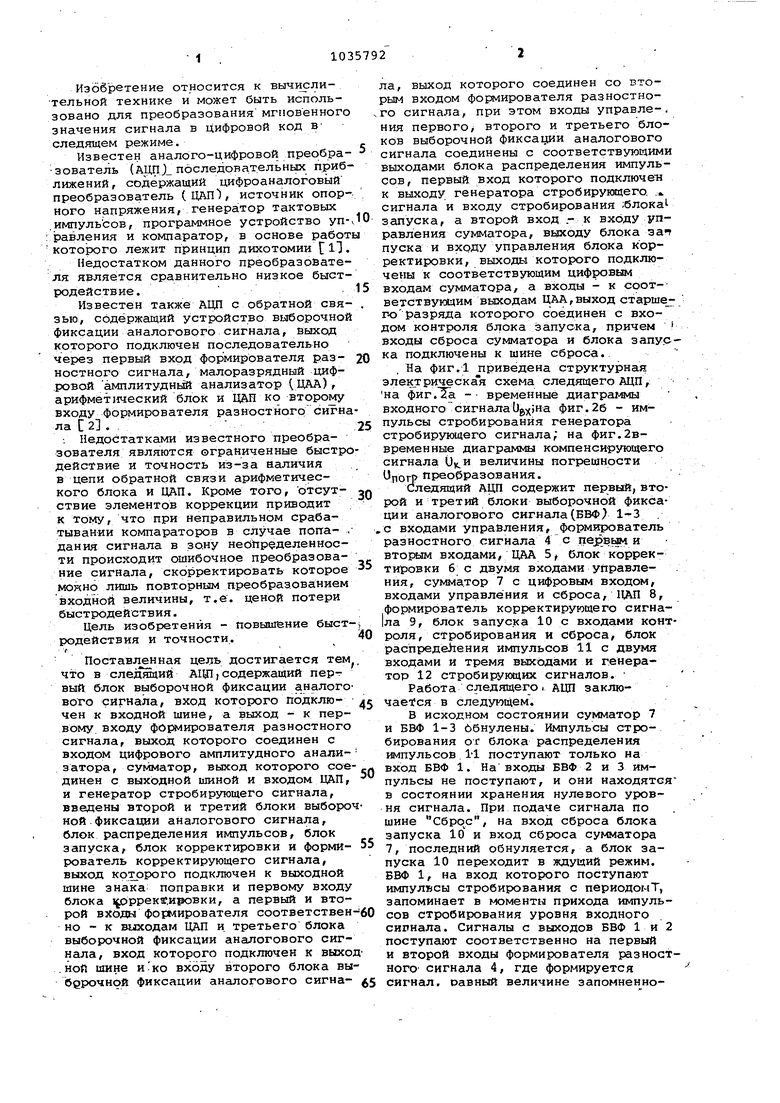

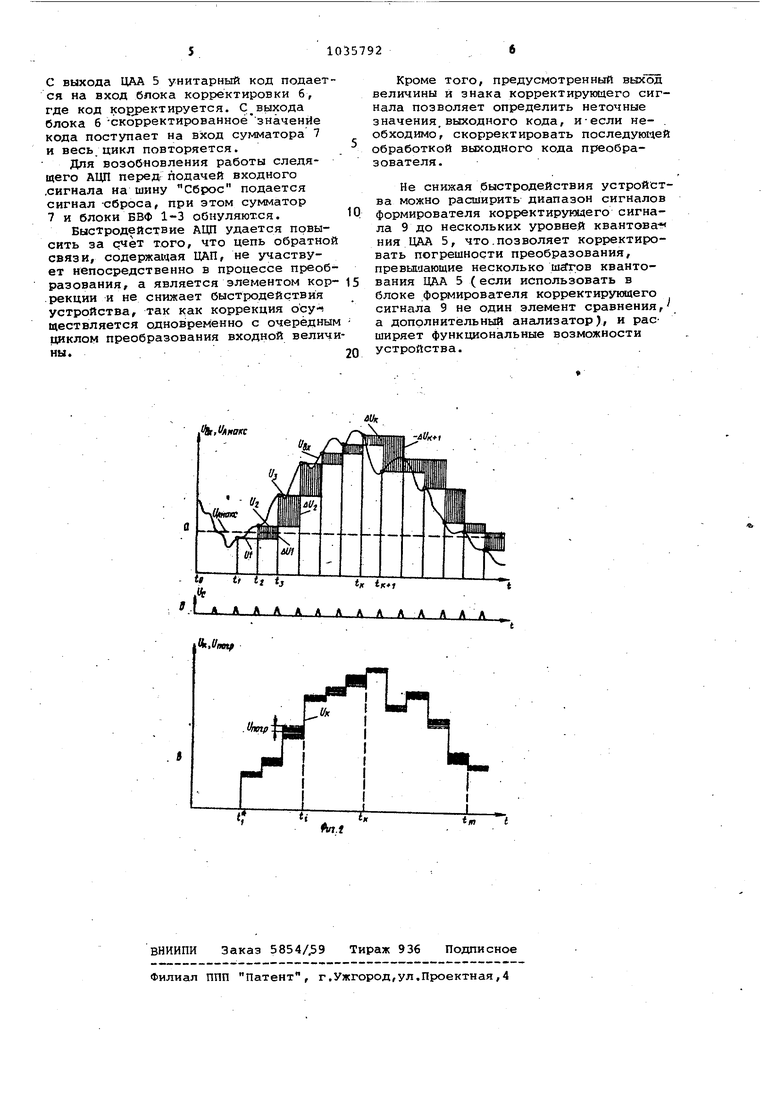

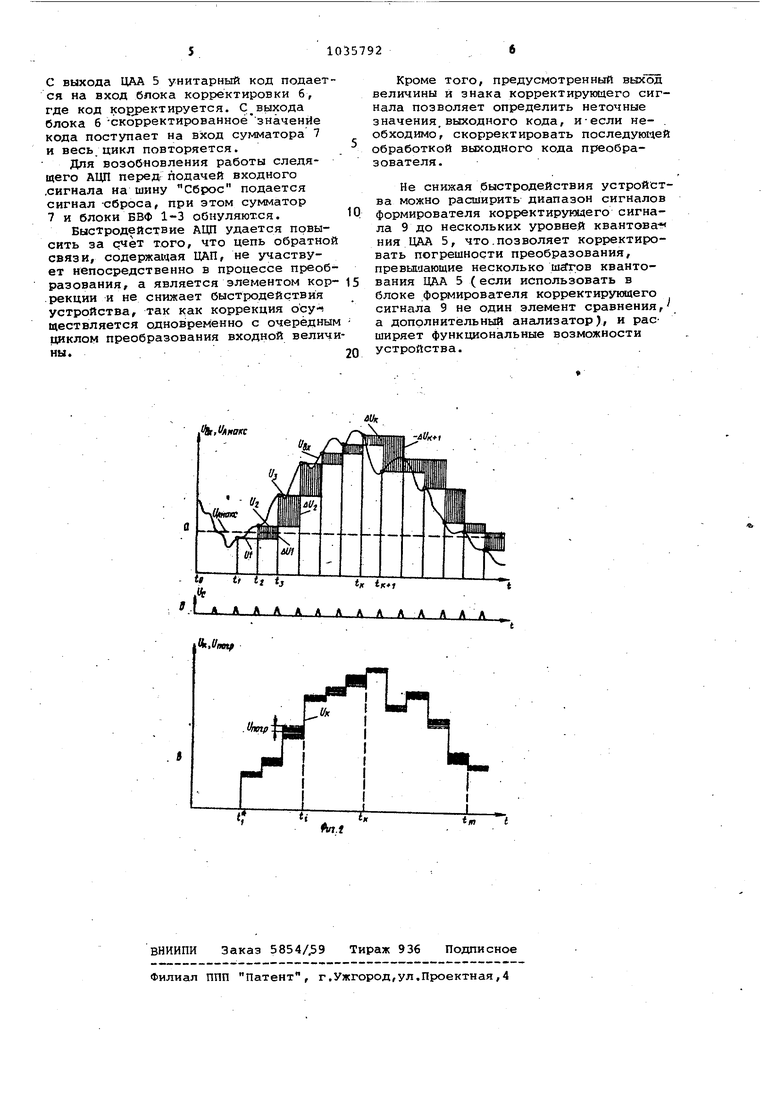

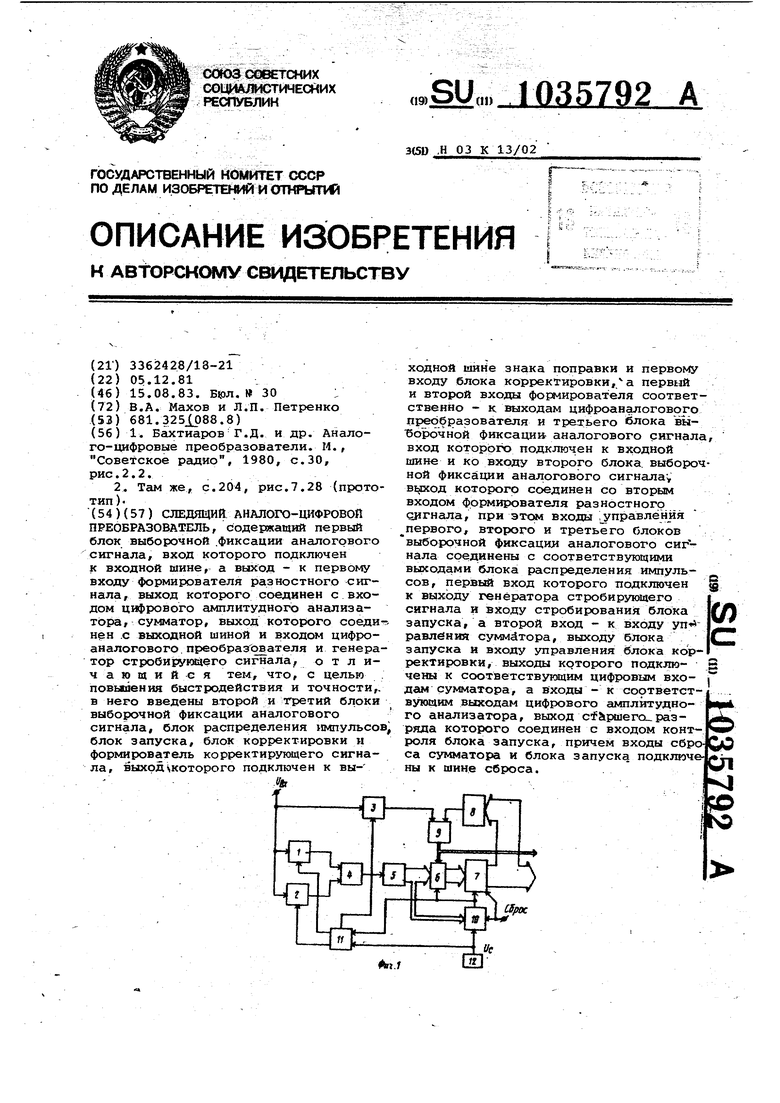

Изобретение относится к вычислительной технике и может быть использовано для преобразования мгновенного значения сигнала в цифровой код В следящем режиме. Известен аналого-цифровой преобра эователь (АЦП) последовательньк приб лижений, содержащий цифроаналоговый преобразователь (ПДП), источник опорного напряжения, генератор тактовых .импульсов, программное устройство уп равления и компаратор, в основе работ которого лежит принцип дихотомии ll Недостатком данного преобразобателя является сравнительно низкое быстродействие. Известен также АЦП с обратной свявью, содержащий устройство выборочной фиксации аналогового сигнала, выход которого подключен последовательно через первый вход формирователя разностного сигнала, малоразрядный циф.ровой амплитудньй анализатор { ДАЛ) , арифметический блок и ДАН ко второму ВХОДУ формирователя разностного сигна ла С 2 .. . Недостатками известного преобразователя являются ограниченные быстро действие и точность из-за наличия в цепи обратной связи арифметического блока и ЦАП, Кроме того, отсутствие элементов коррекции приводит к тому, что при неправильном срабатывании компараторов в случае попаДания сигнала в зону небороделенности происходит ошибочное преобразование сигнала, скорректировать которое мокно лишь повторным преобразованием входной величины, т.е. ценой потери быстродействия. Цель изобретения - повышение быст родействия и точности. Поставленная цель достигается тем что в следотций А1Щ, содержащий пер-г вый блок выборочной фиксации аналого вого сигнала, вход которого подключен к входной шине, а выход - к первому входу формирователя разностного сигнала, выход которого соединен с входом цифрового амплитудного анализатора, сумматор, выход которого сое динен с выходной шиной и входом ЦАП, и генератор стробирующего сигнала, введены второй и третий блоки выборо ной, фиксации аналогового сигнала, блок распределения импульсов, блок запуска, блок корректировки и формирователь корректирующего сигнала, выход которого подключен к выходной шине знака поправки и первому входу блока 1{оррек11Г,и1ювки, а первый и второй входы формирователя соответствен но - к выходам ЦАП и. третьего блока выборочной фиксации аналогового сигнала, вход которого подключен к выхо .ной шине ико входу второго блока вы бдрочной фиксации аналогового сигнала, выход которого соединен со вторым входом формирователя разностного сигнала, при этом входы управле-. ния первого/ второго и третьего блоков выборочной фиксации аналогового сигнала соединены с соответствующими выходами блока распределения импульсов, первый вход которого подключен к выходу генератора стробирующего. , сигнала и входу стробирования :блока1 запуска, а второй вход - к входу управления сумматора, выходу блока за- пуска и входу управления блока корректировки, выходы которого подключены к соответствующим цифровьам входам сумматора, а входы - к соответствунядим выходам ЦАА,выход старше гюразряда которого соединен с входом контроля блока запуска, причем входы сброса сумматора и блока запуска подключены к шине сброса. , На фиг.1 приведена структурная элегстрическая схема следящего АЦП, на фиг.Та - временные диагратфол входного сигналаOgjjiHa фиг.26 - импульсы стробирования генератора стробирующего сигнала; на фиг.2ввременные диаграммы компенсирующего сигнала UK. и величины погрешности погР Р о Рззования. Следящий АЦП содержит первый, второй и третий блоки выборочной фиксации аналогового сигнала(БВФ) 1-3 с входами управления, формирователь разностного сигнала 4 с и втоЕЖЛм входами, ЦАА 5 блок корректировки 6 с двумя входами управления, сумматор 7 с цифровым входом, входами управления и сброса,ЦАП 8, формирователь корректирующего сигна|ла 9, блок запуска 10 с входами контроля, стробирования и сброса, блок распределения импульсов 11 с двумя входами и тремя выходами и генератор 12 стробирующих сигналов. Работа следящего I АЦП заключаемся в следующем. В исходном состоянии сумматор 7 и БВФ 1-3 ббнулены. Импульсы стробирования ог блока распределения импульсов . поступают только на вход БВФ 1. На входы БВФ 2 и 3 импульсы не поступают, и они находятся в состоянии хранения нулевого уровня сигнала. При подаче сигнала по шине C6pqc, на вход сброса блока запуска 10 и вход сброса сумматора 7, последний обнуляется, а блок запуска 10 переходит в ждущий режим. БВФ 1, на вход которого поступают импульсы стробирования с периодом Т, запоминает в моменты прихода импульсов стробирования уровня входного сирнал а. Сигналы с выходов БВФ 1 и 2 поступают соответственно на первый и второй входы формирователя разностного сигнала 4, где формируется сигнал, равный величине запомненного в БВФ 1 уровня входного сигнала. Сигнал с выхода формирователя разносного сигнала 4 поступает на вход ЦАА 5. Если входной сигнал превышает .величин1гид),{фиг. 2а), равную максимальной измеряемого ЦАА 5 напряжения, то ЦАА 5 выдает унитарный код, состоящий из одних единиц Часть кода, соответствующая старшим разрядам, поступает на вход контроля блока запуска 10 Пока поступающая часть кода состоит из единиц /блок запуска 10 продолжает находиться в режиме ожидания, иуправл ровдий сигна на суммированиЬ с егЬ вькода не поступает на вход управления cyNayaTopai 7, При этом управляющий сигнал также поступает на второй вход блока распределения, импульсов 11. Блок расг ределения импульсов 11 стробируюдие сигналы на входы УВФ 2 и 3 н0 вы дает... :: . . -. : : . . . ;. Пусть в момент времени t входной Сигнал Ору стал ло актлитуде меньше некоторпо заранее установленнуи величину/ равную нескольким у ровНИМ квантования ЦАА 5. Разряды унитарного кода, соответствующие этим яонтрольн№1 уровням ЦАА 5 и поступгиощие на х5од ксн;гроля блока запуска 10, изме11яют свои состояния со 1 на значение О, что означает факт вхождения сигнала , в .диапазон ЦАА 5.- Как только сигнал вошёл в диапазон ЦАА 5у блок запуска Id выдает сигнал на вход управления сумматора 7 на начало с5 1МирЬван1ш и На второй вход блока распределения импульсов 11 на начало стробирован я БВФ 2 и 3, после чего он вы- ходит из режима ожидания. Унитарный код через блок корректировки 6 поступает. на вход сумматора 7, где предобра зуетсяй двоичный код, суммируется с хранящимся в cyNMaTope 7 текущ 1м значением кода, а результат сумяи рования поступает на вход-ЦАП 8 и на Выход ует1юйства. После прихода управЛяскщего сигнала с выхода блока запуска 10 на:второй вход блока расПред€(ленйя импульсов 11, последний выдает сигналы стробй хэвания на все три БВФ, причем последователь ность Импульсов, поступающая на БВФ 1 теперь имеет период.следования импульсов 2Т ВВФ 2 также стробируется с периодом 2Т, но последовательность импульсов, поступакмцая на строби1юва,ние БВФ 2 сдвинута относительно после:довательнос.ти импульсов, стробирующих БВФ 1 на величину периода Т. На БВФ 3 подается последовательность стро0ирующих импульсов с периоде Т.

Таким образом, начиная с момента 4а.стробируются все три БВФ. В момент времени ; в БВФ 1 продолжает храниться уровень U соответствующий моменту -Ьц , а БВФ 2 и 3 запоминают в момент -tg. уровень 0 .

Формирователь разностного сигнала 4 формирует разность Д Ц eUij-U-(, которая поступает на вход ЦАА 5, Унитарный код через блок.корректировки 6 поступает на вход сумматора 7, где преобразуется в двоичный код и суммируется с текущим значением кода сумматора 7. Новое значение кода поступает с выходс1 cyfwaTppa 7 на вход ЦАП 8 и на вход устройства, В умматоре 7 происходит процесс суммирования цифровых эквивалентов приргодения сигнала за время Т. Приращение измеряется с погрешностью, равной шагу квантования ЦАА 5. При суммировании приращений сумматором 7, суммарный цифровой эквивалент сигнала будет отличаться от текущего значе ниясигнала Орх величину Unort (фиг.2в) значение которой может лревышать шаг квантования,ЦАА 5. Чтобы снизить смаибку преобразования до величины, не прешлясцоцей. шага квантования ЦАА 5 производится кор1 ектировка цифрового эквивалента сигнала, накапливаемого в сумматоре БВф 3 в MtwieHT -Ь запсниинает уровень t

Сшгнал с шлхода БВФ 3 поступает на вход Фор1«ирователя корректирующ1е.гО сигнала 9, на второй вход которого поступает сигнал с выхода ЦАП 8 соответствующий накопленному цифровому эквиваленту входного, сигнала к моменту сравю1вания -fc (фиг. 2в). В формирователе корр9ктир чэдего сигнсша 9 сранн иваются величины э тих сигн алов. Если уровень вхрдно г.Осигнала меньше уровня ЦАП 8 0олее чем на величину шага квантования ЦАА 5, то, формирователь корректирующего сигнал 9 ВБщает сигнал на минусовую коррекцию кода. Этот сигнал подается на выход и одновременно на пе{жый вход блока корректировки 6, где унита1рный ;код, соответствующий приращению сигнала в последующий момент Ь-|4.4 бУДет уменьшен Hgi единицу При превыаении уровня БВФ 3 над уровнем ЦАП 8 более чём на величну idara квантования ЦАА 5, формирователь корректирующего сигнала 9 выдает сигнал на плюсовую коррекцию кода, и унитарный код, соответствующий приращению сюгнгша в последующий BpejteHHfe ij будет увеличен на единицу.,

В момент времени-Ьзстробируйтся БВФ 1и 3, где фиксируется уровень ОзНа первый вход формирователя разностного сигнала 4 подается уровень сигнала U- с выхода БВО 1, на второй, вход - уровень с выхода БВО 2. С выхода формирователя разностного сигнала 4 вновь сфо ированная рлзность AUa-lJ-i-lb. I соответствующая моменту tj, подается на вход ЦАА 5.

С выхода ЦАА 5 унитарный код подается на вход блока корректировки 6, где код коЕректируется. С,выхода блока б -скорректированное значение кода поступает на вход сумматора 7 и весь цикл повторяется..

Для возобновления работы следящего АЦП перед подачей входного сигнала на шину Сброс подается сигнал -сброса, при этом сумматор 7 и блоки БВФ 1-3 обнуляются.

Быстродействие АЦП удается повысить за счет того, что цепь обратной связи содержащая ЦАП, не участвует непосредственно в процессе преобр1зова2ия, а является элементом коррекции и не снижает быстродействия ст ойства, так как коррекция осу- шесйляется одновременно с очередным преобразования входной величины.

Кроме того, предусмотренный выход величины и знака корректирующего сигнала позволяет определить неточные значения выходного кода, и-если необходимо, скорректировать последующей обработкой выходного кода преобразователя.

Не снижая быстродействия устройства можно расширить диапазон сигналов формирователя корректирующего сигнала 9 до нескольких уроввей квантования ЦАА 5, что.позволяет корректировать погрешности преобразования, превыгаающие несколько шйгрв квантования ЦАА 5 (если использовать в блоке формирователя корректирующего сигнала 9 не один элемент сравнения, а дополнительный анализатор), и расширяет функциональные возможности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1538143A2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1596270A2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

%,%w«

О

ЛААЛ.АЛАААЛЛАА

.

T

ti

fui.t

--j«

in

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бахтиаров Г.Д | |||

| и др | |||

| Аналого-цифровые преобразователи | |||

| М., Советское радио, 1980, с.30, рис.2.2 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с.204, рис.7.28 (прототип) | |||

Авторы

Даты

1983-08-15—Публикация

1981-12-05—Подача