Изобретение относится к вычислительной технике и может использоваться как системное устройство для связи цифровых вычислительных машин (ЦВМ) в многомашинном вычислительном комплексе.

Цель изобретения - повьшение быстродействия устройства.

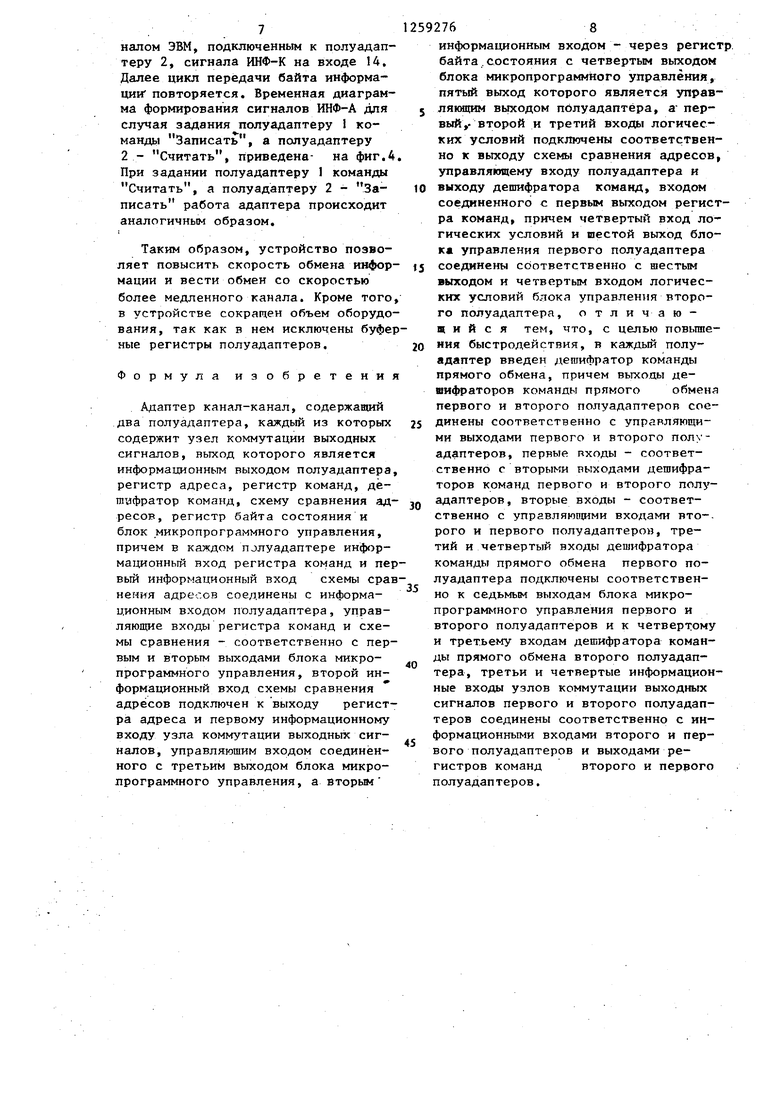

На фиг. 1 приведена блок-схема адаптера; на фиг. 2 - функциональная схема дешифратора команды прямо- ro обмена; на фиг. 3 - блок-схема блока управления; на фиг. А - временная диаграмма работы дешифратора управления прямьм обменом при обмене одним байтом информации; на фиг, 5 -- алгоритм работы блока управления.

Адаптер канал-канал состоит из двух полуадаптеров и 2, казкдый из которых содержит регистр 3 команд, дешифратор 4 команды, регистр 5 адресов, схему 6 сравнения адресов, блок 7 управления, узел 8 коммутации выходных сигналов, регистр 9 байта состояния и дешифратор 10 команды прямого обмена. Адаптер связан с сопрягаемыми каналами ввода- вывода с помощью информационных входов (линии каналов) 1 и 12 полуадаптеров I и 2, управляющих входов (линии каналов) 13 и 1А полуадаптеров. 1 и 2, управляющих выходов vли- нии абонентов) 15 и 16 полуадаптеров 1 и 2, информационных выходов (линии абонентов) 17 и 18 полуадаптеров и 2. Деппгфратор 10 (фиг.2) состоит из элементов ИЛИ 19, НЕ 20, элементов И 21 и 22 и ИЛИ 23.

Блок управления (фиг. З) представляет собой синхронный цифровой автомат, состоящий,например, из мультиплексора 2А входных сигналов, генератора 25 синхроимпульсов, регистра 26 адреса микрокоманды и постоянного запоминающего устройства 27, и вырабатьгоает функциональные сигналы, обеспечивающие работу адапте- ра в соответствии с заложенным алгоритмом и входными сигналами, поступающими с выхода дешифратора 4 команд, схемы 6 сравнения адресов, блока 7 управления другого полуадаптера и управляющими сигналами канала.

На фиг. 1-3 показаны также линии 28-31 связей между дешифратором 10 и другими узлами полуадаптеров.

5

0

Микрокоманда, под управлением которой происходит работа каждого из полуадаптеррв 1 и 2, состоит из следующих полей,

Поле номера информационного сигнала - ПНИС. Под управлением этого по ля проходит выдача того или иного информационного сигнала на выход мультиплексора 24. Сигнал с выхода мультиплексора 24 используется для организации ветвлений (условных переходов) в микропрограмме.

Поле управления способом ветвления в микропрограмме - ПУСВ. Под управлением этого поля определяется способ задания адреса следующей микрокоманды в регистре 26.

Поле маскирования прерывания пмп.

Поле.адреса - ПА. Это поле используется для задания адреса перехода и применяется для организации ветвлений в микропрограмме.

Поле константы управления - ПКУ,

5 Это поле задает функциональные сигналы, обеспечивающие работу адаптера в соответствии с заложенным алгоритмом.

Микропрограмма, выполняемая бло0 ком 7 управления, может быть прервана, при этом в регистр 26 адреса микрокоманды заносится константа, представляющая собой начальный адрес микропрограммы обработки пре- рьшания. Каждой причине прерывания соответствует своя константа. Прерывание может возникнуть при задании каналом ЭВМ последовательности сигналов: Сброс системы, СелективQ ный .сброс, Отключение от интерфей5

са . Прерывание может быть замаскировано путем установки разряда поля маскирования прерывания.

5 Устройство работает следующим образом.

При наличии одного из сигналов Разрешение прямого обмена (РПО) из блока 7 одного из полуадаптеров,

0 например полуадаптера 1 (сигналы РП01 или РП02), наличии одного из сигналов Записать (ЗП) или тать (СЧ) на выходе дешифратора 4 и отсутствии (наличии) сигнала

5 ИНФ-К на входе 12 полуадаптера 2 на выходе элемента ИЛИ 23 вырабатывается, сигнал ИНФ-А, поступающий далее на выход 15.

3

Адаптер распшфровывает и выполняет следующие команды канала: Считать., Считать в обратном направлении, Записать, Управление фиктивное, Управление рабочее, Уто нить состояние, Проверить ввод- вывод.

Некоторые команды, посылаемые каналом в адаптер, вьшолняются только в том случае, если другой канал, с которым связан адаптер, посьшает соответствующую команду. Например, команды Считать или Считать в обра ном направлении, посылаемые одним каналом, могут быть выполнены адаптером только после того, как другим каналом будет послана в адаптер команда Записать, и наоборот. Адаптер указывает свое состояние каналу используя четыре бита байта состояния: нулевой - указатель Внимание третий - указатель - Занято, четвертый - указатель Канал кончил, пятый - указатель ВУ кончило,

Эти указатели обозначают: Внимание - операция, требующая соответствующего ответа от канала, уже начатая другим каналом: Занято -адаптер не может выполнить команду; Канал кончил - адаптер может быть логически отключен от канала; ВУ кончило. - операция, выполняемая каналом, завершена в адаптере.

Чтобы задать адаптеру какую-либо команду, канал вводит последовательность сигналов начальной выборки, которая начинается для адаптера с получением, например, полуадаптером 1 по входу 3 сигнала АДР-К и по входу 11 адреса устройства, для которого предназначена операция ввода-вывода. Полученный адрес устройства поступает на вход схемы 6, где он сравнивается с адресом полуадаптера 1, хранящимся в регистре 5. Если эти адреса равны, то схема 6 формирует сигнал Адрес опознан поступающий в блок 7, Затем ка,нал выдает сигналы Разрешение выборки и Выборка (РВБ-К и ВБР-К) , поступаг- ющие по входу 13 в блок 7, который, если адрес бьт опознан полуадаптером 1, блокирует дальнейшее распространение сигнала ВБР-К, выдаёт сигнал РАБ-А на вход 15, формирует сигнал блокировки начальной выборки другим каналом полуадаптера 2. Назначение этой блокировки - запретить этому каналу поместить код команды

592764

в регистр 3 полуадаптера 2 при выполнении команд Записать, Считать, Управление рабочее. После снятия каналом сигнала АДР-К с входа - 13 блок 7 разрешает выдачу с выхода регистра 5 через узел 8 на выход 17 адреса полуадаптера 1 и формирует сигнал АДР-А на выходе 15. В ответ на сигнал АДР-А канал выдает сигнал

,Q УПР-К, поступающий по входу 13 в блок 7, и помещает на входе 11 код команды. Блок 7 разрешает занесение кода команды с входа 11 в регистр 3, в результанте чего принятая команда

J5 дешифрируется дешифратором 4, сбрасывает сигнал АДР-А на выходе 15, Затем блок 7 формирует байт состояния в регистре 9 в зависимости от условий, сложившихся в адаптере, и

20 присланной команды. После сформирования байта состояния в регистре 9 блок 7 разрешает выдачу информации из регистра 9 через узел 8 на выход 16, выдает сигнал УПР-А на

25 выход 15,

Получив сигнал УПР-А и байт состояния, канал выдает сигнал ИНФ-К, завершая тем самым последовательность сигнг лов начальной выборки. Сигнал ИНФ-.К поступает по входу 13 в блох 7, в результате чего послед- НИИ сбрасывает сигнал УПР-А на выходе 15, если полуадаптеру 1 задана одна из команд Записать, Считать, Считать в обратном направле- НИИ или уточнить состояние, или сбрасывает сигналы РАБ-А и УПР-А на выходе 15, если полуадаптеру 1 была задана любая другая команда, сбрасывает сигнал блокировки начальной выборки полуадаптера 2, запрещает выдачу информации через узел 8, сбрасывает регистр 9. Кроме того, если полуадаптеру 1 задана команда Записать, Считать, Считать в обратном направлении, Управление рабочее, то блок 7 формирует сигнал Ожидание согласования, выдаваемый в блок 7 полуадаптера 2, в результате чего формируется запрос на передачу байта состояния в канал , к которому подключен полуадап тер 2, и вводится последовательность сигналов подключения к каналу по требованию абонента, выполняемая следующим образом. Получив, сигнал Ожидание согласования, блок 7 полуадаптера 2 организует выдачу сигнала ТРБ-А на пыход 16, Затем

30

0

5

0

S

при получении сигнала ВБР-К по входу 14 блок 7 снимает сигнал ТРБ-А на выходе 6, выставляет на нем сигналы РАК-А, AJIP-A, разрешает выдачу информации (адреса) с выхода регистра 5 через узел 8 на выход 18.

Получив от канала сигнал УПР-К по входу 14,. блок 7 сбрасывает сигнал АДР-А на выходе 16, запрещает прохождение информации с выхода регистра 5 через узел 8 на выход 18, формирует в регистре 9 указатель Внимание. После сброса каналом сигнала УПР-К на входе 4 блок 7 разрешает въщячу сформированной в регистре 9 информации с выхода этого регистра через узел 8 на выход 18 и формирует сигнал УПР-А, выдава- на выход 16, При получении по входу 14 сигнала ИНФ-К блок 7 запрещает выдачу информации через узел 8, сбрасывает сигналы РАБ-А и УПР-А на вькоде 16. На этом полуадаптер 2 заканчивает выполнение последовательности сигналов подключения к каналу по требованию абонента.

ЭВМ, получив от полуадаптера 2 байт состояния с указателем Внимание, задает полуадаптеру 2 команду Уточнить состояние с целью определения кода команды, заданной другой ЭВМ полуадаптеру 1. Задание команды происходит путем введения каналом, подключенньм к полуадаптеру 2, последовательности начальной выборки, которая тзыполняется полу эдаптером

2аналогично выполнению последовательности начальной выборки полуадаптером 1, за исключением того, что полуадаптер 2 отключается от канала не с выдачей своего начального байта состояния, а после передач в канал байта информации, содержаще код команды, заданной полуадаптеру и выдачи в канал байта состояния с указателями Канал кончил и ВУ кочило. В этом случае полуадаптер 2 работает следующим образом.

Пос-пе выдачи начального байта состояния в канал блок 7 разрешает выдачу информации с выхода регистра

3полуадаптера 1 через узел 8 на выход 17 и организует выдачу на выход 15 сигнала ИНФ-А. Затем, получив по входу 13 сигнал , означающий, что байт информации принят каналом, блок 7 запрещает выдачу информации через узел 8 на выход 17 и снимает сигнал ИНФ-А на выходе 15. После эт5

92766

го. канал снимает сигнал ИНФ-К (или УПР-К) на входе 13, в результате чего блок 7 формирует в регистре 9 байт состояния с указателями Канал кончил и ВУ кончило, разрешает выдачу информации с выхода регистра 9-через узел 8 на выход 17 и организует выдачу сигнала УПР-А на выход 15 Затем, получив от канала по

Q входу 13 сигнал ИНФ-К, блок 7 запрещает выдачу информации через узел 8 на выход 17 и снимает сигналы РАБ-А и УПР-А на выходе 5, завершая тем самым выполнение команды.

Получив код команды, заданной полуадаптеру 1, другая ЭВМ может определить, какую команду ей следует задать полуадаптеру 2 для организации обмена информации Такой командой

0 должна быть команда Записать, если полуадаптеру 1 задана команда Считать, и команда Считать, если полуадаптеру 1 задана команда Записать.

5 Задание каналом полуадаптеру 2 команды Записать или Считать и выполнение этой команды полуадаптером 2 происходит аналогично заданию и выполнению этих команд полуадаптеQ ром I, за исключением того, что вместо сигнала Ожидание согласования блок 7 формирует сигнал Разрешение прямого обмена, поступающий на дешифраторы 10 обоих полуадаптеров. При этом дешифратор 10 полуадаптера , которому была задана, например, команда Записать, при отсутствии сигнала ИНФ-К на управляющих линиях 14 канала полуадаптера 2, которому

-j была задана, например, команда Считать формирует сигнал ИНФ-А на выходе 15, в ответ на который канал ЭВМ, подключенный к этому полуадаптеру, помещает на вход 11 байт ин формации и выдает на вход 13 сигнал ИНФ-К. Байт информации с входа 11 поступает через узел 8 полуадаптера 2 на выход 16. Дешифратор 10 полуадаптера 2 формирует сигнал ИНФ-А, поступающий на выход 16. Получив сигнал ИНФ-А и байт информации, канал ЭВМ, подключенный к полуадапте- ру 2, выдает сигнал ИНФ-К на вход 14, что приводит к сбросу сигнала ИНФ-А на выходе 15, сбросу каналом ЭВМ, подключенным к полуадаптеру 1, сигнала ИНФ-К на входе.13, сбросу дешифратором 10 полуадаптера 2 сигнала ИНФ-А на выходе 16 и сбросу ка5

0

5

налом ЭВМ, подключенным к полуадаптеру 2, сигнала ИНФ-К на входе 14. Далее цикл передачи байта информации повторяется. Временная диаграмма формирования сигналов ИНФ-А для случая задания полуадаптеру 1 ко- мандь Записать, а полуадаптеру 2 - Считать, приведена- на фиг.4 При задании полуадаптеру 1 команды Считать, а полуадаптеру 2 - Записать работа адаптера происходит аналогичным образом.

Таким образом, устройство позволяет повысить скорость обмена информации и вести обмен со скоростью более медленного канала. Кроме того в устройстве сокращен объем оборудования, так как в нем исключены буферные регистры полуадаптеров.

Формула изобретения

Адаптер канал-канал, содержандай два полуадаптера, каждый из которых содержит узел коммутации выходных сигналов, выход которого является информационным выходом полуадаптера регистр адреса, регистр команд, дё- гауфратор команд, схему сравнения адресов, регистр байта состояния и блок микропрограммного управления, причем в каждом полуадаптере информационный вход регистра команд и первый информационный вход схемы сравнения адресов соединены с информационным входом полуадаптера, управляющие входы регистра команд и схемы сравнения - соответственно с первым и вторым выходами блока микропрограммного управления, второй информационный вход схемы сравнения адресов подключен к выходу регистра адреса и первому информационному входу узла коммутации выходных сигналов, управляющим входом соединённого с третьим выходом блока микропрограммного управления, а вторым

2592768

информационным входом - через регистр байта.состояния с четвертым выходом блока микропрограммного управлени;я, пятый выход которого является управ- J ляющим вьрсодом полуадаптёра, а первый,- второй и третий входы логических условий подключены соответственно к выходу схемы сравнения адресов, управляющеьгу входу полуадаптера и 10 выходу дешифратора команд, входом соединенного с первым выходом регистра команд, причем четвертый вход логических условий и шестой выход блока управления первого полуадаптера (3 соединены соответственно с шестым выходом и четвертым входом логических условий блока управления второго полуадаптера, отличающийся тем, что, с целью повыше- 20 ния быстродействия, в каждый полуадаптер введен дешифратор команды прямого обмена, причем выходы дешифраторов команды прямого обмена первого и второго полуадаптеров сое- 25 динены соответственно с управляющими выходами первого и второго полу - адаптеров, первые входы - соответственно с вторыми выходами дешифраторов команд первого и второго полу- ,- адаптеров, вторые входы - соответственно с управляюпщми входами вто-. рого и первого полуадаптеров, третий и четвертый входы дешифратора команды прямого обмена первого полуадаптера подключены соответственно к седьмьм выходам блока микропрограммного управления первого и второго полуадаптеров и к четвертому и третьему входам дешифратора команды прямого обмена второго полуадаптера, третьи и четвертые информационные входы узлов коммутации выходных сигналов первого и второго полуадаптеров соединены соответственно с информационными входами второго и первого полуадаптеров и выходами регистров команд второго и первого полуадаптеров.

5

0

5

«

16

30

13

tS

30

IS

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1987 |

|

SU1425694A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Многоканальный адаптер | 1987 |

|

SU1495806A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

Изобретение относится к области вычислительной техники- и может быть использовано как системное устройство для связи цифровых вычислительных маптн в многомашинном вычислительном комплексе. Целью изобретения является повышение быстродействия устройства. Это достигается тем, что в адаптер,. содержащий два идентичных полуадаптера, каждый из которых включает узел коммутации входных сигналов, регистр команд, дешифратор команд регистр адреса, схему сравнения адресов, блок управления, узел выходных сигналов, регистр байта состояния, в каждый полуадаптер введен дешифратор команды прямого обмена. 5 ил. Ю м Ьд

Hnip-лг

I ttMtjadanmta ИЛ1ЖИЛЙ7 записать)

Пол11аЯаптср 2 ((ко/намЗо считать)

Hen

Редактор Н.Яцола

Составитель В.Вертлиб

Техред И.Попович Корректор Л.Пилипенко

Заказ 5123/47 Тираж 671 .Подписное

ВНИИПИ Государственного комитету СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое пре шриятне, г. Ужгород, ул. Проектная, 4

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское, свидетельство СССР № 1144114, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-30—Подача