ми блока согласования сигналов, третий, четвертый, чтый и шестой выходы которого соединены соответственно с первыми и вторыми управляющими входами первого эталонного и контролируемого интерфейсов, первый управляющий выход первого эталонного интерфейса соединен с третьим входом блока согласования сигналов и первым входом блока сравнения, второй управляющий выход первого эталонного интерфейса соединен с четвертым входом блока согласования сигналов и вторым входом блока сравнения, третий и четвертый входы которого соединены с первым и втЬрым управляющими выходами контролируемого интерфейса соответственно, выход блока сравнения соединен с входом блока индикации, установочный вход счетчика адреса и второй вход блока сравнения образуют вход пуска устройства, и.нформацион ные входы узла памяти являются входом ввода информации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1984 |

|

SU1264182A2 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАЛЛЕЛЫШХ МИКРОПРОЦЕССОРНЫХ ИНТЕРФЕЙСОВ, содержащее блок сравнени) первый эталонный интерфейс, блок индикации, блок управления, включаю- . щий в себя узел памяти, узел индикации, регистр управлякидах сигналов, регистр .данных, счетчик адреса, два регистра адреса, узел сравнения, злемент ИЛИ,, элемент запрета, генератор тактовых импульсов, причем первый и второй выходы генератора тактовых импульсов соединены с управляющими входами соответственно регистру управлякхшх сигналов и регистра дан1ШХ, информационные входы которых соединены с вЪкодами узла памяти адресные входы которого соединеш с выходгши счетчика адреса, входги од узла индикации и первой группой входов узла сравнения, вторая группа входов котброго соединена с выхоДа- ми первого регистра адреса, выход узла сравнения соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом блока сравнения, третий выход генератора тактовых импульсов соединен с первым входом элемента запрета, второй выход которого соединен с выходом элемента ИЛИ, выход элемента запрета соединен со счетным входом счетчика адреса, группа информационных входов которого соединена.с выходами второго регистра адреса, четвертый выход генератс1(ра тактовых импуль- . сов соединен с первым входом блока сравнения,- отличающееся тем, что, с целью повышения быст- юдейютвия, в него введены второй эталонный интерфейс, два коммутатора и блок согласования сигналов, причем первая группа выходов регистра правляющих сигналов соединена с группами управлякащх входов цервого коммутатора, первого эталонного и контролируемого интерфейсов, вторая группа выходов регистра управляющих сигналов соединена с групс S пами управляющих входов второго эталонного интерфейса и второго (Л коммутатора, первая и вторая группы входов которого соединены с первой с группой входов-вЕлходов .второго эталонного интерфейса, вторая группа входов-выходов которого соединена с первой и второй группами входов первого коммутатора и выходами регистра данных, первая и вторая группы входов блока сравнения соединень соответственно с первой и второй группами выходов первого коммутатора, первая и вторая группы входов4 выходов которого соединены с первыми ЭО группами входов-выходов первого эталонного и контролируемого интерфей:о сов соответственно, третья и четвертая группы входов блока сравнения/ соединены соответственно с первой и второй группами выходов второго коммутатора, первая и вторая группы входов-выходов которого соединены с вторыми группами входов-выходов первого эталонного и контролируемого интерфейсов соответственно, первый и второй управляющие входы и Ь0рвый и второй управляквдие выходы второго эталонного интерфейса соединены соответственно с первым и вторь выходами и первым и вторым входа

Изобретение относится к цифровой вычислительной технике, в частности к средствам автоматизации контроля и поиска неисправности в устройствах с дискретным характером функционирования, например в параллельных микропроцессорных интерфейсах.

Известно устройство, содержащее генератор импульсов, счетчик, контролируемлй и эталонный объекты, блок индикации и блок сравнения l .

Недостатком данного устройства является низкая помехоустойчивость, так как сравнение информации нестробировано, отсутствие возможности контроля двунаправленных шин и невозможность контроля объектов с временной расстановкой входных сигналов

Наиболее близким по технической сущности к предлагаемому является j устройство для автоматического контроля больших интегральных схем, содержащее блок памяти, блок управления, блок сравнения, блок индикации, генератор тестов, блок формирования входных сигналов, два блока перекодировки данных, дешифратор, блок селектора адреса, эталонный и контролируемый объекты, причем выходы блока формирования входных сигнсшов соединены с входами дешифратора, лока селектора адреса, этсшонного и контролируемого объекта, блоками перекодировки данных, В 1ходы которых соединены с входами блока сравнения, выход которого соединен с входом блока управления, первая и вторая группы входов которого соединены соответственно с выходами дешифратора и первой группой выходов блока памяти, вторая, третья и четвертая группы выходов которого соединены с первыми группами входов блока Индикации, генератора тестов и блока, формирования входных сигиалов, выходы блока управления соединены с блоком индикации, блоком памяти, генератором

тестов, блоком .селектора адреса, блоком формирования входных сигналов. Входы-выходы блока управления соединены с входами-выходами блока сравнения f2 .

Недостаток известного устройстваотсутствие возможности вести диалоговый обмен сигналами с эталонным и контролируемым объектами.

Схема интерфейса, например

типа Intel 8255, требует подачи на его вход дополнительного сигнала Подтверждение записи (когда она работает в режиме передачи даннызс

после того,как эта схема выдаст сигнал Строб запис. Требуется вести диалог с эталонной схемой и в режиме приема ею информации (Строб приема Подтверждение приема).

Отсутствие диаологового обмена

между устройством и эталонной (контролируемой схекюй снижает достоверность контроля при значительном снижении быстродействия и увеличении объема памяти устройства.

Так, например, возможно увеличивать время между входными воздействиями (тестами), введя дополнитель ные сигналы управления (Подтверждение записи в режиме передачи и

Строб приема в режиме приема данных ), но это снизит достоверность контроля, так как проверка будет вестись не на реальных рабочих частотах, увеличится объем памяти, так

как после каждого теста необходимо извлекать, из памяти дополнительные сигналы управления, и, как следствие, увеличится время контроля.

К недостаткам известного устройства следует отнести также его низкие диагностические возможности: отсутствует возможность иксаДии неисправного входа (.выхода ) и теста, при котором указанная неисправность появляется.

Цель изобретения - повышение выстродествия.

Поставленная цель достигается тем, что в устройство для контроля параллельных икpoпpoцeccopныx интерфейсов, содержащее блок сравнения, первый эталонный интерфейс, блок индикации, блок управления, включающий в себя узел памяти, узел индикации/ регистр управляющих сигналов, ре-. : гистр данных, счетчик адреса, два . регистра адреса, узел сравнения, / элемент ИЛИ, элемент запрета, гене ратор тактовых импульсов, причем первый и второй выходы генератора тактовых импульсов соединены с управляющими входами соответстйенно регистра управляющих сигналов и регистра данных, информационные входы которых соединены с выходами узла памяти, адресные входы которого соединены с выходами счетчика адреса, входами узла индикации и первой . с группой входов узла сравнения, вторая группа входов которого соединена с выходами первого регистра адреса, выход узла сравнения соединён с первым входом элемента ИЛИ, второй вход которого соединён с выходом блока сравнения, третий выход генератора тактовых импульсов соединен с первым входом элемента запрета, второй вход которого соединен с вы-. ходом элемента ИЛИ, выход элемента запрета соединен со счетным входом счетчика адреса, группа информаци.онных входов которого соединена с выходами второго регистра адреса, четвертый выход генератора тактовых импульсов соединен с первым входом блока сравнения, введены второй этаонный интерфейс, два коммутатора и блок согласования сигналов, причём первая группа регистра управляющих сигналов соединена с группами управяющих входов первого коммутатора, первого эталонного и контролируемого интерфейсов, вторая группа выходов 1егистра управляющих сигналов, соединена с группами управляющих входов второго эталонного интерфейса и втоого коммутатора, первая и вторая группы входов которого соединены с первой группойч входов-выходов второго эталонного интерфейса, вторая ; группа входов-выходов которого сзодинена с первой и второй группами входов первого коммутатора и выходеши

егистра данных, первая и вторая группы входов блока сравнения содинены соответственно с первой-и второй группами выходов первого комутатора, первая и вторая группы ходов-выходов которого соединены с первыми группами входов-выходов ервого эталонного и контролируемого интерфейсов соответственно, треья и четвертая группы входов блока сравнения соединены соответственно с первой и второй группами выходов второго коь «утатора, первая и вторгш

группы входов-выходов которого соединены с вторыми группами входоввыходов первого эталонного и контролируемого интерфейсов соответственно, первый и второй управляющие .входы и первый и второй управляющие выходы второго эталонного интерфейса соединены соответственно с первым и вторым выходами и первым и вторьом входами блока согласования сигналов,

0 третий, четвертый, пятый и шестой выходы которого соединены соответственно с первыми и вторыми управляющими .входами первого, эталонного и контролируемого интерфейсов, первый управляющий выход первого эта- .

5 лонного интерфейса соединен с третьим входом блока согласования сигналов и первым входом блока сравнения, второй управляющий выход пер-, вого эталонного интерфейса соединен

0 с четвёртым входом блока согласования сигналов и вторым входом блока сравнения, третий и четвертый входы которого соединены с первым и вторым управляющими выходами конт5ролируемого интерфейса соответственно, выход блока сравнениясоединен с входом блока индикации, установочный вхсд счетчика ашреса и второй вход блока сравнения обраэгуют вход пуска устройства, информационные

0 входы узла памяти являются входом ввода информации устройства.

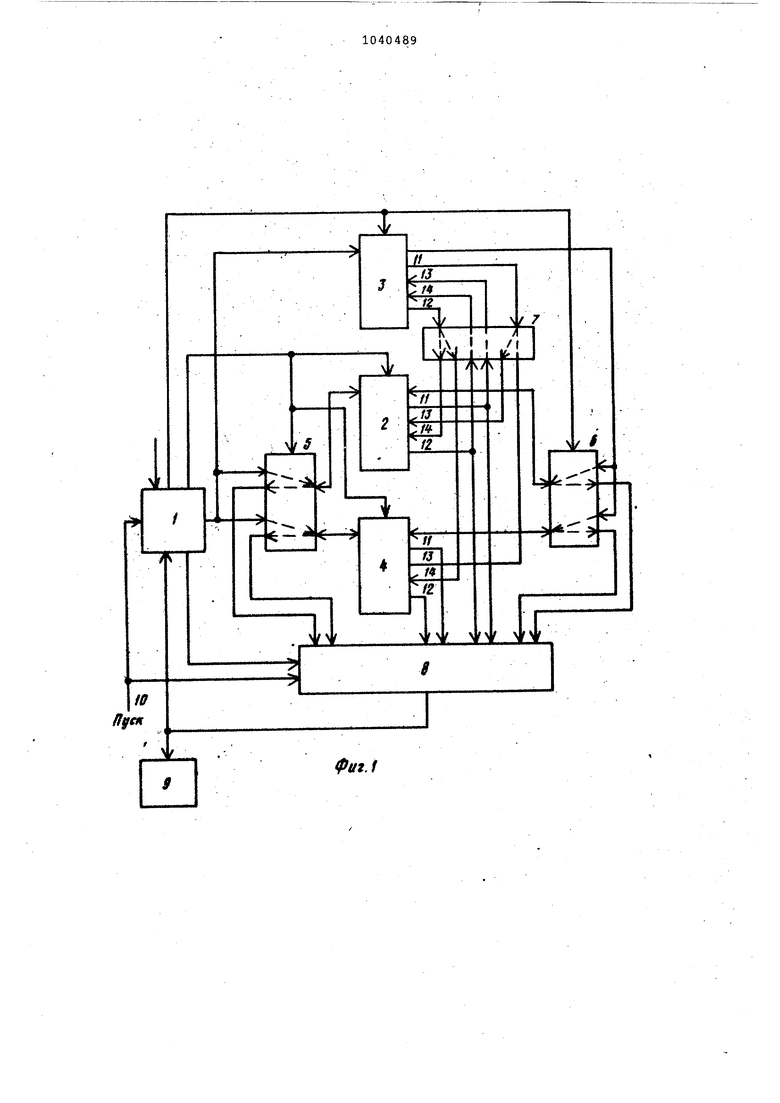

На фиг. 1 приведена структурная схема устройства для контроля параллельного микропроцессорного интер5фейса; на фиг. 2 - структурная схема блока управления; на фиг. 3 структурная схема блока сравнения.

На фиг. 1 изображены блок 1 управления, первый и второй эта.лонные

0 интерфейсы 2 и 3, контролируемый интерфейс 4, первый и второй коммутаторы 5 и 6, блок 7 согласования сигналов, блок 8 сравнения, ,блок 9 индикации, вход 10 пуска устройства,

5 первый и второй выходы 11, 12 эталонных и контролируемого интерфейсов 2-4, первый и второй входы 13 и 14 эталонных и контролируемого интерфейсов 2-4.

Блок 1 управления устанавливает

0 режим работы коммутаторо 5 и 6 эталонных и контролируемого интерфейсов 2-4 с помощью двух групп выходов регистра управляющих сигналов. Для эталонных и контролируемого ин5терфейсов это режимы приема или передачи информации. Первый коммутатор 5 служит для передачи информации из блока 1 управления на первый эталонный и контролируемый интер0фейсы 2 и 4 либо для передачи информации с этих интерфейсов на блок 8 сравнения. Второй коммутатор 6 служит для обмена информацией второго эталонного интерфейса 3 с первым

5 зтёшонным и контролируемым интерфейсами 2 и 4 для передачи информации с первого эталонного и КОНТРОЛИРУЕМОГО интерфейсов 2,4 на блок 8 сравнения. Блок 7 согласования сигналов служит для согласования управляющих сигналов эталонных и контролируемого интерфейсов 2-4. Он обеспечивает соединение управляющих входов и выходов 11-14 эталонных и контролируемых интерфейсов 2-4 таким образом, что один из эталонны интерфейсов работает в режиме передачи, адругой. - в режиме приема ин формации ,к

Управляющие выходы 11 и 12 первото эталонного и контролируемых интерфейсов 2 и 4 соединены с входами блока 8 сравнения, который осуществляет сравнение информационных и управляющих сигналов, поступающих с первого эталонного и контролируемого интерфейсов 2 и 4. Сравнение происходит по сигналам, поступающим из блока 1 управления. Результа сравнения отображается блоком 9 индикации и останавливает работу блока 1 управления.

. На фиг. 2 изображен регистр 15 управляющих сигналов, регистр 16 данных, первый и.второй регистры 17 и 18 адреса, узел 19 сравнения, узел 20 индикации, элемент ИЛИ 21, счетчик 22 адреса, узел 23 памяти, генератор 24 тактовых импульсов, элемент 25 запрета. Первый регистр 17 адреса служит для установки адреса конца тестовой программы, второй регистр 18 адреса служит для установки адреса начала тестовой программы (цепи установки кодов на регистры 17 и 18 адреса на фиг. 2 не изображены ), Узел 20 индикации служит для индикации адреса тестовой программы, на котором произошло несравнение. Элемент 25 запрета служит для останова тестовой программы по сигналу несравнения, поступающему с первого входа блока или по сигналу, поступа1рщему с выхода узла 19 сравнения.Регистр 15 и регистр 16 данных служит для передачи на соответствующие выходы блок управляюпШх и информационных сигналов. Информационные входы регистра 15 и регистра 16 данных соединены с выходами узла 23 памяти, адресные входы которого соединены -с выходами счетчика 22 адреса. Генератор 24 тактовых импульсов служит для формирования сигналов,, синхронизирующи работу регистра 15, регистра 16 данных, счетчика 22 адреса и блока 8 сравнения.

Блок 8 сравнения (фиг; 3i/ содер,жит узел 26 сравнения, регистр 27 ошибок, узел 28 индикации, элемент ИЛИ 29. Узел 26 сравнения осуществ.- ляет сравнение информационных и управляющих сигналов, поступающих с

первого эталонного и контролируемого интерфейсов 2 и 4 на его входы, являющиеся входами блока. Результат сравнения записывается на регистр 27 ошибок, с выходов которого через элемент ИЛИ 29 поступает на выход блока. Сравнение происходит по стробирующим сигналам, поступающим с первого вх.ода блока. Результат сравнения отображается узлом 28 индикации. Сброс регистра 27 ошибок осуществляется сигналом запуска устройства, поступающим со второго входа блока.

Устройство работает следующим образом.

Контролируемый интерфейс 4 проверяется в- двух режимах: в режиме передачи информации (вывод информации ) и режиме приема информации (ввод информации Каждому из двух режимов контроля предшествуют команды управления, поступающие с регистра 15 управляющих сигналов, которые подготавливают устройство к работе, т.е. уртанавЛивают блоки 2-6 в одног из двух состояний на прием или передачу данных. Причем, если первый эталонный и контролируемый интерфей. и 4 устанавливаются в состояние приема данных, то второй эталонный интерфейс 3 устанавливается в. состояние передач данных и наоборот.

Задача второго эталонного интерфейса 3 и его связи с контролируемым интерфейсом 4 и первым эталонным интерфейсом 2 - вести с ними . диалоговый обмен информацией и управляющими сигналами. Кроме того, второй эталонный интерфейс 3 является буфером блока 1 управления при проверке контролируемого интерфейса 4 в режиме приема (ввода)данных.

Связь первого эталонного и контролируемого интерфейсов 2 и 4 .с вторым эталонным интерфейсом 3 осуществляется через блок 7 согласования сигналов. Причем связь организована таким образом, что Строб записи,, который выдает первый эталонный интерфейс 2 по первому управляющему выходу 11 является Стробом приема для второго эталонного объекта 3 (первый управляющий вход 13), а сигнал Подтверждение приема который выдает второй эталонный интерфейс 3 по второму управляющему выходу 12 в ответ на сигнал Строб приема является сигналом Подтверждение записи (второй управляющий вход 14) для первого эталонного 2 и контролируемого 4 интерфейсов и наоборот. Строб записи, который формирует второй эталонный интерфейс 3 в соответствии с алгоритмом функционирования объекта при записи в него информации через первые дву направленные шины, является Стробо приема для первого эталонного и контролируемого интерфе.йсов 2 и 4, а сигнал Подтверждение приема, фо мируемый первым эталонным интерфейсом 2, является сигналом Подтверждение записи для второго эталонног го интерфейса 3. Таким образом, независимо от режима работы контролируемого интерфейса 4, блок 1 управления выдает последовательность тестов, а обмен информации (ее ввод и вывод) производится автоматически Когда первый эталонный и контрол руемый интерфейсы 2 и 4 работают в режиме передачи (вывода данных, тестовая комбинация поступает на них с регистра 16 через первый коммутатор 5 и далее после диалогово -. го обмена с вторым эталонным интерфейсом 3 через второй коммутатор 6 на блок 8 сравнения, В режиме приема (ввода ) данных входной тест поступает через второй эталонный интерфейс 3, второй коммутатор 6 на вторые группы входов выходов первого эталонного и конт-; ролируемого интерфейсов 2 и 4, а затем после диалогового обмена между эталонными интерфейсами 2 и 3 информация поступает через первый коммутатор 5 на блок 8 сравнения. В блоке 8 сравнения сравниваются также и выходные сигналы Строб записи .11 и Подтверждение приема 1 первого эталонного и контролируемого интерфейсов 2 и 4. В качестве коммутаторов 5 и б могут быть использованы логические схемы ИЛИ двунаправленных шинных формирователей типа К589АП16, К589АП26, которые имеют двунаправленные шины, шины выходов и шины входов. , Блок 7 согласования сигналов передает сигналы с первого э,талонйО го интерфейса 2 на второй эталонный интерфейс 3 с второго эталонного интерфейса 3 на первый эталонный и контролируемый интерфейсы 2 и 4, приводят их (сигналы к необходимом логическому ypoBHiQ, а также разделяя их логически, что позволяет раз вязать входы эталонного и контролйр емого объектов. С выхода блока 8 сравнения передаются результаты контроля (годенбрак ) в блок 9 индикации и через . элемент,ИЛИ 21 на элемент 25 з.апрета. . По входу ввода информации устройства производится запись тестовых программ в узел 23 памяти. Сигнал с входа 10 пуска устройства устанавливает в исходное -состояние счетчик 22 адреса и регистр 27 ошибки блока 8 сравнения. После этого импульсы с входа 13 через элемент 25 запрета вновь начинают изменять состояние счетчика 22 адреса. Состояние счетчика 22 адреса вызывает изменение информации на выходе узла 23 памяти, которая, в свою очередь, поступает на регистр 15 управляющих сигналов и регистр 16 данных на интерфейсы 2-4, причем сигналы с регистра 16 данных выдаются позже. Генератор 24 - формирует по четвертому выходу строб-импульс для блока В сравнения, учитывающий задержку передачи данных в интерфейсах. Возможность изменять начало программы контроля и ее конец задается и осуществляется с помощью двух регистдов 17 и 18 адреса узла 19 сравнения и элемента ИЛИ 21,причем, если регистр 18 адреса определяет начало программы, то регистр 17 адреса - ее конец. Гибкое изменение на чала и .конца программы контроля позволяет значительно сократить общее время контроля изделий. Так, современное производство БИС и СБИС имеет средний выход годных изделий от общей партии порядка 10-15%. Зная статистические данные О браке и какие тесты контроля выявляют этот брак, можно отбраковывать изделия в основном на первых же тестах, не продолжая всей программы контроля. Изг нилась технология производства изменилось соотношение процента брака по операциям, можно изменить очередность прохождения тестов. Предлагаемое выполнение устройства и его связей позволило сократить общее время контроля БИС интерфейса микропроцессорного набора сер. К580 по сравнению с известным в 8 раз.

1

/ ГЛГ

фиг.1

f

FS

f7

хЛ

:/«

/2

б:::.

Af

20

19

fe

. . м/-

«

16

25

2

ipuz г

29

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля дискретных блоков | 1977 |

|

SU746524A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для автоматическогоКОНТРОля бОльшиХ иНТЕгРАльНыХ CXEM | 1978 |

|

SU798841A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ..V | |||

Авторы

Даты

1983-09-07—Публикация

1982-05-04—Подача