Изобретение относится к вычислительной технике и может быть использовано в аппаратуре контроля цифровых блоков квазиэлектронных АТС в условиях серийного производства с большой номенклатуррй цифровых блоков.. , . Известно устройство для контроля логических схем, содержащее блок ввода, регистр задания, блоки цифроаналоговых и аналого-цифровых преобразователей, блок сравнения, блок управления, блок индикации, блок эталонов, регистр маски и коммутатор 1 .

Недостатком устройства является недостаточное быстродействие.

Наиболее близким к предлагаемому по технической сущности является многоканальное устройство тестового контроля цифровых узлов ЭВМ, содержащее блок ввода, блок памяти, адресные выходы которого через блок передачи адреса соединены с регистром теста, блок индикации, генератор тактовых импульсов, одним выходом соединенный через элемент И с входом счетчика адреса, а другим выходом - с блоком приема-передачи и через второй элемент И со стробирующим входом блока передачи адреса, выход счетчика адреса соединен с адресными входами блока памяти 2.

Недостатком известного устройства является наличие коммутационных полей, неуправляемых запоминающим устройством, что создает трудности в перепрограммировании, снижает быстродействие.

Цель изобретения. - повыщение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее блок памяти, первая группа информационных выходов которого через блок элементов И соединена с первой группой информационных входов регистра тестов, вторая группа информационных входов которого соединена с второй группой информационных выходов блока памяти, группу п схем сравнения (где п - число выводов контролируемого блока), элементы И, введены группа п коммутаторов признаков, группа п формирователей единичного сигнала, группа п формирователей нулевого сигнала, элемент запрета, причем каждый двунаправленный вывод контролируемого блока соединен с выходами соответствующего формирователя единичного и нулевого сигналов группы и первым входом соответствующей схемы сравнения группы, второй вход которой соединен с первым выходом соответствующего коммутатора признаков группы, четыре входа параметров контрольных сигналов каждого из которых соединены с группой выходов регистра тестов, тактовые входы п коммутаторов признаков группы соединены с первым тактовым входом устройства, первый

и второй выходы каждого коммутатора признаков группы соединены с входами соответствующих формирователей единичного и нулевого сигналов группы, выходы схем сравнения группы соединены с соответствующими входами первого элемента И, выход которого соединен с первым входом элемента запрета, второй вход и выход которого соединены соответственно с первым выходом второй группы информационных выходов блока памяти и первым входом второго элемента И, второй вход которого является вторым тактовым входом устройства, а выход соединен с блокирующим входом блока элементов И.

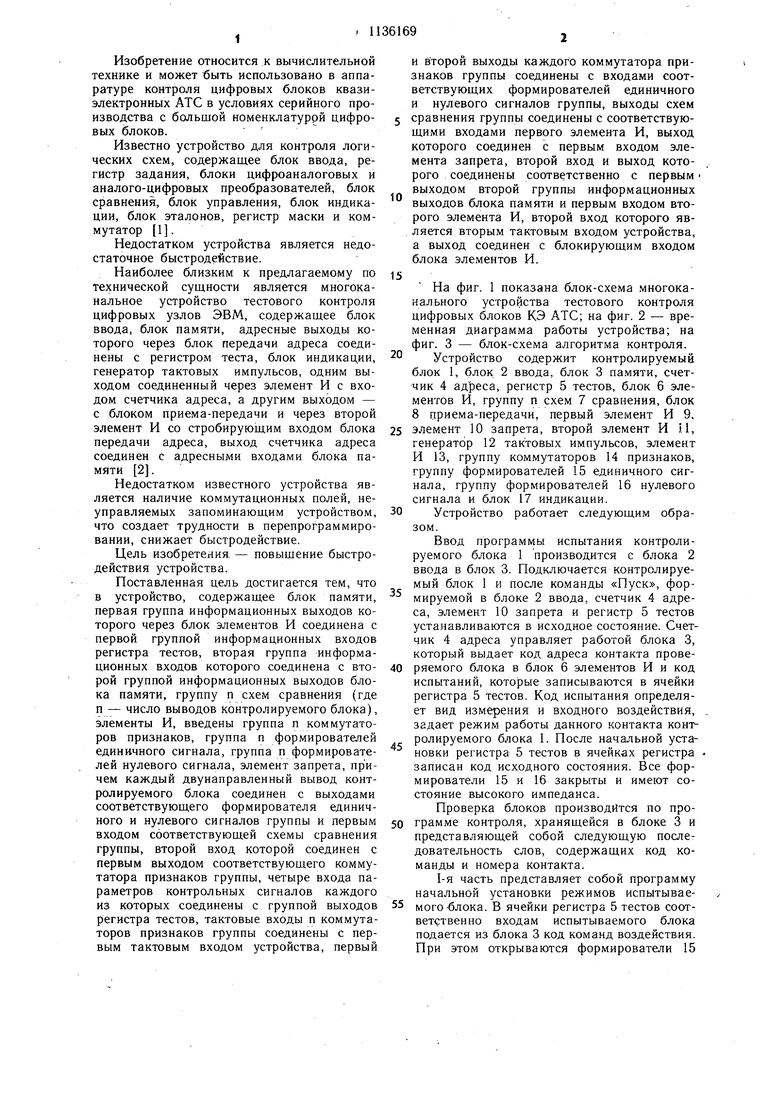

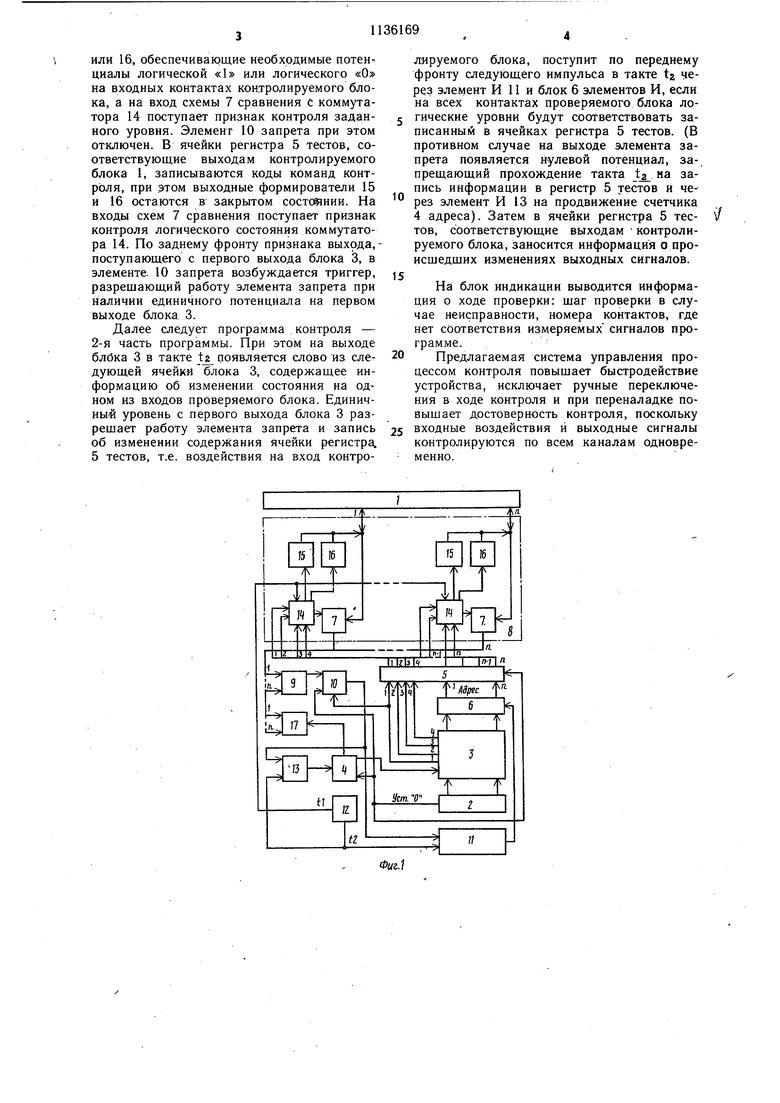

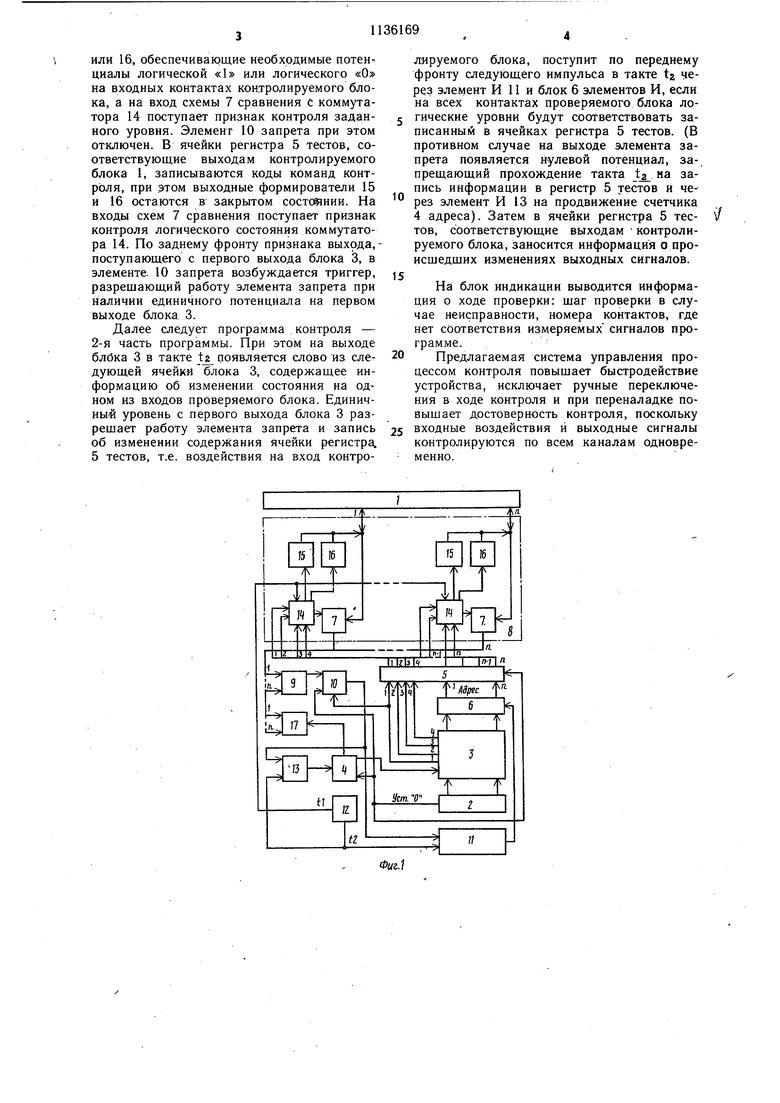

На фиг. 1 показана блок-схема многоканального устройства тестового контроля цифровых блоков КЭ АТС; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - блок-схема алгоритма контроля.

Устройство содержит контролируемый блок 1, блок 2 ввода, блок 3 памяти, счетчик 4 адреса, регистр 5 тестов, блок 6 элементов И, группу п схем 7 сравнения, блок 8 приема-передачи, первый элемент И 9, элемент 10 запрета, второй элемент И И, генератор 12 тактовых импульсов, элемент И 13, группу коммутаторов 14 признаков, группу формирователей 15 единичного сигнала, группу формирователей 16 нулевого сигнала и блок 17 индикации.

Устройство работает следующим образом.

Ввод программы испытания контролируемого блока 1 производится с блока 2 ввода в блок 3. Подключается контролируемый блок 1 и после команды «Пуск, формируемой в блоке 2 ввода, счетчик 4 адреса, элемент 10 запрета и регистр 5 тестов устанавливаются в исходное состояние. Счетчик 4 адреса управляет работой блока 3, который выдает код адреса контакта проверяемого блока в блок 6 элементов И и код испытаний, которые записываются в ячейки регистра 5 тестов. Код испытания определяет вид измерения и входного воздействия, задает режим работы данного контакта контролируемого блока 1. После начальной установки регистра 5 тестов в ячейках регистра записан код исходного состояния. Все формирователи 15 и 16 закрыты и имеют состояние высокого импеданса.

Проверка блоков производится по программе контроля, хранящейся в блоке 3 и представляющей собой следующую последовательность слов, содержащих код команды и номера контакта.

1-я часть представляет собой программу начальной установки режимов испытываемого-блока. В ячейки регистра 5 тестов соответ ;твенно входам испытываемого блока подается из блока 3 код команд воздействия. При этом открываются формирователи 15

или 16, обеспечивающие иеобхрдимые потенциалы логической «1 или логического «О на входных контактах контролируемого блока, а на вход схемы 7 сравнения с коммутатора 14 поступает признак контроля заданного уровня. Элемент 10 запрета при этом отключен. В ячейки регистра 5 тестов, соответствующие выходам контролируемого блока I, записываются коды команд контроля, при этом выходные формирователи 15 и 16 остаются в закрытом состоянии. На входы схем 7 сравнения поступает признак контроля логического состояния коммутатора 14. По заднему фронту признака выхода,поступающего с первого выхода блока 3, в элементе. 10 запрета возбуждается триггер, разрещающий работу элемента запрета при наличии единичного потенциала на первом выходе блока 3.

Далее следует программа контроля - 2-я часть программы. При этом на выходе блбка 3 в такте 1г появляется слово из следующей ячейки блока 3, содержащее информацию об изменении состояния на одном из входов проверяемого блока. Единичный уровень с первого выхода блока 3 разрещает работу элемента запрета и запись об изменении содержания ячейки регистра. 5 тестов, т.е. воздействия на вход контролируемого блока, поступит по переднему фронту следувощего импульса в такте tj через элемент И 11 и блок 6 элементов И, если на всех контактах проверяемого блока логические уровни будут соответствовать записанныгй в ячейках регистра 5 тестов. (В противном случае на выходе элемента запрета появляется нулевой потенциал, запрещающий прохождение такта t2 на запись информации в регистр 5 тестов и через элемент И 13 на продвижение счетчика 4 адреса). Затем в ячейки регистра 5 тес- / тов, соответствующие выходам контролируемого блока, заносится информация о происщедщих изменениях выходных сигналов.

На блок индикации выводится информация о ходе проверки: щаг проверки в случае неисправности, номера контактов, где нет соответствия измеряемых сигналов программе.

0 Предлагаемая система управления процессом контроля повыщает быстродействие устройства, исключает ручные переключения в ходе контроля и при переналадке повышает достоверность контроля, поскольку

5 входные воздействия и выходные сигналы контролируются по всем каналам одновре- менно.

Hen.о Зати Cm (41

cmdl Инфвьа as

ltH(f.itnl

за

бьа./кг.тесаа ./11еста

Sta.iaiSf.efзапкта)

Smaxnpma

t,wn

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ, содержащее блок памяти, первая группа информационных выходов которого через блок элементов И соединена с первой группой информационных входов регистра тестов, вторая группа информационных входов которого соединена с второй группой информационных выходов блока памяти, группу п схем сравнения (где п - число выводов контролируемого блока), элементы И, отличающееся тем, что, с целью повышения быстродействия, оно содержит группу п коммутаторов признаков, группу п формирователей единичного сигнала, группу п формирователей нулевого сигнала, элемент запрета, причем каждый двунаправленный вывод контролируемого блока соединен с выходами соответствующего формирователя единичного и нулевого сигналов группы и первым входом соответствующей схемы сравнения группы, второй вход которой соединен с первым выходом соответствующего коммутатора признаков группь, четыре входа параметров контрольных сигналов каждого из которых соединены с группой выходов регистра тестов, тактовые входы п коммутаторов признаков группы соединены с первым тактовым входом устройства, первый и второй выходы каждого коммутатора признаков группы соединены Q входами соответствующих формирователей единичного и нулевого сигналов группы, выходы схем сравнения группы соединены с соотг; ветствующими входами первого элемента И, выход которого соединен с первым входом элемента запрета, второй вход и выход которого соединены соответственно с первым выходом второй группы информационных выходов блока памяти и первым входом второго элемента И, второй вход которого является вторым тактовым входом устройства, а выход соединен с блокирующим вхоО9 О) дом блока элементов И. О) со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля цифровыхСХЕМ | 1979 |

|

SU849217A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин | 1977 |

|

SU656065A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1983-04-01—Подача