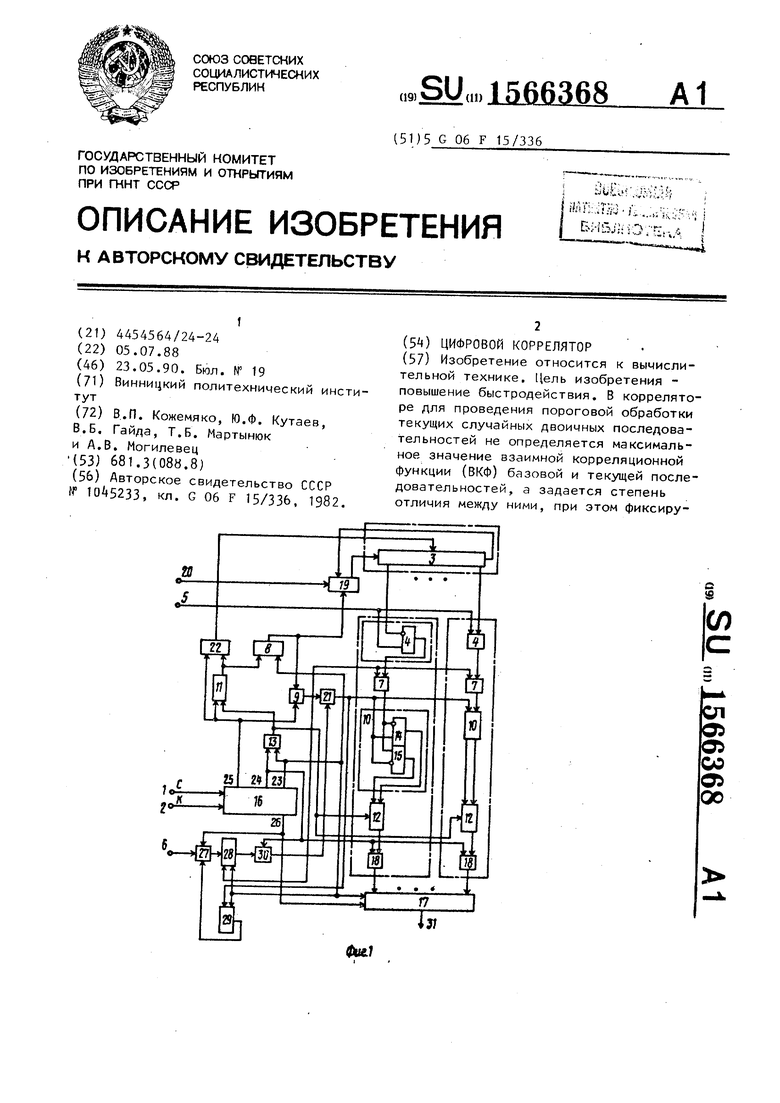

Изобретение относится к автоматике и вычислительной технике и может быть использовано в корреляционных экстремальных системах.

Целью изобретения является повышение быстродействия.

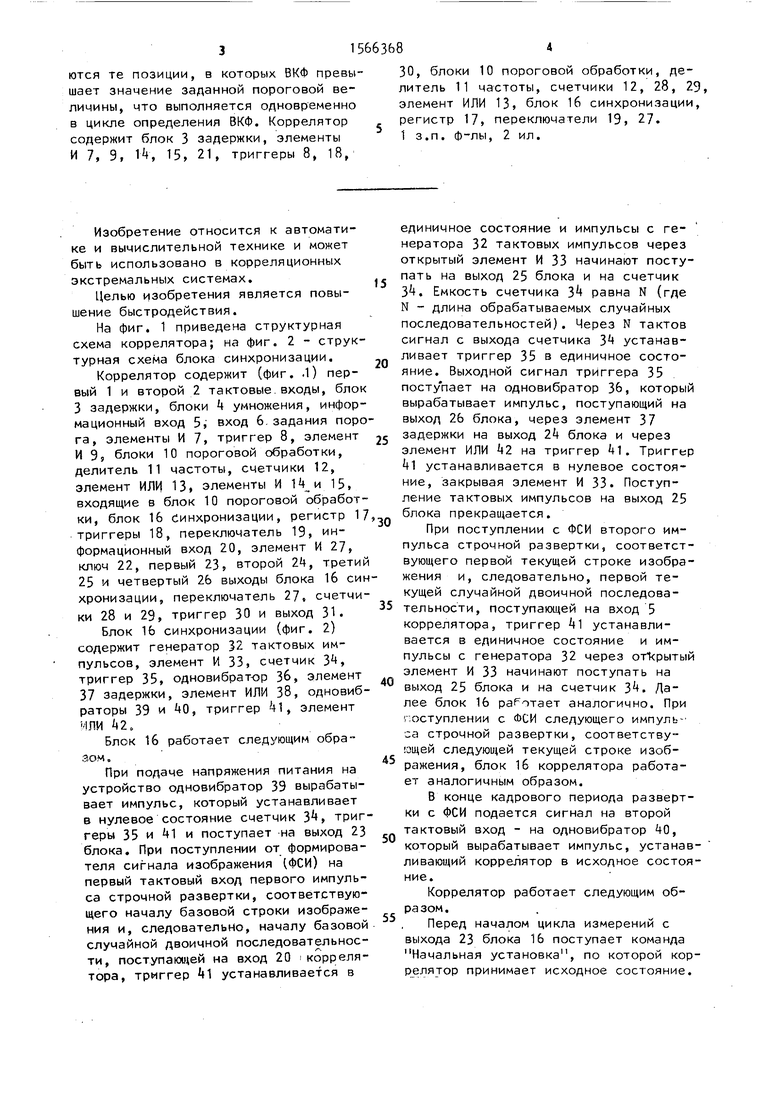

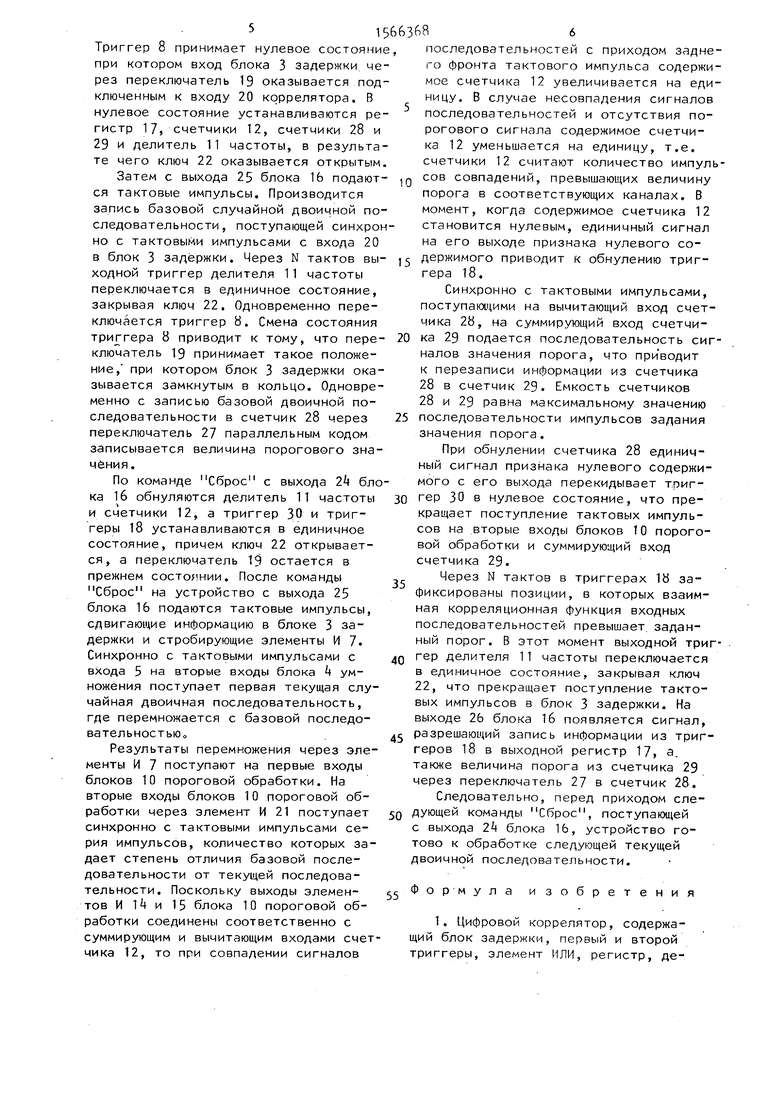

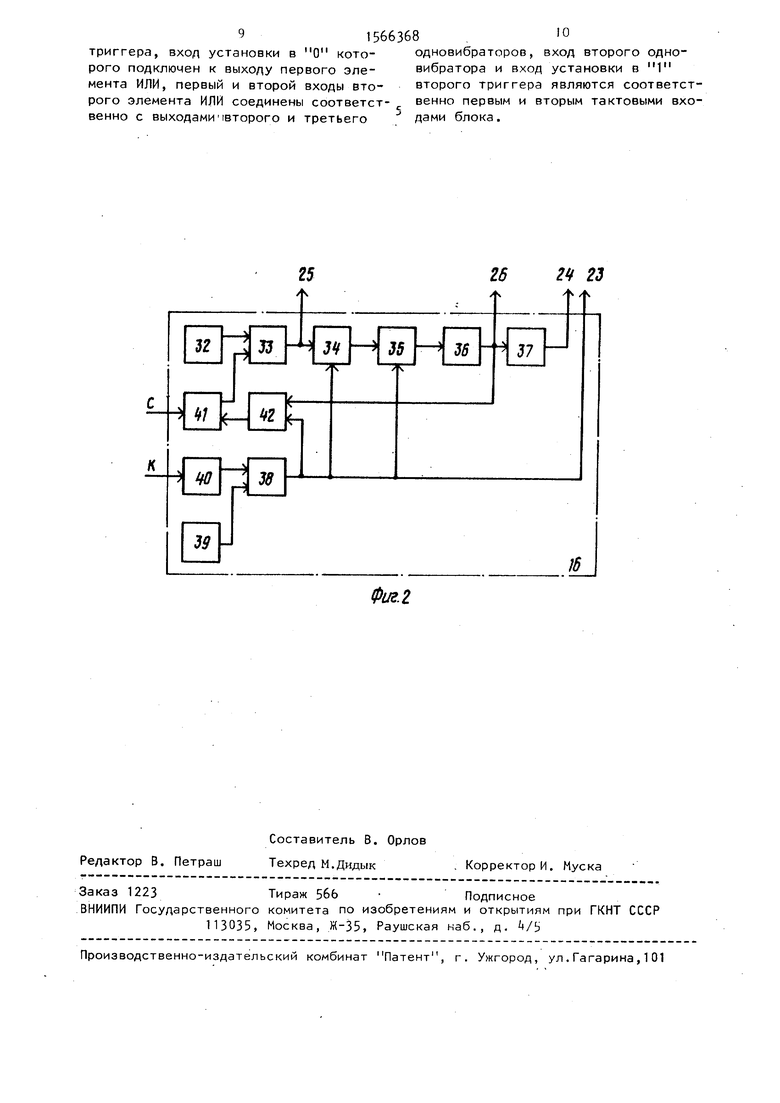

На фиг. 1 приведена структурная схема коррелятора; на фиг. 2 - структурная схема блока синхронизации.

Коррелятор содержит (фиг. .1) первый 1 и второй 2 тактовые входы, блок 3 задержки, блоки Ц умножения, информационный вход 5, вход 6 задания поро га, элементы И 7, триггер 8, элемент И 9 9 блоки 10 пороговой обработки, делитель 11 частоты, счетчики 12, элемент ИЛИ 13, элементы И 14 и 15, входящие в блок 10 пороговой обработки, блок 16 синхронизации, регистр 17 триггеры 18, переключатель 19, информационный вход 20, элемент И 27, ключ 22, первый 23, второй 24, третий 25 и четвертый 26 выходы блока 16 синхронизации, переключатель 27, счетчики 28 и 29, триггер 30 и выход 31.

Блок 16 синхронизации (фиг. 2) содержит генератор 32 тактовых импульсов, элемент И 33, счетчик 34, триггер 35, одновибратор 36, элемент 37 задержки, элемент ИЛИ 38, одновиб- раторы 39 и АО, триггер 41, элемент ;-1ЛИ 42.

Блок 16 работает следующим образом.

При подаче напряжения питания на устройство одновибратор 39 вырабатывает импульс, который устанавливает в нулевое состояние счетчик 34, триггеры 35 и 41 и поступает на выход 23 блока. При поступлении от формирователя сигнала изображения (ФСИ) на первый тактовый вход первого импульса строчной развертки, соответствующего началу базовой строки изображения и, следовательно, началу базовой случайной двоичной последовательности, поступающей на вход 20 i коррелятора, триггер 41 устанавливается в

5

0

5

0

35

40

45

50

55

единичное состояние и импульсы с генератора 32 тактовых импульсов через открытый элемент И 33 начинают поступать на выход 25 блока и на счетчик 34. Емкость счетчика 34 равна N (где N - длина обрабатываемых случайных последовательностей). Через N тактов сигнал с выхода счетчика 34 устанавливает триггер 35 в единичное состояние. Выходной сигнал триггера 35 посту пает на одновибратор 36, который вырабатывает импульс, поступающий на выход 26 блока, через элемент 37 задержки на выход 24 блока и через элемент ИЛИ 42 на триггер 41. Триггер 41 устанавливается в нулевое состояние, закрывая элемент И 33. Поступление тактовых импульсов на выход 25 блока прекращается.

При поступлении с ФСИ второго импульса строчной развертки, соответствующего первой текущей строке изображения и, следовательно, первой текущей случайной двоичной последовательности, поступающей на вход 5 коррелятора, триггер 41 устанавливается в единичное состояние и импульсы с генератора 32 через открытый элемент И 33 начинают поступать на выход 25 блока и на счетчик 34. Далее блок 16 работает аналогично. При . оступлении с СИ следующего импуль са строчной развертки, соответствующей следующей текущей строке изображения, блок 16 коррелятора работает аналогичным образом.

В конце кадрового периода развертки с ФСИ подается сигнал на второй тактовый вход - на одновибратор 40, который вырабатывает импульс, устанавливающий коррелятор в исходное состояние.

Коррелятор работает следующим обра зом.

Перед началом цикла измерений с выхода 23 блока 16 поступает команда Начальная установка, по которой коррелятор принимает исходное состояние.

5156636В6

Триггер 8 принимает нулевое состояние, последовательностей

го фронта тактового мое счетчика 12 уве ницу. В случае несо последовательностей рогового сигнала сод ка 12 уменьшается на счетчики 12 считают сов совпадений, прев порога в соответству момент, когда содерж становится нулевым, на его выходе призна J5 держимого приводит к гера 18.

при котором вход блока 3 задержки через переключатель 19 оказывается подключенным к входу 20 коррелятора. В нулевое состояние устанавливаются регистр 17, счетчики 12, счетчики 28 и 29 и делитель 11 частоты, в результате чего ключ 22 оказывается открытым.

Затем с выхода 25 блока 16 подаются тактовые импульсы. Производится запись базовой случайной двоичной последовательности, поступающей синхронно с тактовыми импульсами с входа 20 в блок 3 задержки. Через N тактов выходной триггер делителя 11 частоты переключается в единичное состояние, закрывая ключ 22. Одновременно переключается триггер 8. Смена состояния триггера 8 приводит к тому, что переключатель 19 принимает такое положение, при котором блок 3 задержки оказывается замкнутым в кольцо. Одновременно с записью базовой двоичной последовательности в счетчик 28 через переключатель 27 параллельным кодом записывается величина порогового значения.

По команде Сброс с выхода 2k блока 16 обнуляются делитель 11 частоты и счетчики 12, а триггер 30 и триггеры 18 устанавливаются в единичное состояние, причем ключ 22 открывается, а переключатель 19 остается в прежнем состоянии. После команды Сброс на устройство с выхода 25 блока 16 подаются тактовые импульсы, сдвигающие информацию в блоке 3 задержки и стробирующие элементы И 7. Синхронно с тактовыми импульсами с входа 5 на вторые входы блока k умножения поступает первая текущая случайная двоичная последовательность, где перемножается с базовой последовательностью.

Результаты перемножения через элементы И 7 поступают на первые входы блоков 10 пороговой обработки. На вторые входы блоков 10 пороговой обработки через элемент И 21 поступает синхронно с тактовыми импульсами серия импульсов, количество которых задает степень отличия базовой последовательности от текущей последовательности. Поскольку выходы элемен- тов И 14 и 15 блока 10 пороговой обработки соединены соответственно с суммирующим и вычитающим входами счетчика 12, то при совпадении сигналов

последовательностей

10

20

5

0

5

с приходом заднего фронта тактового импульса содержимое счетчика 12 увеличивается на единицу. В случае несовпадения сигналов последовательностей и отсутствия порогового сигнала содержимое счетчика 12 уменьшается на единицу, т.е. счетчики 12 считают количество импульсов совпадений, превышающих величину порога в соответствующих каналах. В момент, когда содержимое счетчика 12 становится нулевым, единичный сигнал на его выходе признака нулевого со- J5 держимого приводит к обнулению трИ1- гера 18.

Синхронно с тактовыми импульсами, поступающими на вычитающий вход счетчика 28, на суммирующий вход счетчика 29 подается последовательность сигналов значения порога, что приводит к перезаписи информации из счетчика 28 в счетчик 29. Емкость счетчиков 28 и 29 равна максимальному значению последовательности импульсов задания значения порога.

При обнулении счетчика 28 единичный сигнал признака нулевого содержимого с его выхода перекидывает гер 30 в нулевое состояние, что прекращает поступление тактовых импульсов на вторые входы блоков 10 пороговой обработки и суммирующий вход счетчика 29.

Через N тактов в триггерах 1й зафиксированы позиции, в которых взаимная корреляционная функция входных последовательностей превышает заданный порог. В этот момент выходной триггер делителя 11 частоты переключается в единичное состояние, закрывая ключ 22, что прекращает поступление тактовых импульсов в блок 3 задержки. На выходе 26 блока 16 появляется сигнал, разрешающий запись информации из триггеров 18 в выходной регистр 17, а, также величина порога из счетчика 29 через переключатель 27 в счетчик 28.

Следовательно, перед приходом сле- 0 дующей команды Сброс, поступающей с выхода 24 блока 16, устройство готово к обработке следующей текущей двоичной последовательности.

5

0

5

Формула изобретения

1. Цифровой коррелятор, содержащий блок задержки, первый и второй триггеры, элемент ИЛИ, регистр, делитель частоты, ключ, переключатель, элемент И, счетчик, блок синхронизации, N каналов, каждый из которых содержит блок умножения, счетчик, первы и второй элементы И, причем первый выход блока синхронизации соединен с входом разрешения записи регистра, вход обнуления которого соединен с первым входом элемента ИЛИ, входом установки в О первого триггера и вторым выходом блока синхронизации, третий выход которого соединен с вторым входом элемента ИЛИ, выход которого соединен с входами установки в О делителя частоты и счетчиков каждого канала, информационный вход делителя частоты соединен с информационным входом ключа и четвертым выходом блока синхронизации, управляющий вход ключа соединен с входом установки в 1 первого триггера и выходом делителя частоты, выход ключа соединен с тактовым входом блока задержки, информационный вход которого соединен с выходом переключателя, первый информационный и управляющий входы которого соединены соответственно с выходом блока задержки и выходом первого триггере, второй информационный вход пе- реклюмателя является первым входом коррелятора, первый и второй тактовые входы блока синхронизации являются од-юименными входами коррелятора, прямые входы первых элементов И под- ключены к второму информационному входу коррелятора, инверсные входы .лементов И всех ка.налов соединены с соответствующими выходами блока задержки s выход регистра является выхо- дом коррелятораs отличающийся тем, что, с целью повыше., k 6bC iJ v4c Г8ИЯ в Hfcro ДОПОЛНИоЛь,;, L ьздеью уторой счгтчи , второй , t юночате/.ь, второй элемент И, в

канал дополнительно введены третий и четвертый элементы И и триг- 4 rep, причем в каждом канале выход первого элемента И соединен с первым входом второго элемента И, выход ко- торого соединен с инверсным входом третьего элемента И и прямым входом четвертого элемента И, выход третьего элемента И соединен с суммирующим вводом счетчика, вычитающий вход ко- торого соединен с выходом четвертого элемента И, выход признака обнуления счетчика соединен с входом установки в 0м триггера, выходы триггеров всех

каналов соединены с соответствующими входами регистра, третий выход блока синхронизации соединен с входами установки в 1 второго триггера и триггеров всех каналов, второй выход блока синхронизации соединен с входами обнуления первого и второго счетчиков четвертый выход блока синхронизации соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, а выход с вычитающим входом первого счетчика, вторыми входами вторых элементов И каждого канала и первым входом второго элемента И, второй вход которого соединен с выходом второго триггера, а выход - с суммирующим входом второго счетчика и прямым входом третьего элемента И и инверсным входом четвертого элемента И каждого канала, первый выход блока синхронизации соединен с управляющим входом второго переключателя, первый информационный вход которого является входом задания порога коррелятора, второй информационный вход второго переключателя соединен с выходом второго счетчика, а выход - с входом задания начального состояния первого счетчика, выход признака обнуления которого соединен с входом установки в О второго триггера.

2, Коррелятор по п. 1, отличающийся тем, что, блок синхронизации содержит три одновибрато- ра, два триггера, счетчик, генератор тактовых импульсов, элемент задержки, два элемента ИЛИ и элемент И, причем выход первого одновибратора соединен с входом элемента задержки и первым входом первого элемента ИЛИ и ЯВЛЯРГ- й первым выходом блока, выход эг - мента задержки является третьим вь- ходом блока, вход первого одновиЗра- тора подключен к выходу первого триггера, вход установки в О которого соединен с входом установки в О счетчика, вторым выходом второго элемента ИЛИ и выходом второго элемента ИЛИ и является вторым выходом блока, вход установки в 1 первого триггера подключен к выходу счетчика, информационный вход которого соединен с выходом элемента И и является четвертым выходом блока, первый и второй входы элемента И соединены со- ответственно с выходом генератора тактовых импульсов и выходом второго

триггера, вход установки в О которого подключен к выходу первого элемента ИЛИ, первый и второй входы втоодновибраторов, вход второго одно- вибратора и вход установки в 1 второго триггера являются соответстрого элемента ИЛИ соединены соответст- с венно первым и вторым тактовыми входами блока.

венно с выходами второго и третьего

одновибраторов, вход второго одно- вибратора и вход установки в 1 второго триггера являются соответственно первым

дами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1982 |

|

SU1045233A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1991 |

|

RU2051413C1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Тренажер радиотелеграфиста | 1987 |

|

SU1456987A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия. В корреляторе для проведения пороговой обработки текущих случайных двоичных последовательностей не определяется максимальное значение взаимной корреляционной функции (ВКФ) базовой и текущей последовательностей, а задается степень отличия между ними, при этом фиксируются те позиции, в которых ВКФ превышает значение заданной пороговой величины, что выполняется одновременно в цикле определения ВКФ. Коррелятор содержит блок 3 задержки, элементы И 4, 7, 9, 14, 15, 21 триггеры 8, 18, 30, блоки 10 пороговой обработки, делитель 11 частоты, счетчики 12, 28, 29 элемент ИЛИ 13, блок 16 синхронизации, регистр 17, переключатели 19, 27. 1 з.п.ф-лы, 2 ил.

25

26

14 23

| Брауновская трубка для приема дальновидения | 1934 |

|

SU45233A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-05—Подача