иен с вторым выходом решающего блока

5. Устройство по пп. 1-4, о т л ичающееся Tefvi, что второй решакядий блок содержит сумматор, формировательуровня О и ключ 4, причем входы Сум1.1атора соединены соответственно с первым, вторьЛ/ и Третьим входами второго-решающего блока, выход сумматора соединен с первым выходом второго решающего блока, первый вход ключа соединен с выходом формирователя уровня О, второй вход ключа соединен с четвертым входом второго решагадего блока, а выход с вторым выходом второго решающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного декодирования в целом | 1983 |

|

SU1109902A1 |

| Устройство для мажоритарного декодирования в целом | 1984 |

|

SU1243101A1 |

| Устройство для преобразования кодов в системе передачи данных | 1982 |

|

SU1086449A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1986 |

|

SU1363485A2 |

| Устройство для передачи кодовых комбинаций постоянного веса | 1981 |

|

SU982055A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1091210A1 |

| Устройство для приема и передачи избыточных сигналов | 1981 |

|

SU976466A1 |

1. УСТРОЙСТВО ДЛЯ КАЖОРИТАРНОГО ДЕКОДИРОВАНИЯ, содержащее аналоговый демодулятор, вьоход которого подключен через последовательно соединенные квантизатор, первый регистр, yпpaвляe ый вентиль и первый элемент ИЛИ к входу второго регистра, отличающеес я тем, что, с целью пов ;1шения помехоустойчивости, в него введены два решающих блока, второй управляемый вентиль, блок сравнения и второй элемент ИЛИ, причем выход квантизатора через второй управляемый вентиль, управляющий вход которого соединен с управляющим входом первого управляемого вентиля, соединен с вторым входом первого элемента ИЛИ и с первыми входами решающих блоков, вторые входы которых подключены к выходу первого регистра, третьи входы решакщих блоков соединены с выходом второго регистра, кроме того, первый и второй решающие блоки четвертым входом подклю.чены соответственно к первому и второму выходу блока сравнения, первые выходы решающих блоков подключены соответственно к первому и второму входам блока сравнения, вторые выходы решалсвдих блоков соединены через второй элемент ИЛИ с выходом устройства. 2.Устройство по п. 1, отлич а ,ю щ е е с я , гс KEaiiTi;затор состоит из формирователя пороговых напржкений, преобразователя уровней,- дешифратора и многоустойчивого элемента,- причем выходы формирователя пороговых напряжений подключены к соответствующим входам преобразователя уровней, vii -и вход преобразователя уровней соединен с входом квантизатора, выходы преобразователя уровней соединены соответственно с входами дешифратора, кроме того, первый выкод преобразователя уровней и выходы дешифратора соединены соответственно с входами многоустойчивого элe ieнтa, 50 выход которого соединен с выходом квантизатора. 3,Устройство по п. 1 и 2, о т л и чающееся тем, что., блок сравнения состоит пз блока вычитания и элемента liE,- причем первый и второй входь: блока вычитания соединены соответственно с первым и вторым входами блока сравнения, выход блока вычитания соединен с . aiSSS первым выходом блока срглвнения и через элемент НЕ с вторы-м выходом блока сравнения. 4. Устройство по пп. 1-3, отличающееся тем, что первый решающий блок содержит три блока вычитания, су:-{матор, формирователь уровня №-1 и ключ, причем первые входы блоков вычитания соединейы соответственно с первым, вторым и третьим входами первого решанадего, блока, вторые входы блоков вычита- ния соединены с выходом формирователя уровня VV1-1 и с первым входом ключа, выходы блоков вычитания соединены через сумматор с первым выходом решающего блока, второй вход ключа подключен к четвертому входу решающего блока, выход ключа соеди

Изобретение относится к электросвязи, а именно, к системам передачи данных, в которых для передачи сообщений используют составные сигналы с избыточностью, формируемые на основе кодов с повторением, и может быть использовано в приемных устройствах систем передачи данных при трехкратном дублировании сообщений,

Известно устройство для оптимального приема сообщений, закодированных с избыточностью, содержащее перемножители, интеграторы и блок сравнения, и обеспечиваквдее потенциальную помехоустойчивость приема составных сигналов с избыточностью С 1 .

Однако нри обработке длинных и сверхдлинных кодов оно практически нереализуемо.

Наиболее близким по технической сущности к предлагаемому является устройство для мажоритарного декодирования двоичных кодов, содержащее аналоговый демодулятор, выход которсзго подключен через последовательно соединенные квантизатор, первый регистр, yпpaвляe sый вентиль и первый элемент ИЛИ к входу второго регистра С

Недостаток известного устройства низкая помехоустойчивость.

Цель изобретения - повышение пом хоустойчивости,

Поставлен.чая цель достигается TBMf что в устройство для мажоритарного декодирования, содержащее аналоговый демодулятор, выход которого подключен через последовательн соединеншле квантизатор, первый регистр, управляемый вентиль И первый элемент ИЛИ к входу второго регистра, введены два решающих блока, второй управляегф,.1й вентиль, блок сравнения и второй элемент ИЛИ, причем БГлход квантизатора через второй управляемый вентиль, управляющий вход которого соединен с управляющим входом первого управляемого вентиля, соединен с вторьи )зходом

2

первого элемента ИЛИ и с первыми входами решающих блоков, вторые входы которых подключены к выходу первого регистра, третьи входы решающих блоков соединены с выходом второго, регистра, кроме того, первый и второй решающие блоки четвертым входом подключены соответственно к первому и второму выходу блока сравнения , первые выходы решающих блоко подключены соответственно к первог у и второму входам блока сравнения, вторые выходы решающих блоков соединены через второй элемент ИЛИ с выходом устройства.

При этом квантизатор состоит из формирователя пороговых .напряжений, преобразователя уровней, дешифратор И многоустойчивого элемента, причем выходы формирователя пороговых напрюкений подключены к соответствующим входам преобразователя уровней, м-ый вход преобразователя уровней соединен с входом квантизатора, выходы преобразователя уровней соединены соответственно с входами деш1- фратора, кроме того, первьш выход преобразователя уровней и выходь; дешифратора соединены соответственно с входами многоустойчивого элемента, выход которого- соединен с выходом квантизатора.

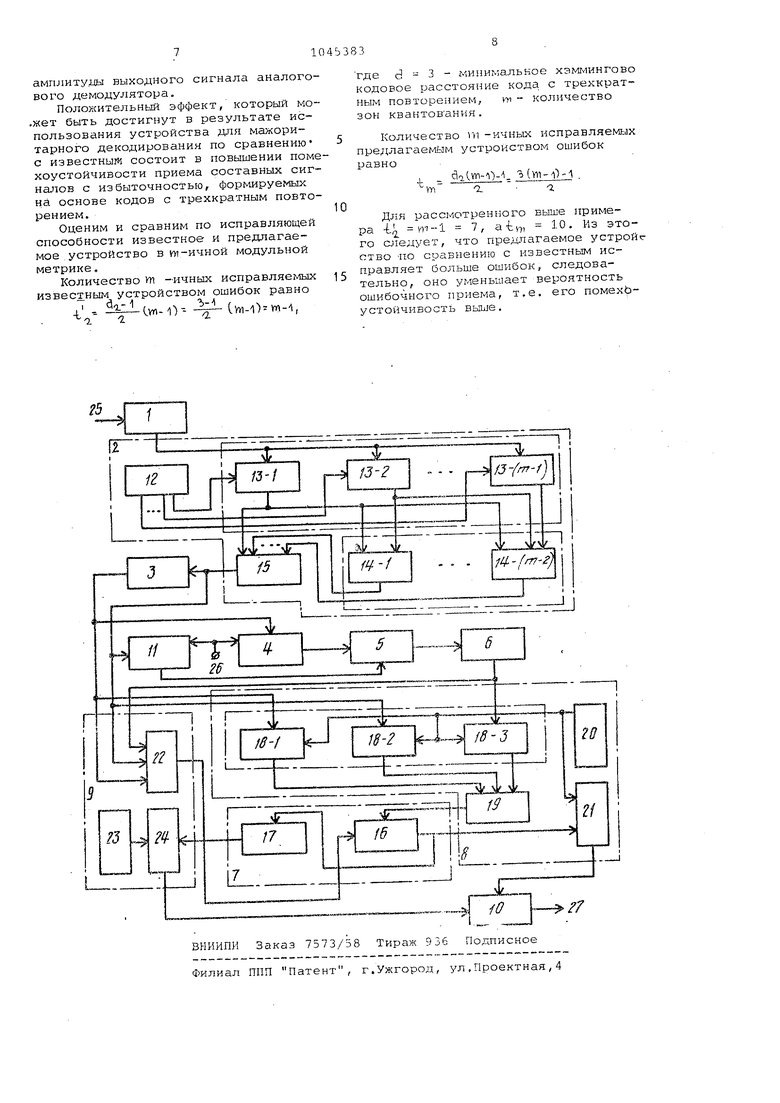

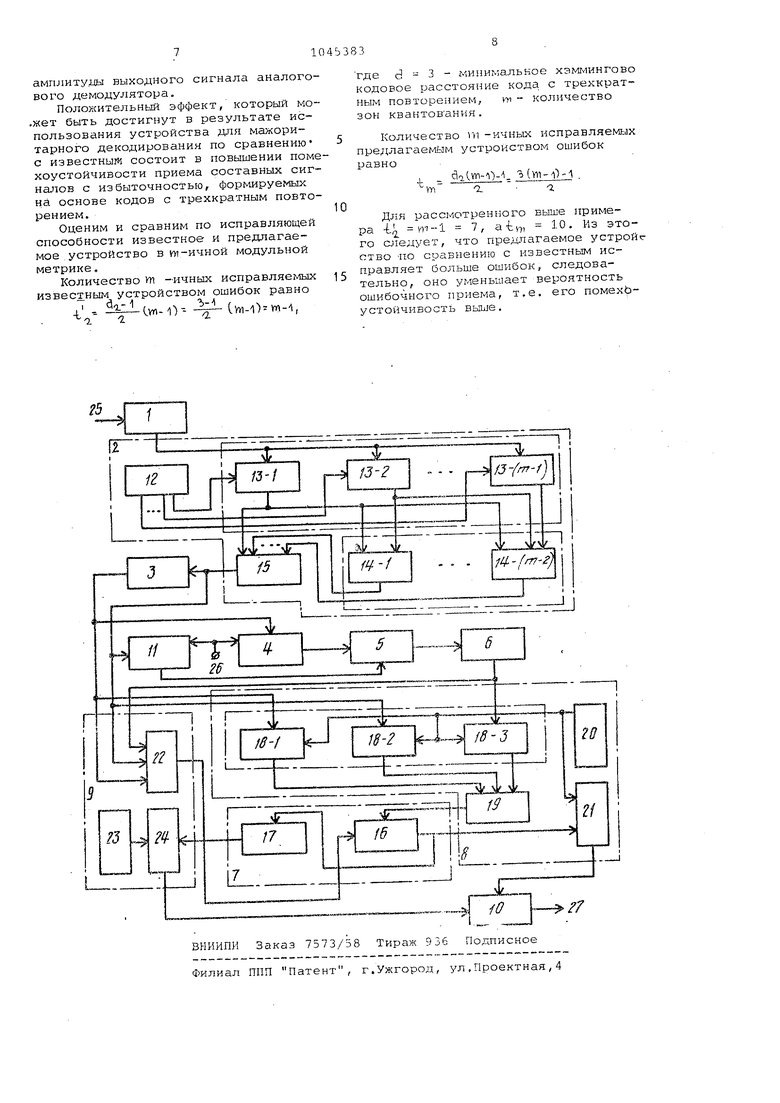

Блок сравнения состоит из блока вычитания и элемента НЕ, причем первый и второй входы блока вычитания соединены соответственно с первым и вторььм входами блока сравнени выход блока вычитания соединен с первым выходом блока сравнения и через элемент НЕ с вторым выходом блока сравнения.При этом первый решающий блок содержит три блока вычитания, сумматор, формирователь уровня(HI-1/ и ключ с причем первые входы блоксв вычитания соединены соответственно с первым, вторым и третьим входами первого решающего блока, вторые входы блоков вычитания соединены с Ь кходом формирователя уровня (in-l 1 и с первым входом ключа, выходы бл ков вычитания .соединены через сумматор с первым выходом решающего б ка, второй вход ключа подключен к четвертому входу решающего блока, выход ключа соеддинен с вторым выхо дом решающего блока. Причем второй решагаций блок содержит суглматор, формирователь уровня О, и ключ, причем входы сумматора соединены соответственно с первым, вторым и третьим входаг1и второго решающего блока, выход сумматора соединен с первым выходо второго решающего блока, первый вход ключа соединен с выходом формирователя уровня О, второй вход ключа соединен с четвертым входом второго решающего блока, а выход с вторым выходом второго решагадего блока. На чертеже изображена структурн схема устройства для мажоритарного декодирования. Схема содержит аналоговый демодулятор 1, квантизатор 2, первый р егистр 3, первый управляемый вентиль 4, первый элемент ИЛИ 5 второ регистр б, блок 7 сравнения, первы решающий блок 8, второй решающий блок 9, второй элемент ИЛИ 10, второй управляемый вентиль 11. . Квантизатор состоит из формирователя пороговых напряжений преобразователя (vn-l) на триггера дешифратора 14-1 т 14(hi-2) на элементах И и многоустойчивого элемента 15. Блок 7 сравнения содержит блок вычитания и элемент НЕ 17. Первый решающий блок 8 выполнен на блоках 18-1 т 18-3 вычитания, сумматоре 1 формирователе 20 уровняVn- 1 ключе 21. Второй решающий блок состоит из cyi /iMaTopa 22, формирователя 23 уровня О и ключа 24. Устройство также содержит входную шину 25, тактовую ишну 26. Вш-сод 27 устройства. Устройство для мажоритарного де кодирования работает следующим образом. На вход устройства поступает последовательный составной сигнал с избыточностью. 4-tV- ,, W,(.--. . s,,(.t),s.,,,w,..., где х- количество информационных сигналов в кодограмме с трехкратны повторением. В демодуляторе 1 его преобразую в аналоговый последовательный сост ной сигнал с избыточностью (суиество этой операции определяется способом приема элементарных сигналов, их типом, характеристиками канала связи, отношением cnrnaji - ш.ум и т.п. -(X,,X,v ,KI )-- ic,). Аналоговый сигнал X последовательно поступает на. вход квантизатора 2, а точнее - на входы триггеров 13-71 13 (№-1) преобразователя уровней. На другой вход каждого триггера 13т 1 7 13(т- 1 с соответствующего выхода формирователя 12 пороговых напряхкений подаются напряжения, определяющие порог срабатывания данного триггера. Если входной аналоговый сигнал квантизатора 2 меньше величины первого уровня, то все триггеры 13-1 г 13-(11-1) находятся в исходном (нулевом) состоянии. При этом на всех входах многоустойчивого элемента 15 управляющие сигналы отсутствуют, вследствие чего на его выходе формируется сигнал О. Если же входной аналоговый сигнал больше первого, но меньше второго порогового уровня напряжения, то срабатывает первый триггер 13-1, на первом входе элемента 15 формируется выходной сигнал 1, вследствие чего на выходе многоустойчивого элемента 15 форЕсли величина мируется сигнал сигнала на выходе аналогового демодулятора 1 такова, что срабатыва.ют первьШ и второй триггеры 13-1 и 13-2, управляющие сигналы появляются на первых двух входах элемента 15, а его вьк одной сигнал имеет значение 2, и т..д. Если же величина аналогового сигнала больше величины последнего порогового уровня напряжения, то срабатывают все триггеры 13-1 г 13(|м-1) г а управлякхцие сигналы будут присутствовать на всех входах, элемента 15. При этом из выходе многоустойчивого элемента 15 появляется сигнал )П-1. Таким образом, с помощью квантизатора 2 аналоговые сигналы преобразуют дискретные VTj-ичные сигналы. На выходе гсвантизатора 2 формируется последовательный дискретный избыточный сигнал Чг,Хг1,-Ду:.,) 77 7 i-i где { 0,1,2,. . ., Hi-lji который представляет собой трехкрат/НО повторенные информационные И1 кчные символы (сигналы). Сигнал псзследовательно поступает на вход .первого регистра 3 и одновременно через 3JieMeHT ИЛИ 5 на вход второго регистра 6 входы решающих блоков 8 и 9 dpH этом не воспринимают эти сигналы .

При этом для первой

,,,Z.,,...,J

- второй

г 0.,..., Z. t: j)

11,

одинаковых частей tri-ичной последовательности осуществляется запись в регистр б и в регистр 3 соответствекно. На время приема третьей части т -ичной последовательности. Я 1, Котсутствует управляющий сигнал на втором входде вентиля 4. Поэтому третья часть кп-ичной последовательности Z-3, поступает на соответствующие входы открытых на время: ее поступления решающих блоков 8 и 9, Таким образом, в соответствующие моменты времени на входах решаю щих блоков 8 и 9 будут,присутствова сигналы, соответствующие повторениям одноименных информационных сигналов iz,,2.i,7-i,,), .-1,.аД,2.г 1 ъ- Ло2Д-ъг , ч - - - -, ), Рассмотрим ЙальнеййуюОбработку кшкдого из троичных сигналов на при мере обработки трех повторений (они « образуют этот сигнал) первого информационного сигнала 7. Z ,1, . В блоке 8 каждый из элементарных сигналов 5 образующ.чх троичный сигнап, подается на входы блоков 18-1 т 18-3, на другой вход каждого из которых подается вырабатываемый формирователем 20 уровня дискретный сигнал VT) - 1, который вычитается из каждого из указанных сигналов. Разностные сигналы поступают на вход суььматора 19, в котором суь1мируются Результат этого суммирования подается ria вход блока 16 вычитания блока 7 сравнения. Тот же троичный сигнал, составлен Н:--й из повторений одного информационного сигнала, подается и на вход . о р о i о р eUi а юще г о блока 9. Точнее :;;; ВХОДЫ сумматора 22, в котором они С:у:чт -.-;ируются, Результат суммирования подается с вйходда сумг атора 22 на .другой ВХОДблока 16 вычитания. На

выходе блока 16 вычитания формируется разностный сигнал, знак которого показывает на значение двоичного символа, который необходимо подать на выход 27 устройства. Если вы ходной разностный сигнал блока 16 положителен, то.он воспринимается ключом 21, которьв открывается,, пропуская на выход 27 устройства через элемент ИЛИ 10 сигнал Если же

выходной сигнал блока 16 отрицателен , то после инверсии с помощью элемента 17 открывается ключ 24, пропуская на выход 27 устройства через элемент 10 двоичный сигнал 0

Таким образом, Б блоке В вычисляют степень близости этого сигнала (fpexзначного) к сигналу трехзначному (, у-г1 1, Л1-1) , 1 в решающем блоке 9 - к С15гналу (0,0,0) . Причем

степени близости определяются но дульным расстоянием ( - Т) - I. 1 где --i -ое повторение первого информационного сигнала, а ый эталонный сигнал соответствующего трехзначного эталонного сигнала. Как было отмечено, сигналы, соответствующие модул.ным расстояниям ( близости) , подаются на блок 7 сргишения,. в котором сравниваются. Е;СЛИ входное трехзначный сигнал блике к едип:--гч:ному эталонному hi-ичном масаггабе), то выходной сигнал блока 7 сразнен я - положительньш. Он подается в блок 8. где воспринимается ключом 21 и разрешает на вы,ход 27 устройства двоичного единичного сигнагга . В противном случае выходной управляющий сигнал блока 7 - отрицательный. Он воспринимается. блоком 9, из которого на выход 27 устройства считывается двоичный нулевой сигнал 0 , он задается с помощью формирователя 23 уровня соответственно единичный сигнал вт-ичном масштабе задается с помощью формирователя 20 уровня. После обработки всех троичных сигналов на входе решаю и-зх блоков- 8 и 9 (это BpeMiH опред::ел -;ется временем прохождения третьей части кодограммы) последн.ие закрываются и цикл обработки повторяется для следующего составного сигнала с избыточностью., Техническое, пpeи ii/щecтвo устройства по сравнению с базовым объектотл заключается в более полнсм использовании апостериорной информации о приЕ-1имаемых сигналах - vipi-o принятии решения учитывается зеличи.ч,;

амплитуды выходного сигнала аналогового демодулятора.

Положительный эффект, который мо.жет быть достигнут в результате использования устройства для мажоритарного декодирования по сравнению с известны состоит в повышении помехоустойчивости приема составных сигналов с избыточностью, формируемых на основе кодов с трехкратным повторением.

Оценим и сравним по исправляющей способности известное и предлагаемое .устройство в №-ичной модульной метрике.

Количество № -ичных исправляемых извест.ным устройством ошибок равно 1 .-1 ,. .. г(.Wl-O-vn--,

-lvn-1)t

0.

где d 3 - минимальное хэммингово кодовое расстояние кода, с трехкратным повторением, v-n - количество зон квантоБания .

Количество гп -ичных исправляемых преллагаеь1Ым устройством ошибок равно

л. - .(yn-lV-J , -vy, а -г

Для рассмотренного выше примера и1--1 7, at,71 10- Из этого следует, что пре;.длагаемое устроЙ ство -PLO сравнению с известнЕлм исправляет больше ошибок, следовательно, оно уменьшает вероятность ошибочного приема, т.е. его помехЬустойчивость выше.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Финн Л.М | |||

| Теория передачи дискретных -сообщений | |||

| М., Сов | |||

| радио, 1970, с | |||

| СПОСОБ ЭЛЕКТРИЧЕСКОЙ ПЕРЕДАЧИ ИЗОБРАЖЕНИЙ ПРИ ПОМОЩИ СИСТЕМЫ ПАРАЛЛЕЛЬНЫХ ПРОВОДОВ | 1921 |

|

SU636A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для мажоритарного декадирования двоичных кодов | 1974 |

|

SU497729A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-09-30—Публикация

1982-06-10—Подача