4

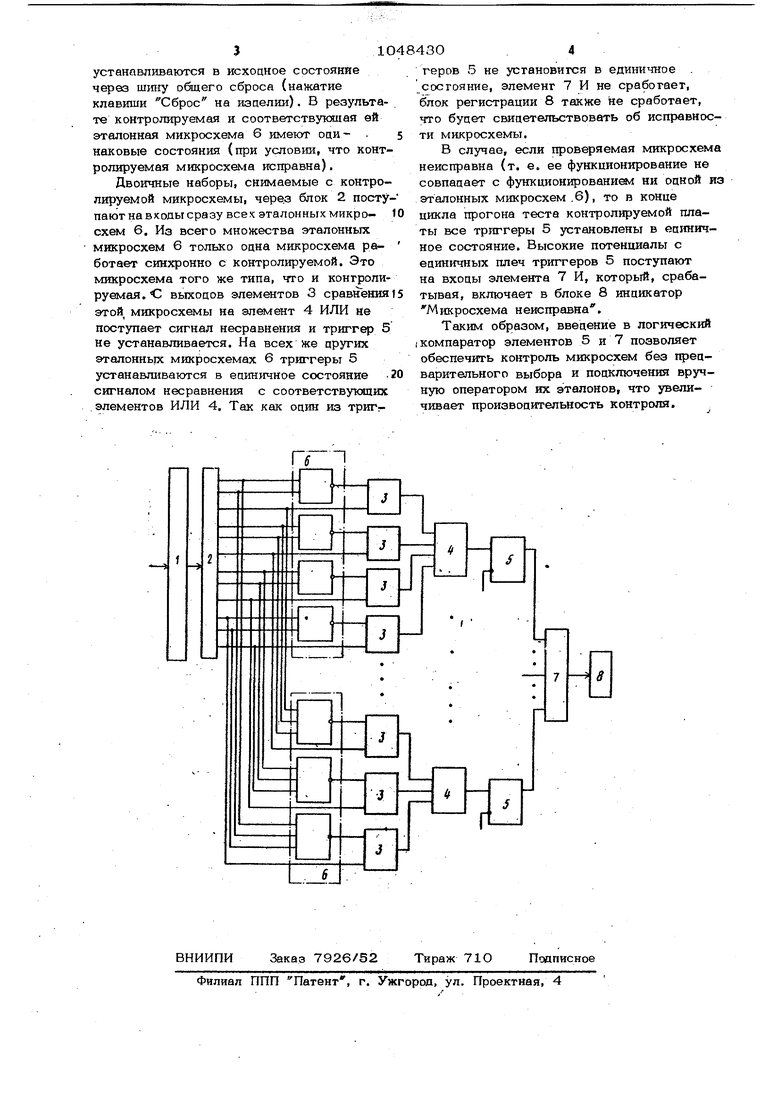

СХ) 4 СО 110 Изобретение относится к контрольно.измерительной технике, в частности, к контролю и циагносткке рапиоэлектронных изцелий. Известно устройство цля контроля цифровых микросхем, содерйсащее контактирующий зона, элементы сравнения, блок, инцикации и гнезао цля съемной эталонной микросхемы l . Недостатком указанного устройства является низкая производительность, поскольку при контроле одной платы необходимо несколько раз (5-10) менять эталонные микросхемы в гнезде. Кроме того наличие подвижного контшста эталонная микросхема - гнездо снижает надежность устройства, а участие в выборе эталонной микросхемы оператора снижает досто верность контроля. Наиболее близким техническим решением к изобретению является логический компаратор для контроля цифровых схем, содержащий блок регистрации, контактиру ющий блок, соединенный вхоаами с первы ми входами устройства, выходами - с входами блока развязывающих усилителей соединенного первыми выходами с соответствующими входами эталонных микросхем различных типов, вьпсоды каждой из которых соединены с первыми входами соответствующих элементов сравнения, соединенных вторыми входами с соответствующими выходами блока развязывающи усилителей, выходами - с входами соответствующего данной эталонноЙ микросхеме элемента ИЛИ . Недостатком известного компаратора является низкая производительность, что обусловлено потерями времени на многократное (10-15 раз) переключение тумблеров для выбора эталонных микросхем при больщом числе их типов. - : Цель изобретения - повьпиение производительности контроля. Поставленная цель постигается тем, что в логический компаратор цля контроля цифровых схем, содержащий блок реги рации, контактирующий блок, соединенный входами с первыми входами логического компаратора, выходами - с входами блока развязывающих усилителей, соедине ного первыми выходами с соответствующими входами эталонных микросхем, выходы каждой из которых соеаинены с пер выми вхоаами соответствующих элементо сравнени соединенных вторыми восодами с с ответствукяпимн выходами блока развязыва ющих усш1игелей,выходамн - входами 3О оответствующего данной эталонной микрохеме элемента ИЛИ, введены по числу эталонных микросхем триггеры и элемент И, соединенный выходом с входом блока егистрации, входами - с выходами соответствующих триггеров, соединенных первыми входами с выходами соответствуюих элементов ИЛИ, вторыми входами вторым входом логического компаратоа.. На чертеже, приведена блок-схема ло-. гического компаратора. Логический компаратор содержит конактирукяций блок I, блок 2 развязыв1аюих усилителей, элементы 3 сравнения, элементы ИЛИ 4, триггеры 5, эталонные икросхемы 6, элемент 7 И, блок 8 регитрации. Логический компаратор работает следующим образом. Контактирующий блок I (зонд) надевается на проверяемую цифровую микросхему, которая запаяна в логической плате (блоке и т, п.). Затем запускается контактирующий тест для данной платы. Генератором тестов может быть устройство тестового контроля (на не показа|но) с заранее составленными конгрси1Ирук идими программами. Если таких программ нет, пользуются сигналами с разъема готового изделия, заменив в нем соответствую- / щую исправную плату на контролиругалую. Для этого плату устанавливают в разъем изделия через переходной удлинитель и запускают изделие в работу. На выходы проверяемой платы поступают рабочие двоичные наборы, являющиеся в данном I случае тестовыми контролируемыми наборами. Соответственно, на входы контролируемой в данный момент микросхемы пос-, тупают двоичные наборы как производные входньк на боров платы. Блок I обеспечивает съем сигналов, которые поступают на , вход блока 2 развязывающих усилителей, которые служат для уменьщеншГ нагрузки .на проверяемую цифровую микросхему. I Сигналы с / выходов блока 2 поступают на эталонные микросхемы 6. Предлагаемь1й кст паратор не цепвет различий межцу комбинационной к послецовательной микросхемой так как , тестовым набором контролируемая и подключенная к кеА через блок, эталонная мккроск&ла 6 устанавливается в одинаковое исходное состояние. Если контроль логической платы вьшолняется не реальном нздепин через переходник, то все ее послецовательнгае микросхемы

устанавливаются в исхоцное состояние через mmiy общего сброса (нажатие клавиши Сброс на иэпелии). В результате контролируемая и соответствующая ей эталонная микросхема 6 имеют оци- . 5 наковые состояния (при условии, что контролируемая микросхема исправна).

Двоичные наборы, снимаемые с контролируемой микросхемы, чере.3 блок 2 поступают на вкоды сразу всех эталонных микро- 10 схем 6. Из всего множества эталонных микросхем 6 только одна микросхема работает синхронно с контролируемой. Это микросхема того же типа, что и контролируемая, С выходов элементов 3 сравнения 15 этой микросхемы на элемент 4 ИЛИ не поступает сигнал несравнения и триггер 5 не устанавливается. На всех же других эталонньпс микросхемах 6 триггеры 5 устанавливаются в единичное состояние .20 сигналом несравнения с соответствукяцих . элементов ИЛИ 4. Так как один из тригГГ

геров 5 не установится в единичное . состояние, элемент 7 И не сработает, блок регистрации 8 также не сработает, что будет свидетельствовать об исправности микросхемы,

В случае, если проверяемая микросхем неисправна (т. е, ее функционирование не совпадает с функционированием ни одной и эталонных микросхем .6), то в конце цикла прогона теста контролируемой платы все триггеры 5 установлены в единичное состояние. Высокие потенциалы с единичных плеч триггеров 5 поступают на входы элемента 7 И, который, срабатывая, включает в блоке 8 индикатор Микросхема неисправна.

Таким образом, введение в логический (Компаратор элементов 5 и 7 позволяет обеспечить контроль микросхем без тфедварительного выбора и подктпочения вручную оператором их эталонов, что увеличивает производительность контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа выходных реакций контролируемой цифровой схемы | 1986 |

|

SU1429117A1 |

| Логический компаратор для контроля цифровых микросхем | 1977 |

|

SU702502A1 |

| Устройство для контроля цифровых объектов | 1986 |

|

SU1319037A2 |

| Устройство для контроля интегральных микросхем | 1982 |

|

SU1056089A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Трехфазное устройство для контроля релейной защиты (его варианты) | 1981 |

|

SU1000939A1 |

ЛОГИЧЕСКИЙ КОМПАРАТСЯР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ, 00ц жащий блок регистреции, контактирующий блок, соединенный вхоаами с первыми входами логического компаратора, выхоцамн - с входами блока развязывающих усилителей, соединенного первыми выходами с соответствукяцими входами эталонных микросхем, выходы каждой из , : которых соединены с входами соответствутдщих элементов сравнения, соединенньпс вторыми входами с соответствующими выходками блока развязьюающих усилителей, выходами - с Еосодами соответствующего данной эталонной микросхеме элемента ИЛИ, отличающийся тем, что, с целью повышения производительности контроля, в него ввеаены по числу эталонных микросхем триггеры .и. элемент И, соецнненный выходом с входом блока регистрашга, вхоаами - с выходами соответствующих триггеров, соёдннеквых первыми входами с s выходами соответствукших элементов ИЛИ, вторыми вхоаами - с втсфым вхоСО пом погическсяо компаратора...

| I | |||

| Аллеи Д | |||

| Р | |||

| Логический тестер | |||

| цля аифровых интегральных схемных плат | |||

| - Электроника, 1973, Jsfe 23, с | |||

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свицетельство СССР кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-10-15—Публикация

1982-05-20—Подача