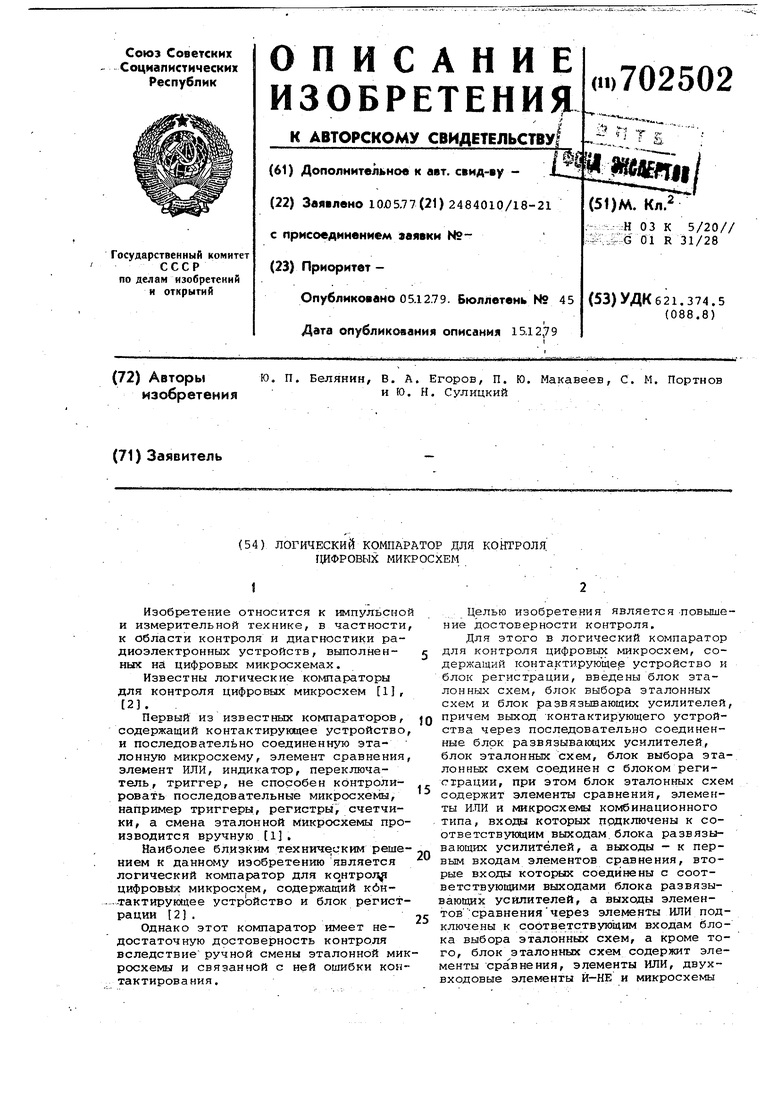

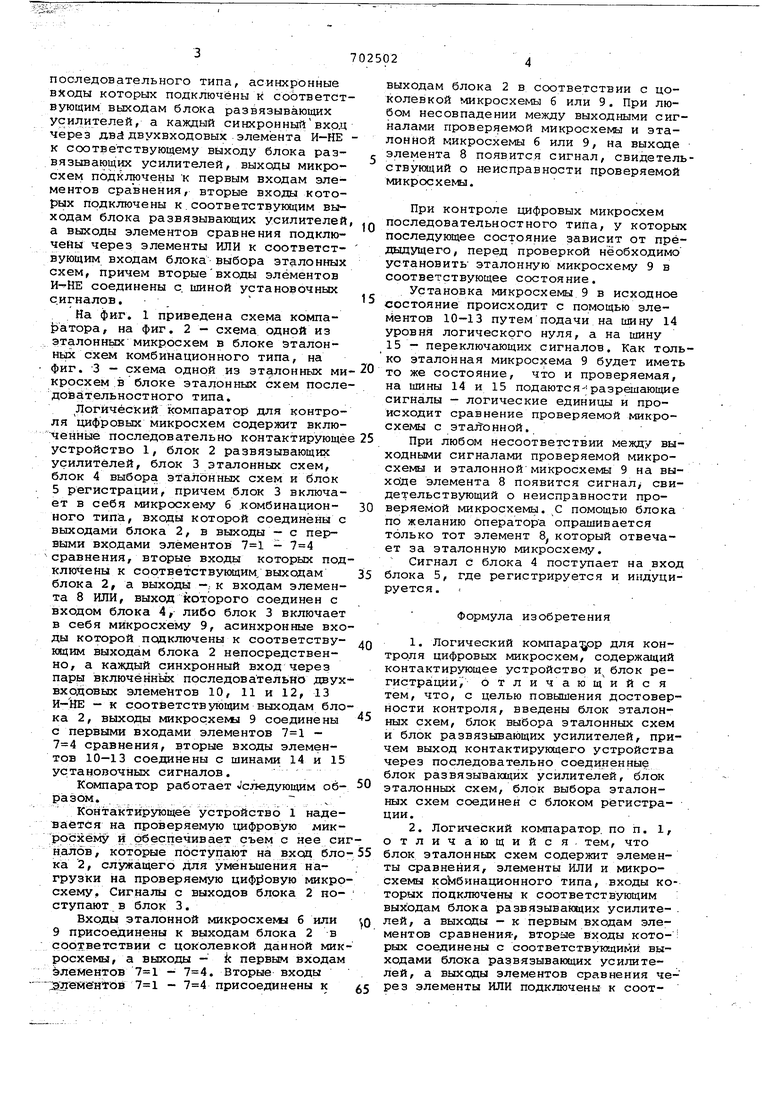

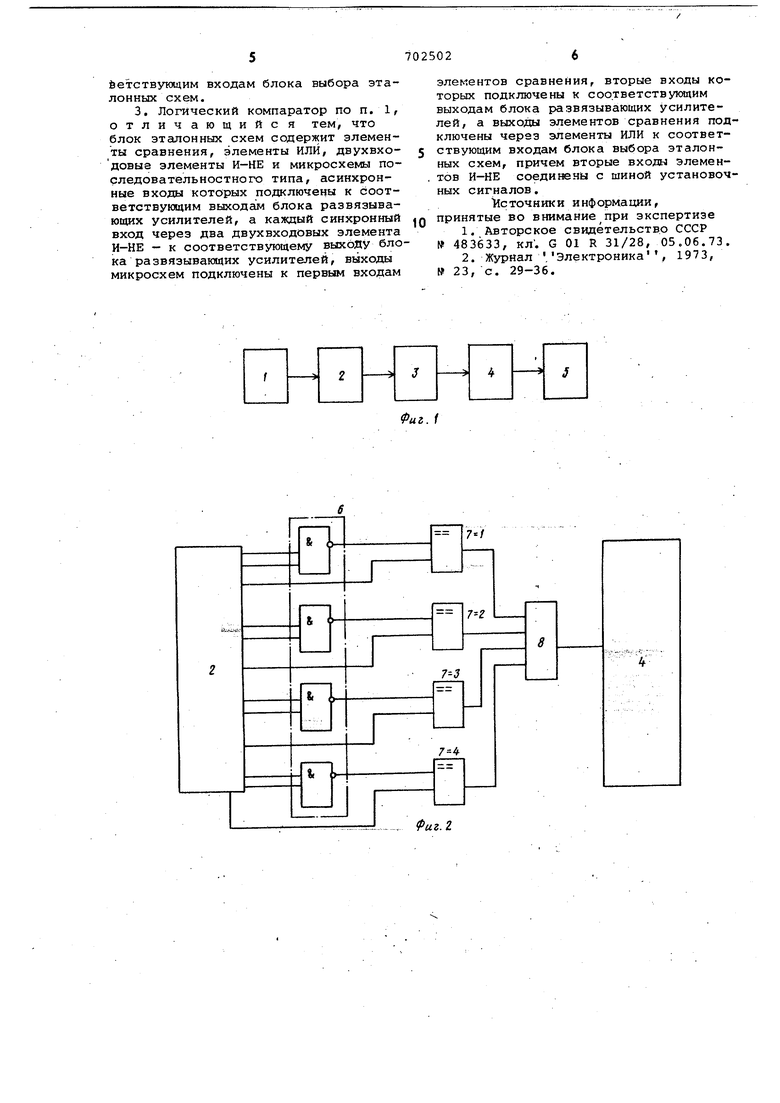

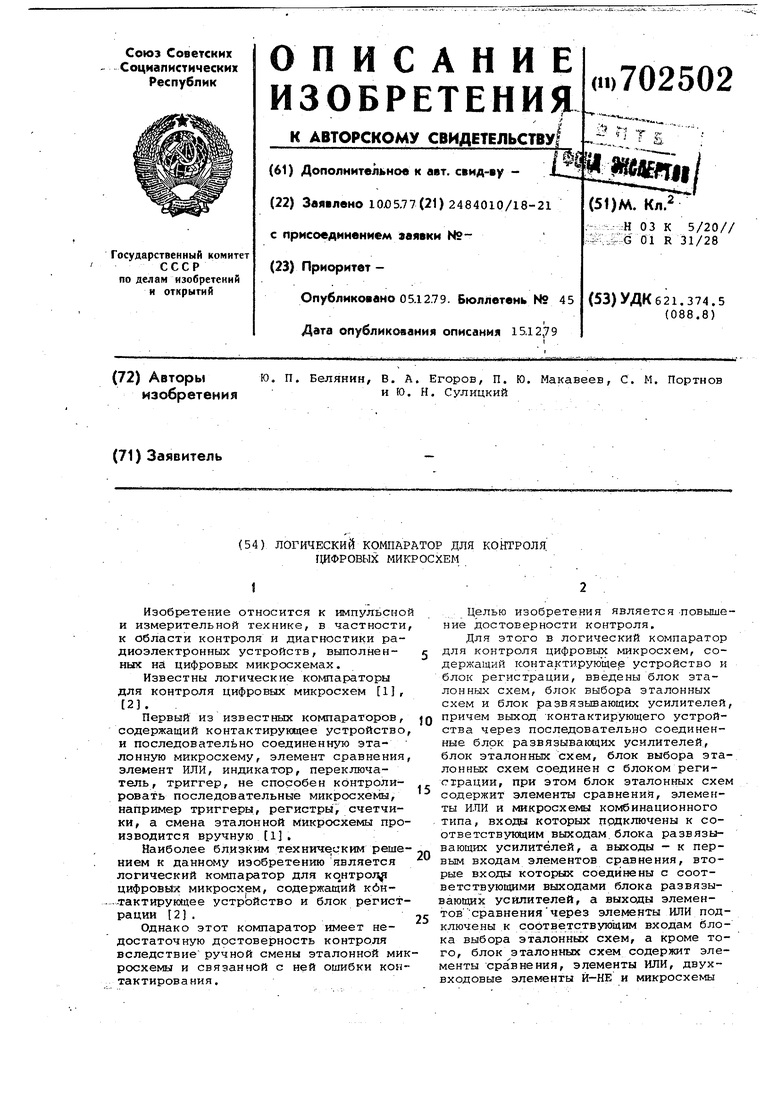

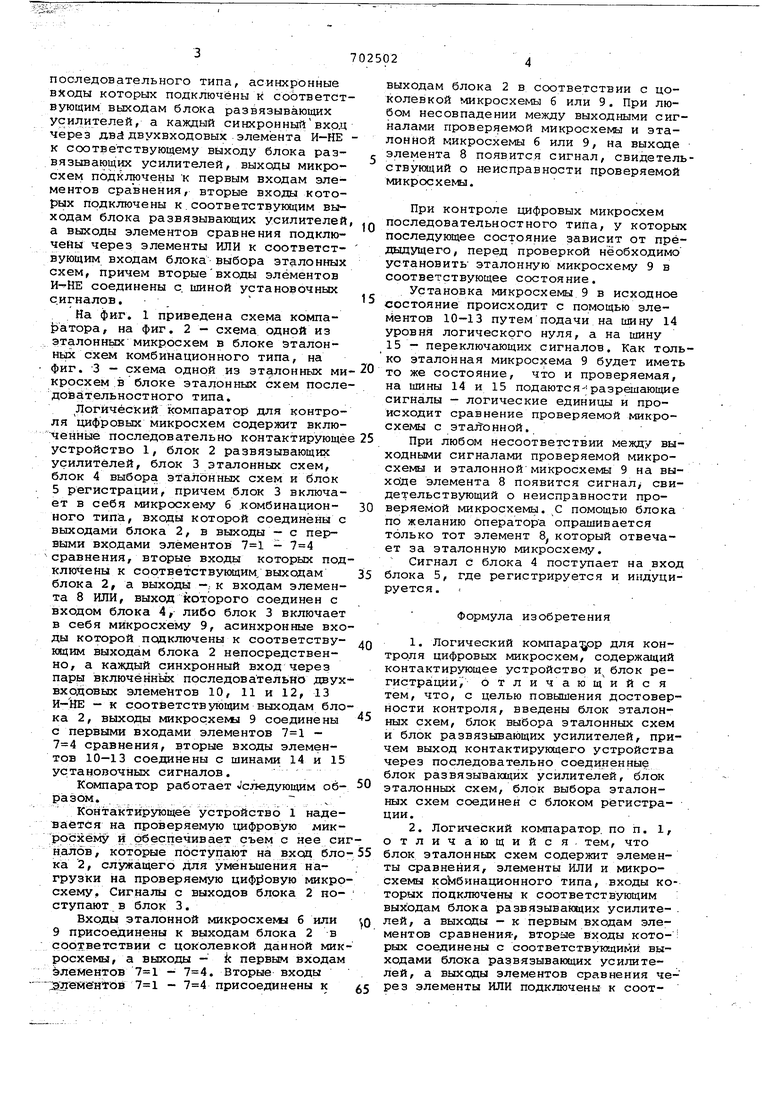

(54) ЛОГИЧЕСКИЙ КОМПАРАТОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ МИКРОСХЕМ последовательного типа, асинхронные входы которых подключены к соответст вующим выходам блока развязывающих усилителей, а каждый синхронныйвход через два двухвходовых элемента И-НЕ к соответствующему выходу блока развязывающ1« усилителей, выходы микросхем подключены К первым входам элементов сравнения, вторые входы которых подключены к.соответствующим выходам блока развязывающих усилителей а выходы элементов сравнения подключены через элементы ИЛИ к соответствующим входам блока выбора эталонных схем, причем вторыевходы элементов И-НЕ соединены с, шиной установочных с.игналов. На фиг. 1 приведена схема компаратора, на фиг. 2 - схема одной из эталонных микросхем в блоке эталонных схем комбинационного типа, на фиг. 3 - схема одной из эталонных ми кросхем ; в блоке эталонных схем после дова1тельностного типа. Логический компаратор для контроля цифровых микросхем содержит включейныё последовательно контактирующе устройство 1, блок 2 развязывающих усилителей, блок 3 эталонных схем, блок 4 выбора эт алонных схем и блок 5 регистрации, причем блок 3 включает в себя микросхему б .комбинационного типа, входы которой соединены с выходами блока 2, в выходы - с первыми входами элементов - сравнения, вторые входы которых под к соответствукадим, выходам блока 2, а выходы -. к входам элемента 8 ИЛИ, выход Которого соединен с входом блока 4, либо блок 3 включает в себя микросхему 9, асинхронные вхо ды которой подключены к соответствующим выходам блока 2 непосредственно, а каждый синхронный вход череэ пары включённых последовательно двух входовых элементов 10, 11 и 12, 13 И-НЕ - к соответствующим выходам бло ка 2, выходы микросхема 9 соединены с первыми входами элементов сравнения, вторые входы элементов 10-13 соединены с шинами 14 и 15 установочных сигналов. Компаратор работает ./следующим об разом. Контактирующее устройство 1 надева:ется на проверяемую цифровую микросхему и обеспечивает съем с нее си налов, которые поступают на вход бло ка 2, служащего для уменьшения нагрузки на проверяемую циф13овую микро схему. Сигналы с выходов блока 2 поступают в блок 3. Входы эталонной микросхе 1 б или 9 присоединены к выходам блока 2 в соответствии с цоколевкой данной мик росхемы, а выходы - k первым входам Элементов - . Вторые входы 3fef e№fOB - присоединены к выходам блока 2 в соответствии с цоколевкой микросхемы 6 или 9. При любом несовпадении между выходными сигналами проверяемой микросхемы и эталонной микросхемы б или 9, на выходе элемента 8 появится сигнал, свидетельствующий о неисправности проверяемой микросхемы. При контроле цифровых микросхем последовательностного типа, у которых последующее состояние зависит от предыдущего, перед проверкой необходимо установить эталонную микросхему 9 в соответствующее состояние. Установка микросхемы 9 в исходное состояние происходит с помощью элементов 10-13 путем подачи на шину 14 уровня логического нуля, а на шину 15 - переключающих сигналов. Как только эталонная микросхема 9 будет иметь то же состояние, что и проверяемая, на шины 14 и 15 подаются-разраиающие сигналы - логические единицы и происходит сравнение проверяемой микросхемы с эталтонной. При любом несоответствии между выходными сигналами проверяемой микросхемы и эталонной микросхемы 9 на выходе элемента 8 появится сигнал/ свидетельствующий о неисправности проверяемой микросхемы. С помощью блока по желанию оператора опрашивается только тот элемент 8 который отвечает за эталонную микросхему. Сигнал с блока 4 поступает на вход блока 5, где регистрируется и индуцируется. Формула изобретения 1.Логический компарат ор для контроля цифровых микросхем, содержащий контактирующее устройство и блок регистрации, отличающийс я тем, что, с целью повышения достоверности контроля, введены блок эталонных схем, блок выбора эталонных схем и блок развязывающих усилителей, причем выход контактирующего устройства через последовательно соединенные блок развязывающих усилителей, блок эталонных схем, блок выбора эталонных схем соединен с блоком регистрации. 2.Логический компаратор, по п. 1, о тлич ающийс я, тем, что блок эталонных схем содержит элементы сравнения, элементы ИЛИ и микросхемы комбинационного типа, входы которых подключены к соответствующим выхЪдам блока развязывающих усилите- . лей, а выходы - к первым входам элементов сравнения-, вторые входы кото- : рых соединены с соответствующими выходами блока развязывающих усилителей, а выходы элементов сравнения через элементы ИЛИ подключены к соотйетствующим входам блока выбора эталонных схем.

3. Логический компаратор по п. 1, отличающийся тем, что блок эталонных схем содержит элементы сравнения, элементы ИЛИ, двухвходовые элементы И-НЕ и микросхемы последовательностного типа, асинхронные входы которых подключены к соответствующим выхода1М блока развязывающих усилителей, а казкдый синхронный вход через два двухвходовых элемента И-НЕ - к соответствующему выходу блока развязывающих усилителей, выходы микросхем подключены к первым входам

элементов сравнения, вторые входы которых подключены к соответствующим выходам блока развязывающих усилителей, а выходы элементов сравнения подключены через элементы ИЛИ к соответствующим входам блока выбора эталонных схем, причем вторые входы элементов И-НЕ соединены с шиной установочных сигналов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 483633, кл; G 01 R 31/28, 05,06.73.

2.Журнал ,Электроника, 1973, 23, с. 29-36.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический компаратор для контроля цифровых схем | 1982 |

|

SU1048430A1 |

| Устройство для анализа выходных реакций контролируемой цифровой схемы | 1986 |

|

SU1429117A1 |

| Устройство для контроля узлов электронных вычислительных машин | 1976 |

|

SU667969A1 |

| Устройство для контроля интегральных схем | 1981 |

|

SU1029146A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля микросхем | 1985 |

|

SU1322289A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

| Устройство логического и допускового контроля | 1980 |

|

SU875313A1 |

| Способ косвенного измерения отказоустойчивости облучаемых испытательных цифровых микросхем, построенных способом постоянного резервирования, и функциональная структура испытательной микросхемы, предназначенной для реализации этого способа | 2020 |

|

RU2756577C1 |

| Устройство для контроля микросхем | 1990 |

|

SU1758610A1 |

Фиг.г

Авторы

Даты

1979-12-05—Публикация

1977-05-10—Подача