ьо

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический компаратор для контроля цифровых схем | 1982 |

|

SU1048430A1 |

| Асинхронное автоматическое устройство для контроля цифровых систем | 1989 |

|

SU1751761A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1363212A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для функционального контроля логических элементов | 1984 |

|

SU1226468A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

Изобретение относится к коит- рольио-измерительной техиике и предназначено для контроля цифровых интегральных схем с ко1 инациоиной 4 внутренней структурой в составе логических, плат. Цель - повышение достоверности анализа. Устройство содержит контактирутаций блок 1, подключенный ко всем выводам цифровой микросхемы, выходы которого соединены с входами:: блока 2 развязывающих усилителей, выходы которого соединены с адресными 1входами блока 3 памяти и входами блока 4 формирования стробирующего сигнала, выход которого соединен с входом синхронизации чтения блока 3 памяти, а выходы блока 3 связаны с соответствующими входами блока 6 регистрации. Чтение реакций происходит только поспе перехода контролируемой схемы в установившийся режим. 1 З.П. ф-ЛЫ, 3 Ш1... со JU

Л

9ja.t

;1U

I Изобретение относится к контроль- о-измерительной технике и предназначено для контроля цифровых интеграль мых схем с комбинационной внутренней структурой в составе логических плат.

Цель изобретения - повышение достоверности анализа.

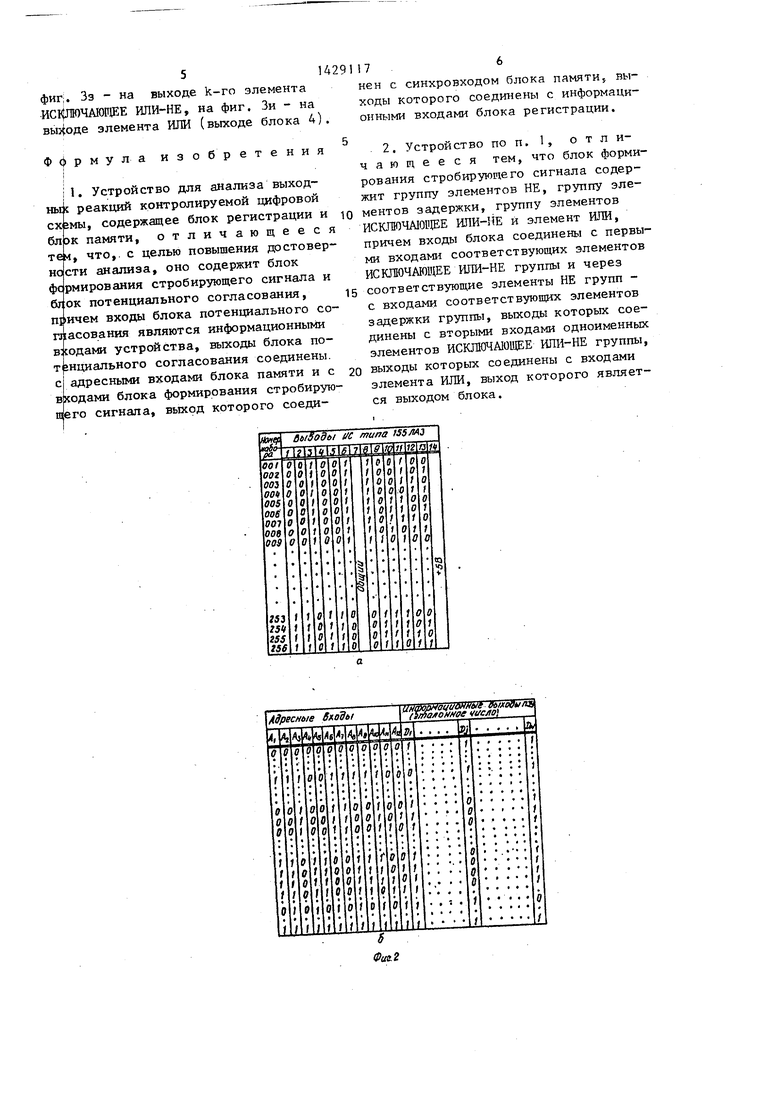

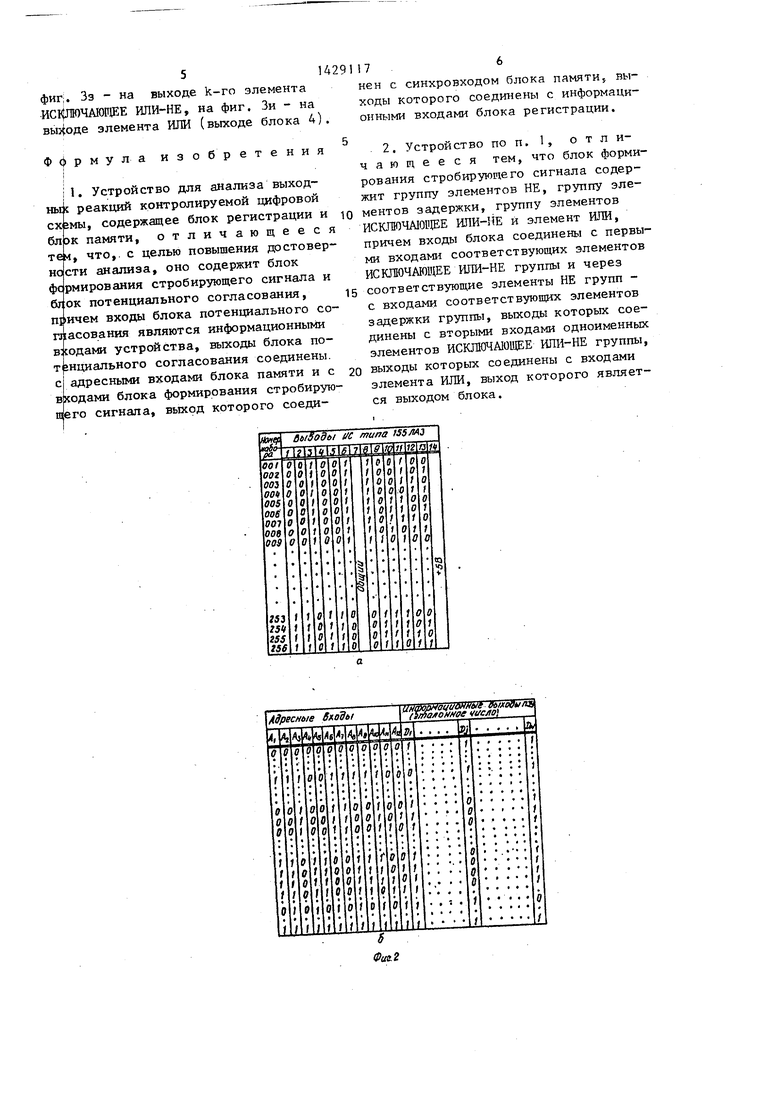

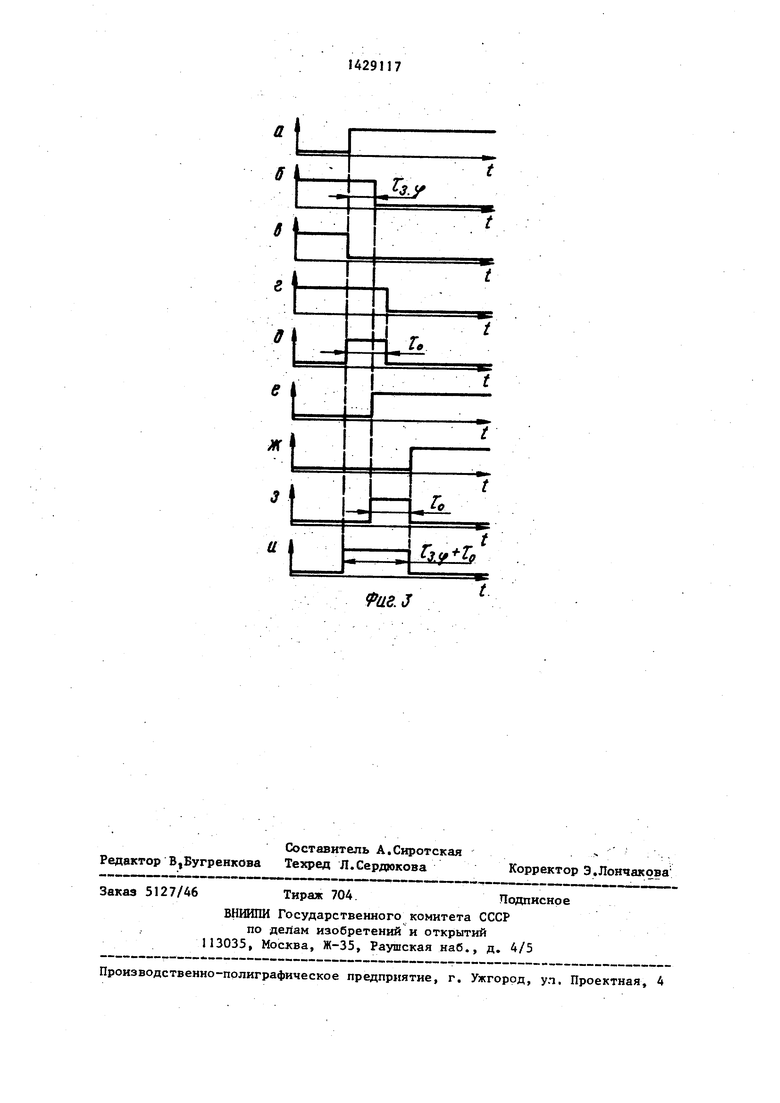

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - пример организации записи эталонной информации в блоке памяти; на фиг. 3 - временные диаграммы работы устройства .

Устройство (фиг. 1) содержит блок потенциального согласования, образованный контактирующим блоком 1 и блоком 2 развязьшающих усилителей, блок 3 памяти, блок 4 формирования строби- рУющего сигнала, группу триггеров 5j блок 6 регистрации, элемент 7 индикации, элемент И 8, элемент ИЛИ 9, группу элементов ИСКЛОЧА1011ЩЕ ИПИ-НЕ 10, группу элементов 11 задержки, группу элементов НЕ 12.

В блоке 3 записана информация в виде N-разрядных двоичных слов. (Число разрядов N слов, хранящихся в бло- ке 3, соответствует числу типов схем, эталонная информация о которых запи- сана в блоке 3). Номер j разряда слова, считываемого из блока 3, при любом адресном наборе соответствует .информации о каком-либо определенном .типе цифровой схемы.

Информация в блоке 3 записана в со ответствии с таблицами истинности дпя всех N типов проверяемых схем. При этом, если двоичньй набор, снимаемый с входов и выходов какой-либо контро- лируемой j схемы, соотйетствует таблице истинности для этого типа микросхем, то по адресу блока 3, соответствующему двоичному набору на выводах схемы в j-й разряд N-разрядного двоич ного слова, записан логический О, в противном азучае в j-й разряд N- разрядного слова записана логическая

и и

.

На фиг. 2 приведен пример организации записи эталонной информации дпя микросхемы типа 155IIA.3. При этом на фиг. 2а представлена таблица истинности для микросхемы 155 ЛАЗ. На основании этой таблицы в блок 3 записана информация в J-e разряды N-разрядных эталонных слов. В разряд Dj N-pas рядного эталонного числа, соответствующий микросхеме 155 ЛАЗ, записан ло

91

ц

5 0 . 5

0

Q с

5

0

П2

гический О, если двоичный набор на адресных входах А,...,АГ, блока 3 соответствует таблице истинности для этого типа . .микросхемы. В противном случае в разряд Dj записана логическая I. В остальные разряды D,...,I, (кроме DJ ) эталонного числа записаны логические 1, если двоичный набор на адресных входах А,...,А не соответствует таблицам истинности набора типов микросхем 1,...,N и логические О - в противном случае.

Устройство производит контроль функционирования N типов ци1Й)овых микросхем, имеющих комбинационную внутреннюю структуру (например, микросхемы, содержащие элементы И, ИЛИ, И-НЕ, дешифраторы, шифраторы, мультиплексоры, сумматоры и т.п.), непосредственно в составе работающей логической платы.

Последовательность входных и выходных сигналов контролируемой схемы при прохождении контролирующего теста для данной логической платы, (или при прохождении рабочей последовательности на входах логической платы) снимается посредством контактирующего блока 1 с выводом схекы и передается на входы блока 2 развязы - вающих усилителей, служащего для снижения нагрузки на проверяемую микросхему. Выходы блока 2 развязывающих усилителей имеют нумерацию в соответствии с цоколевкой проверяемой мик-. росхемы. С выходов блока 2 развязывающих усилителей последовательность двоичных наборов на входах и выходах контролируемой микросхемы передается на адресные входы блока 3 и на входы блока 4. Число адресных входов блока 3 соответствует числу выводов контролируемой микросхемы.

Чтение эталонного числа из ячейки блока 3, адрес которой соответствует двоичному набору на входах и выходах контролируемой схемы, происходит по спаду Сигнала, поступающего с выхода блока 4 на вход синхронизации чтения блока 3..

В случае, если контролируемая микросхема j-го типа исправна, то по адресам блока 3, соответствующим двоичным наборам на входах и выходах .контролируемой схемы, считьшаются N- . разрядные двоичные слова, в N-M разряде которых постоянно присутствует логический О. Следовательно, на

31

вход соответствующего j-ro триггера 5 блока 6 регистрации не поступает ни одного сигнала логической I и триггер 5 не устанавливается в единичное состояние. Все остальные триггеры 5 устанавливаются в единичное состояние сигналами уровня логической 1 с соответствующих разрядов информационных выходов блока 3. Ввиду того, что один из триггеров 5, а именно триггер, соединенный с j-м информационным выходом блока 3, не устанавливается в единичное состояние, элемент И 8 не срабатывает н не передает сигнал в элемент 7 индикации, что и .свидетельствует об исправности контролируемой ,

В случае неисправности контролируемой схемы J-ro типа на адресных входах блока 3 появляются двоичные наборы, не соответствующие таблицам истинности ни одной из N типов схем. Из ячеек блока 3, адреса которых соответствуют двоичным наборам на входах и выходах контролируемой схе- , считыв яются N-разрядные слова, в каждом разряде которых, хотя бы по одному адресу, присутствуют сигналы уровня логической 1. Следовательно все триггеры 5 устанавливаются за врмя .прохождения контролирующего теста в единичное, состояние сигналами уровня логической I с соответствующих информационных выходов блока 3. Так как все триггеры 5 устанавливаются в единичное состояние, срабатывает элемент И 8, и сигнал передается на элемент 7 индикации, который зафиксирует факт неисправности проверя емой схемы.

Сигнал, поступающий на-вход синхронизации чтения блока 3, вырабатывается блоком 4 при каждом изменении двоичного набора на входах и выходах контролируемой схемы, т.е. при каждом лерепаде логических уровней хотя бы на одном из входов или выходов проверяемой цифровой схемы,

.

При этом учитывается, что каждая

цифровая схема из набора (l,...,N) типов микросхем имеет внутреннюю задержку срабатывания (т.е. задержку изменения информации на выходе по отношению к изменению информации на входах микросхемы),зависящую от многих факторов, но имеющую ограничения по максимуму в соответствии с

1

Q 5

0 5 о о

g

0

g

5

17

техническими условиями на данный тип микросхем.

Естественно, при прямой подаче сигналов с выводов контролируемой цифровой микросхемы на адрес№1е входы блока 3 может возникнуть некорректная ситуация, когда входной набор контролируемой схемы изменился, а выходная реакция на выходах микросхемы еще не появилась. Поэтому чтение эталонных N-разрядных слов из блока 3 допжно происходить только после появления на входах и выходах схем установившегося логического состояния.

Последовательность двоичных кодов с входов и выходов контролируемой микросхемы через контактирующий блок J и блок 2 развязывающих усилителей поступают на входы элементов НЕ 12 блока 4 и на входы элемектов ИСКПЮ- ЧАЩЕЕ ИПРЬНЕ 10, на первые входы которых поступают через элементы i1 задержки сигналы с выходов элементов 12. Каждое изменение уровня сигнала на входе какого-либо 1-го элемента 12 вызывает его срабатывание и изменение сигнала ,на выходе, который через элемент 1I задержки поступает ка вход элемента ИСКЛЮЧАЮЩЕЕ 1ШИ-НЕ JC В результате сигнал на входе эламен- та ИСКЛОЧАЮР1ЕЕ ИЛИ-НЕ 10 изменяется с опозданием на время Т относитель- но изменения уровня сигнала на дру- . гом входе этого элемента, и на вь;хо- де элемента ИСКЛОЧАИЦЕЕ ИЛ И-НЕ 10 сформируется положительный импульс длительностью То . Длительность импульса Г о должна удовлетворять условию Ti ;- .мосо Я Г.ср.мдкс - максимальное время задержки срабатывания для микросхем из группы N типов, информация о которых записана в блоке 3..

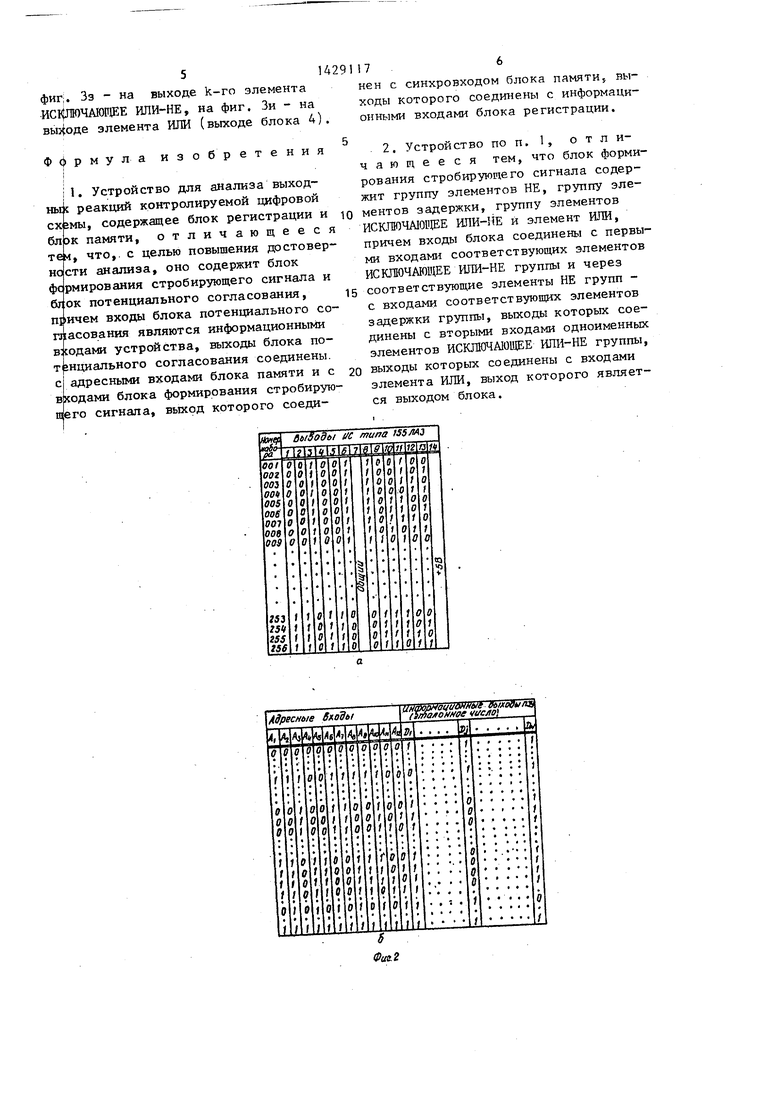

Процесс формирования стробирующих импульсов поясняется временными диаграммами (фиг. 3), где на фиг. За приведена временная диаграмма сигнала на i-M входе контролируемой цифровой схемы, на фиг. 36 - на k-м выходе контролируемой схемы, на фиг.Зв- на выходе соответствующего i-ro инвертора, на фиг. Зг - на первом входе 1-го элемента ИСКПЮЧАЮРЕЕ ИЛИ-НЕ, на фиг. Зд - на выходе i-ro элемента ИСКЛЮЧАЮЩЕЕ ШШ-НЕ, на фиг. Зе - на выходе соответствующего k-ro элемента НЕ, на фиг. Зж - на первом входе k-ro элемента ИСКЛЮЧЛгаЦЕЕ ШШ-НЕ, на

фнг;. Зз - на выходе k-ro элемента ИСФТЮЧАЮЩЕЕ ИЛИ-НЕ, на фиг. Зи - на выходе элемента ИЛИ (выходе блока 4).

Формула изобретения

Щ1ичем входы блока потенциального согласования являются информационными вводами устройства, выходы блока по- т шциального согласования соединены. с адресными входами блока памяти и с входами блока формирования стробирую- шего сигнала, выход которого соеди.

14291176

ней с синхровходом блока памяти, выходы которого соедт ены с информационными входами блока регистрации.

лг J

| Устройство для контроля цифровых блоков | 1978 |

|

SU746553A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| АНАЛИЗА ВЫХОДНЫХ РЕАКЦИЙ КОНТРОЛИРУЕМОЙ ЦИФРОВОЙ СХЕМЫ | |||

Авторы

Даты

1988-10-07—Публикация

1986-11-18—Подача