Изобретение относится к импульсной технике, в частности к устройст вам для контроля источников электри ческих сигналов, и может быть использовано для контроля работоспосо ности и допускового контроля аналог вых устройств. Известна система контроля аналог вых сигналов, содержащая ЦВМ, блок преобразования аналог-код, блок сопряжения. Информация, полученная после преобразования аналог-код, сравнивается в. ЦВМ с номинальными значениями, заранее записанными в ДЗУ. По результатам сравнения ЦВМ осуществляет оценку общей работоспособности контролируемых устройст а При выходе за пределы допусков одного или нескольких параметров ЦВМ по специальной подпрограмме осуществляет локализацию неисправности и устанавливает ее причину. Известная система контроля обладает высокими техническими характеристиками .. ; Недостатком известной системы является ее относительная сложность требующая больших аппаратурных затрат. Известно устройство для контроля источников сигналов, содержащее группу входных шин, два элемента И, два элемента НЕ, элемент ИЛМ, комму татор сигналов, счетчик, формироват управляющих сигналов, выходы счетчи ка соединены с адресными входами коммутатора сигналов, информационны входы которого соединены с группой входных шин и с выходом генератора, выход коммутатора сигналов соединен с первым входом первого элемента И и соединен через первый элемент НЕ с первым входом второго элемента И, выход формирователя управляющих сигналов соединен со вторым входом первого.элемента И и соединен через второй элемент НЕ со вторым входом вто|5ого элемента И, выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен со счетным входом счетчика. Известное устройство работает следующим образом. При исправной работе всех источников входных импульсов на информационные входы коммутатора сигналов поступают импульсы На выход коммутатора сигналов проходит импульс с информационного входа, разрешенного, соответствующей комбинацией двоичного кода, поступающего со счетчика.. С выхода коммутатора сигналов импульс через элемент И, открытый сигналом с формиро.вателя управляющих сигналов, и элемент ИЛИ поступает на счетный вход счетчи-. ка и наращивает информацию в нем i на единицу. При это на вход коммутатора сигналов подключается очередной контролируемый канал-. При отсутствии импульсов в контролируемом канале (уровень логического О или логической 1) счетчик не пере; ключится и его состояние буцет соот- ветствовать номеру отказавшего источника импульсов. В этом случае переключение счетчика производится сигналом, поступающим с формирователя управ1ляющих сигналов, которь)й. совпадает с постоянным уровнем на первом элементе И или на втором элементе И и через элемент ИЛИ пос;тупает на счётчик. При отсутствии неисправностей код на выходе счетчика меняется с частотой входных импульсов. На контрольный информационный вход коммутатора счетчиков поступают имп ульсы от генератора контрольного канала, причем частота им пульсов генератора контрольного канала во много раз ниже частоты входных контролируемых импульсов и определяет периодичность опроса контролируег«9 х каналов. Известное устройство выявляет неисправный канал только цифровых устройств 2 . Недостатком известного устройства является то, что.оно не позволяет выявить неисправный канал аналоговых устройств, а тем более локализовать неисправность взаимодействующих аналоговых устройств. Цель изобретения - обеспечение возможности локализации неисправности взаимодействующих аналоговых устройств. Указанная цель достигается тем, что в устройство для контроля источников сигналов, содержащее группу входных шин, элемент И, коммутатор сигналов, счетчик и формирователь управляющих сигналов, выходы счетчика соединены с адресными входами коммутатора сигналов, информационые входы которого соединены с групой входных шин, введены шина .управлеия, пороговый блок, блок (зменения

порога, дешифратор, регистр и блок анализа неисправностей, информационные входы которого соединены с выходами регистра, информационные входы которого соединены с выходами дешифратора, входы которого соединены с выходами счетчика шина управления соединена с первымвходом формирователя управляющих сигналов, второй вход которого соединен с дополнительным выходом счетчика выход коммутатора сигналов соединен с первым входом порогового блока, второй вход и выход,которого соединены соответственно с выходом блока изменения порога и с первым входом элементя И, выход которого оединен с первым управляющим входом регистра, первый, второй, третий, четвертый и пятый выходы формирователя управляющих сигналов соединены соответственно со счетным входом счетчика, со входом блока изменения порога, со вторым входом элемента И, со вторым управляющим входом регистра и с управляю-i щим входом блока анализа неисправностей .

В устройстве для контроля источников сигналов блок анализа неисправностей содержит группу элементов НЕ, элементы И-НЕ по количеству элементо НЕ, элемент ИЛИ, элемент ИЛИ-НЕ и три дополнительных элемента И-НЕ, выход элемента ИЛИ соединен с первыми входами элементов И-НЕ, вторые входы которых соединены через элементы НЕ с первой частью информационных входов блока анализа неисправностей, остальные информа14ионные входы которого соединены с остальными входами элементов И-НЕ, выходы которых соединены со входами элемента ИЛИ-НЕ и с первой группой выходных шин, выход элемента ИЛИ-НЕ соединен с первыми входами трех дополнительных элементов И-НЕ, вторые входы которых соединены соответст-венно с шинами управления и со входами элемента ИЛИ, выходы дополнител ных элементов И-НЕ соединены с дополнительными выходными шинами.

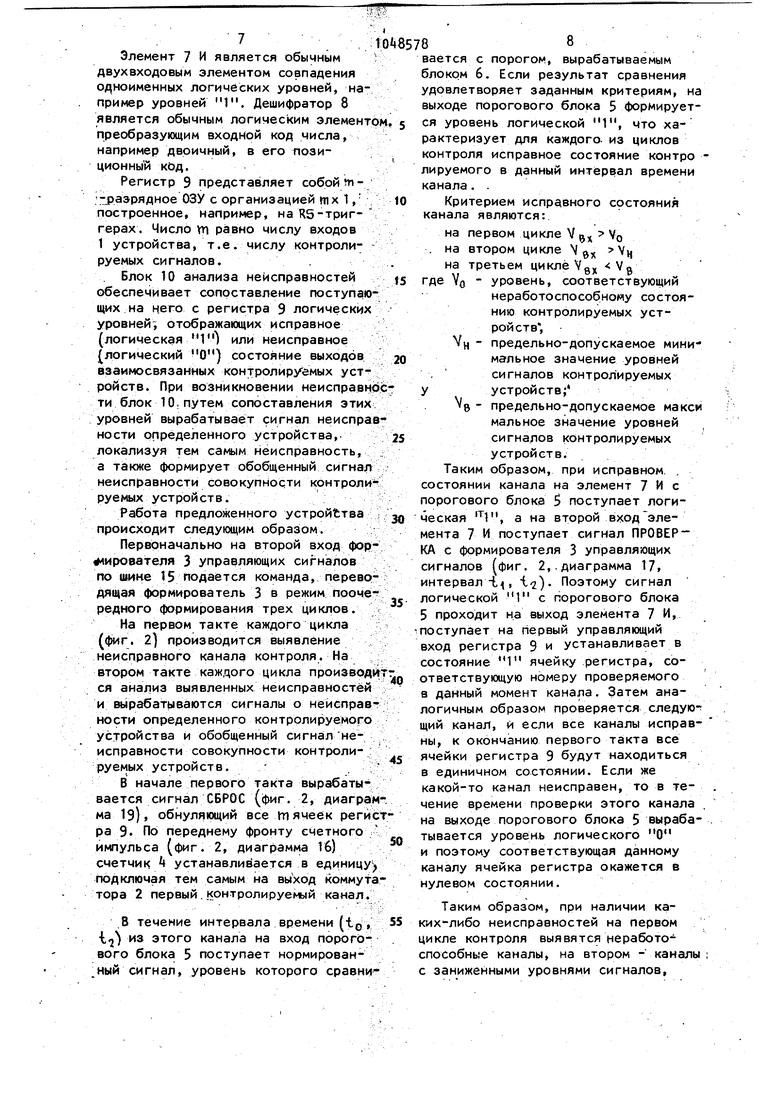

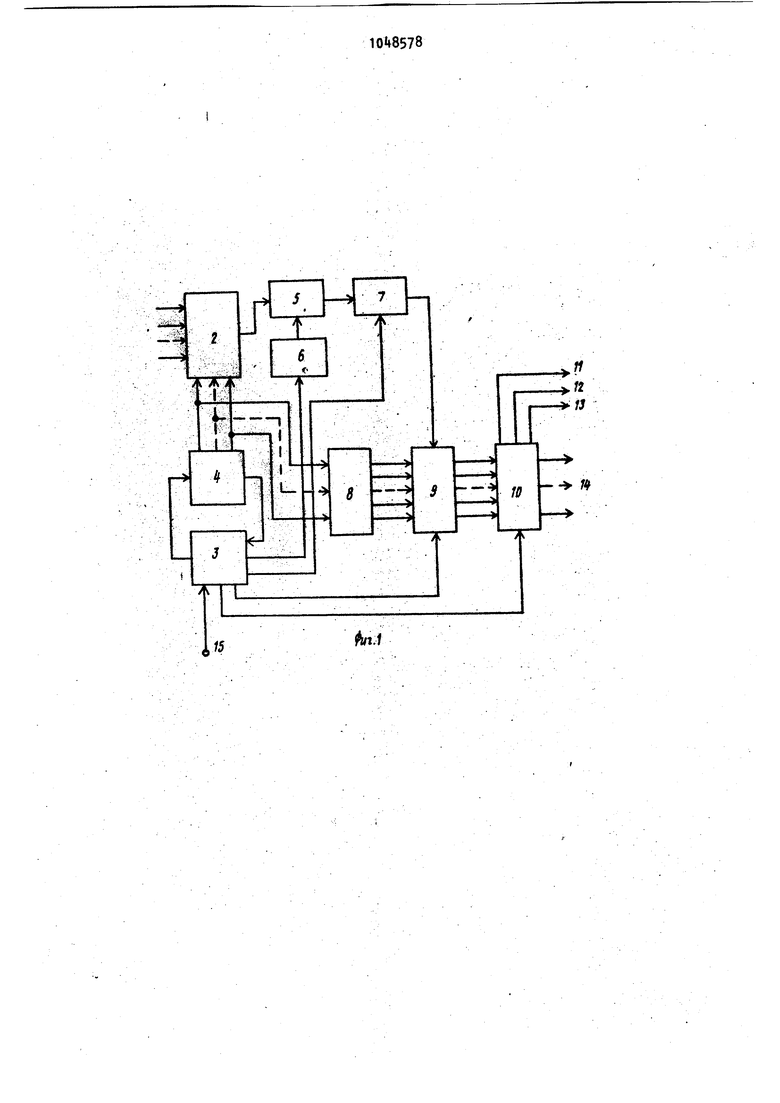

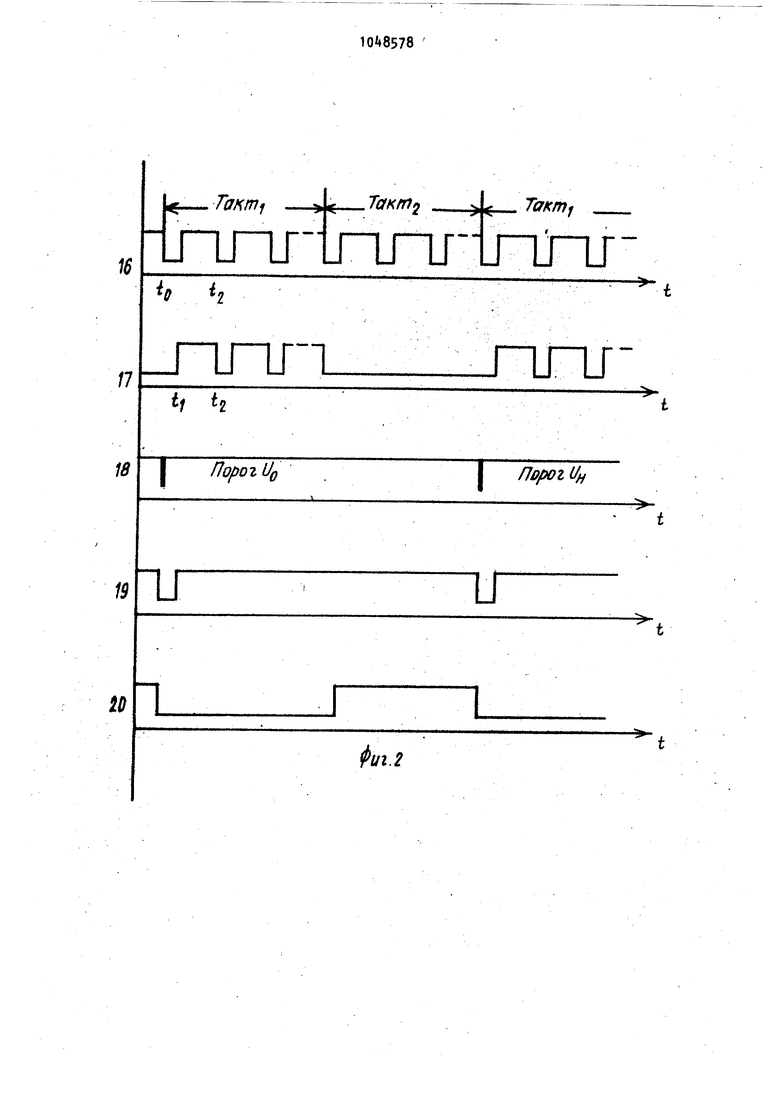

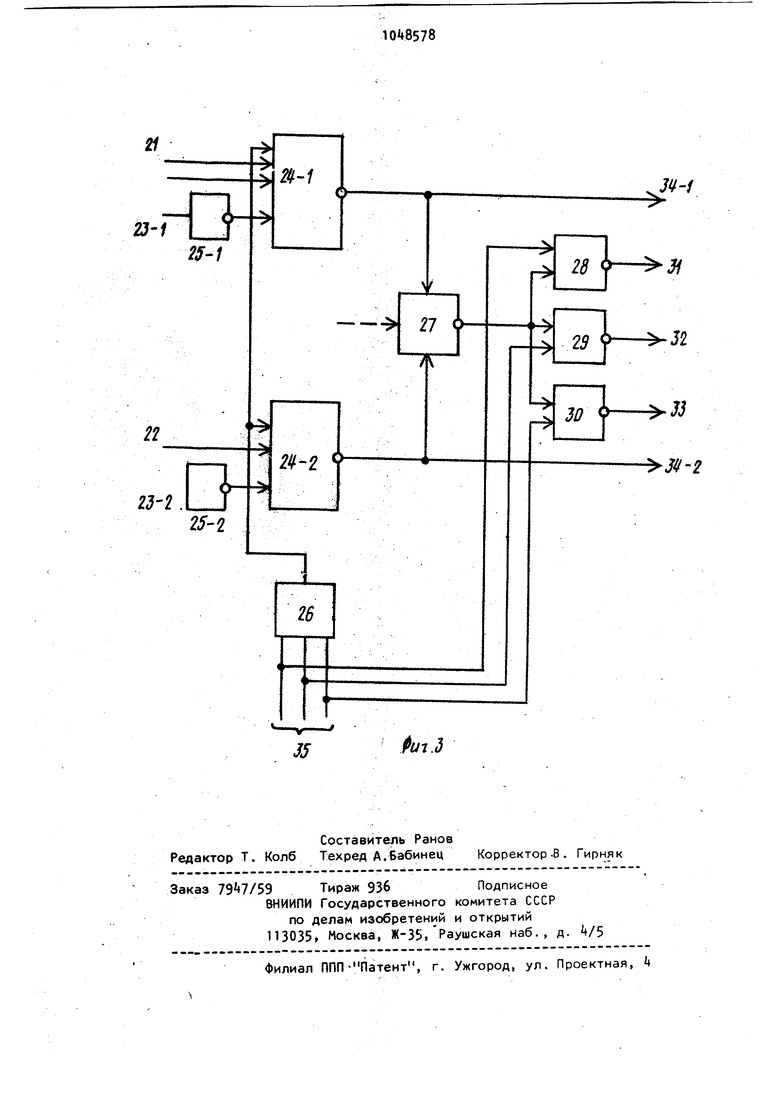

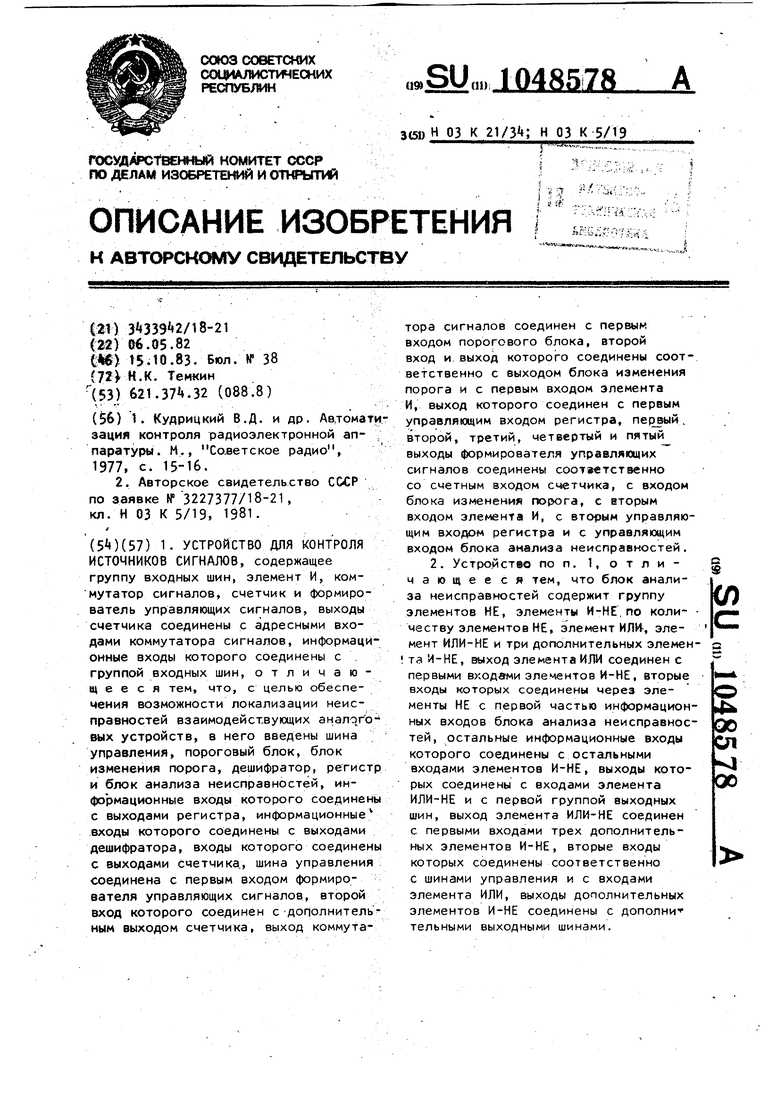

На фиг. 1 приведена блок-схема устройства для контроля источников сигналов, на фиг. 2 - диаграммы работы устройства для контроля источников сигналов, на фиг. 3 - схема блока анализа неисправностей устройства для контроля источников .

Устройство содержит группу 1 входных шин, коммутатор 2 сигналов, формирователь 3 управляющих сигналов, счетчик k, пороговый блок S, блок 6 изменения порога, элемент 7 И, дешифратор 8, регистр 9 блок 10 анализа неисправностей, выходные шины } - k и шину 15 управления. Группа 1 входных шин соединена с информационными входами коммутатора

2сигналов, выход которого соединен с первым входом порогс вого блока 5, второй вход и выход которого соединены соответственно с выходом блока 6

5 изменения порога и с первым входом элемента 7 И, выход которого соединен с первым управляющим входом регистра 9, выходы и информационные входы которого соединены соответственно с информационными входами блока

0

10; анализа неисправностей и с выходами дешифратора 8, входы которого соединены с адресными входами коммутатора 2 сигналов и соединены с выходами счетчика , дополнительный вы5ход которого соединен с первым входом формирователя 3 управляющих сигналов, второй вход, первый, второй, третий, четвертый и пятый выходы

0 которого соединены соответственно с шиной 15 управления, со ci/етным входом счетчика 4, со входом блока 6 изменения порога, со вторым входом элемента 7 И, со вторым управляющим входом регистра 9 и с управляющим

5 входом блока 10 анализа неисправностей, первый, второй и третий выходы которого соединены соответственно с выходными шинами 11, 12 и 13 ДОполнитёльные выходы блока 10 анали0за неисправностей соединены с выходными шинами I.

На фиг. 2 представлены диаграммы 16 - 20 сигналов соответственно на первом, втором, третьем, четвер5том и пятом выходах формирователя

3управляющих сигналов.

Блок 10 анализа неисправностей (фиг. 3) содержит информационные

0 входы 21, 22, 23-1, 23-2, элементы и 2k-2 И-НЕ, элементы .25-1 и 25-2 НЕ,, элемент 26 ИЛИ, элемент 27 ИЛИ-НЕ, элементы 28-30 И-НЕ, выходы 31-33, дополнительные виходи 3+-1

5 и , управляющие входы 35.

На фиг. 3 управляющие входы 35 соединены соответственно с первыми входами элементов 28-30 И-НЕ и соедийены со входами элемента 26 ИЛИ, вы ход которого соединен с первыми входами элементов 24-1 и И-НЕ вторые входы которых соединены соот ветственно с выходами элементов 25-V и 25-2 НЕ, входы которых соеди нены соответственно с информационны ми входами 23-1, 23-2 блока 10 анализа неисправностей, информационные входы 21 и 22 которого соединены соответственно с третьими входами элементов и 24-2 И-НЕ, выходы которых соединены соответственно с дополнительными выходами и 3 блока 10 анализа неисправностей и соединены со входами элемента 27 ИЛИ-НЕ, выход которого соединен со вторыми входами элементов 28-30 И-НЕ, выходы которых соединены соот ветственно с выходами 31-33 блока 10 анализа неисправностей. Коммутатор 2 сигналов является коммутатором аналоговых сигналив, обеспечивающий коммутацию на свой выход сигналов, поступивших на вход, номер которого соответствует коду, поданному на адресные входы коммутатора 2. Информационные входы коммутатора 2 являются входами, на которые пода 1бтся нормированные сигналы контроли руемых аналоговых устройств по груп пе 1 входных шин. Формирователь 3 управляющих сигналов предназначен для обеспечения взаимодействия всех составных частей устройства в необходимой времен ной последобательности. Период конт роля состоит из трех циклов: цикл контроля работоспособности взаимодействующих аналоговых устройств, цикл контроля по нижнему допустимом уровню входных сигналов, и цикл контроля по верхнему допустимому уровню входных сигналов. В каждом цикле работа устройства состоит из двух тактов: такта выявления неисправного канала и такта анализа выявленных неисправностей. Формирователь 3 на каждом такте вырабатывает следующие сигналы: на первом выходе - счетные, импульсы (фиг. 2, диаграмма 16), на второ выходе - сигнал-управления величино порогового уровня (фиг. 2 диаграмма 17), на третьем выходе - сигнал ПРОВЕРКА (фиг. 2, диаграмма 18), на|Четвертом выходе - сигнал СБРОС (фиг. 2, диаграмма -19), на пятом выходе - сигнал АНАЛИЗ (фиг. 2, диаграмма 20). . Формирователь имеет два входа. Первый вход соединен с дополнительным выходом счетчика 4, второй вход предназначен для подачи по шине 15 управления команд перевода формирователя 3 управляющих сигналов в режим поочередного формирования либо всех трех циклов контроля, либо периодического повторения любого одного из циклов. Формирователь 3 может быть реали(зован на элементах дискретной и циффовой техники - мультивибраторе и логических узлах. Счетчик 4 является обычным счетчиком импульсов. Переключение счетчика происходит по переднему фронту импульсов отрицательной полярности (фиг. 2, диаграмма 16). Пороговый блок 5 обеспечивает сравнение нормированных уровней контролируемых сигналов, поступающих с выхода коммутатора 2, с поро говым уровнем, поступающим с блока 6 изменения порога. Еслив первом цикле входной сигнал превышает уровень VQ (Vg - порог, соответствую- щий началу срыва функционирования . контролируемых устройств), во втором цикле входной сигнал превышает VH нижний допустимый уровень, при котором устройства еще функционируют, но величины сигналов занижены по сравнению с нормальными .уровнями, а,в третьем цикле - не превышает V ц ( V в верхний допусти1 1й уровень, при котором устройства еще функционируют, но величины сигналов завышены по сравнению с нормальными уровнями , пороговый блок 5 выдает на свой выход уровень логической 1. При других соотношениях между нормированными уровнями входных сигналов и пороговыми уровнями на выходе порогового устройства формируется уровень логического О. Блок 6 изменения порога обеспечивает по командам, поступающим с формирователя 3 управляющих си1- налов, изменение пороговых уровней для порогового блока 5. Блок 6 реализуется на основе коммутаторов аналоговых сигналов и источников напряжений, соответствующих пороговым уровням. Элемент 7 И является обычным двухвходовым элементом совпадения одноименных логических уровней, например уровней 1. Дешифратор 8 является обычным логическим элементо преобразующим входной код числа, например двоичный, в его позиционный кОд. Регистр 9 представляет собой п:1раэрядное ОЗУ с организацией тх 1 , построенное, например, на К5-триггерах. Число г равно числу входов 1 устройства, т.е. числу контролируемых сигналов. . Блок 10 анализа неисправностей обеспечивает сопоставление поступаю щих на него с регистра 9 логических уровней отображающих исправное (логическая 1 или неисправное {логический О) состояние выходов взаимосвязанных контролируемых устройств. При возникновении неисправно ти блок 10. путем сопоставления этих уровней вырабатывает сигнал неиспра ности определенного устройства, локализуя тем самым неисправность, а также формирует обобщенный сигнал неисправности совокупности контроли руемых устройств. Работа предложенного ycтpoйtтвa происходит следующим образом. Первоначально на второй вход фор ирователя 3 управляющих сигналов по шине 15 подается команда, перево дящая формирователь 3 в режим пооче редного формирования трех циклов. На первом такте каждого цикла (фиг. 2) производится выявление неисправного канала контроля. На втором такте каждого цикла производ ся анализ выявленных неисправностей и вь1рабатываются сигналы о неисправ ности определенного контролируемого устройства и обобщенный сигнал неисправности совокупности контролируемых устройств. В начале первого такта вырабатывается сигнал СБРОС (фиг. 2, диагра ма 19), обнуляющий все hi ячеек реги ра 9. По переднему фронту счетного импульса (фиг. 2, диаграмма 16) счетчик А устанавливается в eдиницy подключая тем самым на выход коммут тора 2 первый.контролируемый канал. В течение интервала времени (tg , {. из этого канала на вход порогового блока 5 поступает нормирован ный сигнал, уровень которого сравни Q8 веется с порогом, вырабатываемым блоком 6. Если результат сравнения удовлетворяет заданным критериям, на выходе порогового блока 5 формируется уровень логической 1, что характеризует для каждого, из циклов контроля исправное состояние контро лируемого в данный интервал времени канала. . Критерием исправного срстояния канала являются: на первом цикле на втором цикле на третьем цикле Vg в где YO - уровень, соответствующий неработоспособному состоянию контролируемых устройств, предельно-допускаемое минимальное значение уровней сигналов контролируемых устройств; предельно-допускаемое макси мальное значение уровней сигналов контролируемых устройств. Таким образом, при исправном, состоянии канала на элемент 7 И с порогового блока 5 поступает логическая Ч а на второй вход элемента 7 И поступает сигнал ПРОВЕРКА с формирователя 3 управляющих сигналов (фиг. 2,.диаграмма 17, интервал-L. t-z)- Поэтому сигнал логической 1 с порогового блока 5 проходит на выход элемента 7 И, поступает на первый управляющий вход регистра 9 и устанавливает в состояние М ячейку регистра, соответствующую номеру проверяемого в данный момент канала. Затем аналогичным образом проверяется следующий канал, и если все каналы исправны, к окончанию первого такта все ячейки регистра 9 будут находиться в единичном состоянии. Если же какой-то канал неисправен, то в течение времени проверки этого канала на выходе порогового блока 5 выраба- . тывается уровень логического О и поэтому соответствующая данному каналу ячейка регистра окажется в нулевом состоянии. Таким образом, при наличии каких-либо неисправностей на первом цикле контроля выявятся неработоспособные каналы, на втором -каналы; с заниженными уровнями сигналов. а на третьем цикле - каналы с завышенными уровнями сигналов, причем номеру неисправного канала соответствует номер ячейки регистра 9 оставшейся к концу первого такта в нулевом состоянии. По окончании первого такта формирователь 3 управляющих сигналов фиг. 2, диаграмма 20) вырабатывает сигнал АНАЛИЗ 1 на первом цикле, сигнал АНАЛИЗ. 2 - на втором и сигнал АНАЛИЗ 3 - на третьем цикле и прекра щает на время действия этих сигналов формирование сигнала ПРОВЕРКА (фиг. 2, диаграмма 17). Сигнал АНАЛИЗ 1 (2, 3) поступает на блок-10 анализа неисправностей,.разрешая его работу. Работа этого блока (фиг. З) при поступлении сигнала АНАЛИЗ 1 происходит следующим образом. Входы 21 и 22 блока 10 подключены к выходам ячеек регистра 9 устройств контроля таким образом, что на эти входы подаются сигналы с таких ячеек регистра, в которых по окончании такта 1 записана информация о работо способности( V р Vo) или неработоспособности (у вх )Tex контролируемы устройств, сигналы которых являются входными для аналогового устройства, формирующего из этих входных сигнало 21 и 22 свой выходной сигнал, поступа ющий на входы 23-1 или 23-2. Если аналоговое устройство, напри мер первое, исправно, то сигнал на входе 23-1 логическая 1. На выходе элемента-23-1 И-НЕ в этом случае появится уровень логической 1, что характеризует исправное состояние первого устройства. Если при проверке в первом такте выявлена неработоспособность первого устройства, это может быть следствием того, что первое устройство неисправно,или того, что первое устройство исправно, но отсутствует один из его входных сигналов. В первом случае сигналы на входах 21 и 22 - логическая 1, а на входе 23-1 - логический О, следовательно элемент И-НЕ сформирует на своем выходе и на выходе З уровень логического О, что и характеризует неисправное состояние i 8 первого устройства. Выходные сигналы всех элементов , И-НЕ подаются на элемент 27 ИЛЙ-НЕ и поэтому на его выходе появляется уровень логической 1. А так как сигнал АНАЛИЗ 1 подан на первый вход элемента 2б ИЛИ и на первый вход элемента 28 И-НЕ, на выходе элемента 28 И-НЕ и на вйхрде 31 появляется уровень логического О, что является обобщенным сигналом неработоспособности совокупности взаимодействующих контролируемых устройств. Во втором случае один из сигналов на входах 21 и 22 - логический О и поэтому, несмотря на то, что и сигнал на входе 23-1 - логический О, на выходе элемента И-НЕ появляется уровень логической 1, что соответствует исправному состоянию первого устройства. Сигнал неисправности в этом случае будет выдан для другого устройства, у которого, при наличии всех его входных сигналов, выходной сигнал отсутствует (Vgbix Vo). Аналогичным образом происходит работа блока 10 анализа неисправностей на втором и третьем циклах. При этом на втором цикле выявляются устройства с заниженным уровнем выходных сигналов, а на третьем с завышенным уровнем. Так как при последовательной смене циклов появление ;7бгического О на одном из выходов и характеризует лишь неисправное состояние какого-либо устройства, для уточнения характера неисправности (отказ; занижение или завышение выходных уровней) оператор переводит формирователь 3 управляющих, сигналов, подавая соответствующий сигнал на его второй вход, в режим последовательного повторения только первого, затем второго и затем третьего цикла, что и позволяет уточнить характер неисправности какого-то устройства. Таким образом, предложенное устройство обеспечивает локализацию неисправностей взаимодействующих аналоговых устройств, выявляя при этом характер неисправности - отказ, занижение или завышение выходных уровней этих устройств.

Такту

1 -

Lnm

LTU

;5

2

1ПГЛ

f7

if 2

TffK/nj

Lrtnr

nnr

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1383416A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля группы цифровых узлов | 1987 |

|

SU1534461A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1075394A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

1 Лорог UQ

/

U

19

i/

I Порог Uf

1/1.2

35

Pui .5

Авторы

Даты

1983-10-15—Публикация

1982-05-06—Подача