1

СП

СО

со

4

2. Устройство по п.1, отличающееся тем,- что блок памяти содержит дешифратор и регистр, вход сброса которого соединен.с входом cCipoca блока памяти, вход записи - с вторым входом блока памяти, а входы выбора разрядов подключены к выходам дешифратора, входы ко- торого соединены с адресными входами блока памяти.

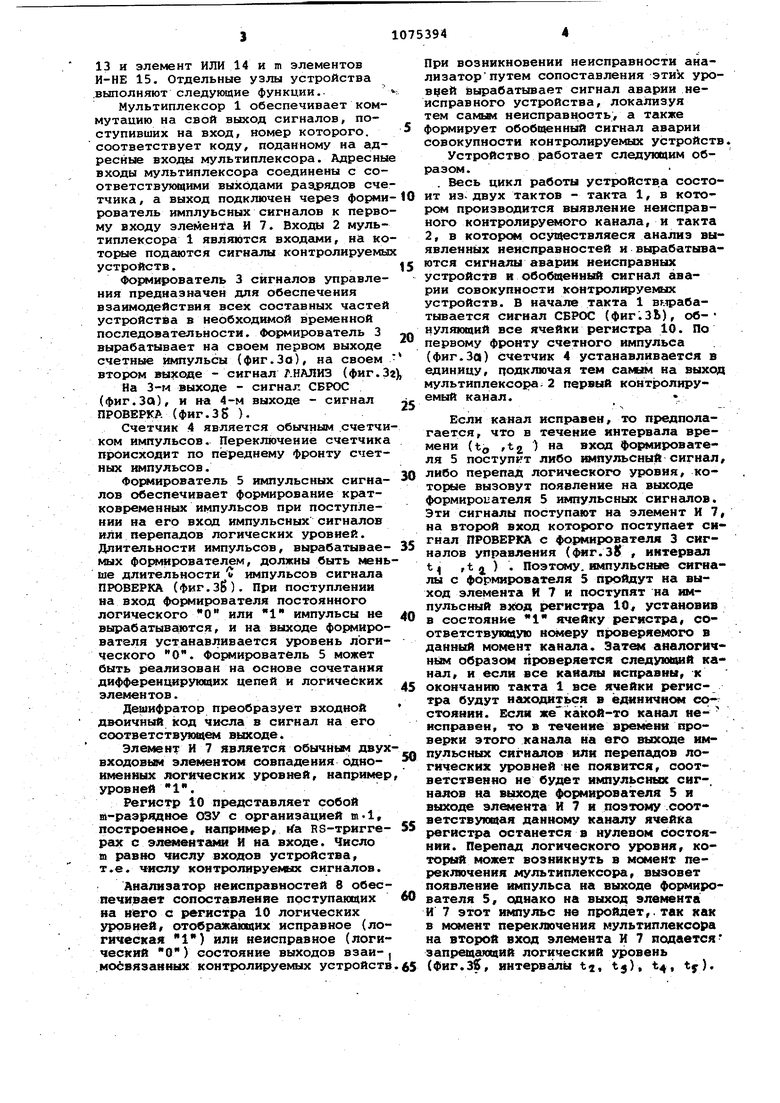

3. Устройство по ПП.1 и 2, о т - . личающееся тем, что блок анализа неисправностей содержит элементы И-НЕ, выходы которых подключены к соответствующим входам элемента ИЛИ, первые входы соединены с вто- рьм входом блока анализа неисправностей, второе входы через инвертор, а группы третьих входов непосредственно соединены с первыми входами блока анализа неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля источников сигналов | 1982 |

|

SU1048578A1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ. ЦИФРОВЬК БЛСЖОВ, содержащее элемент И, .4юрмирователь импульсов, мультиплексор, сигнальные входы-которого 1ПОдкгеочены к соответствующим первьш входам всего устройства, а входы управления - к выходам счетчика, счетный вход которого соединен с выходсм формирователя сигналов управления. отличающееся тем, что, с целью расширения функциональных возможностей, в иего ввеяен блок памяти, блок анализа неяЕСправностей и формирователь импульсов, первые входы которого соединены с выходами блока памяти, а второа вход подключен к второму выходу формирователя сигналов управления, третий выход которого подключен к входу сброса блока памяти, а четвертый - к вторсму входу элемента И, выход которого соединен с входом блока памяти, адресные входш которого поразрядно соединены с соЪтветствупцими выходами счетчика и с входами формирователя сигналов управления, причем выход щ мультиплексора соединен с первым i входом элемента И через формирователы/Л импульсов.

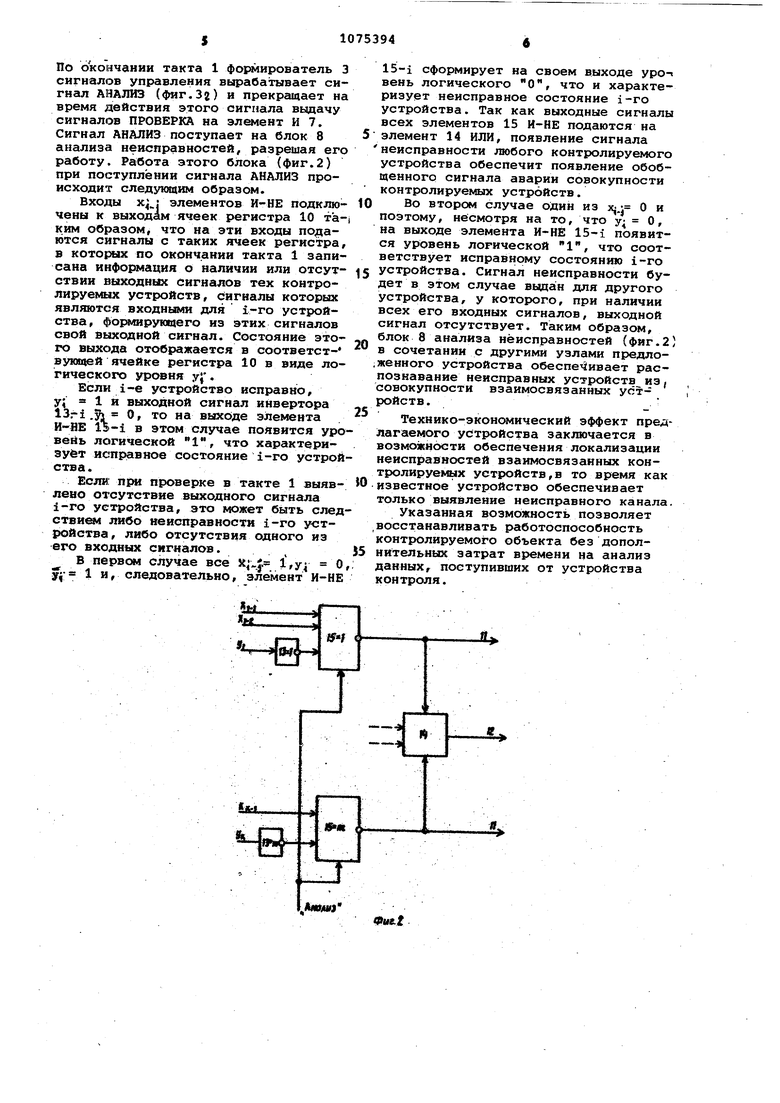

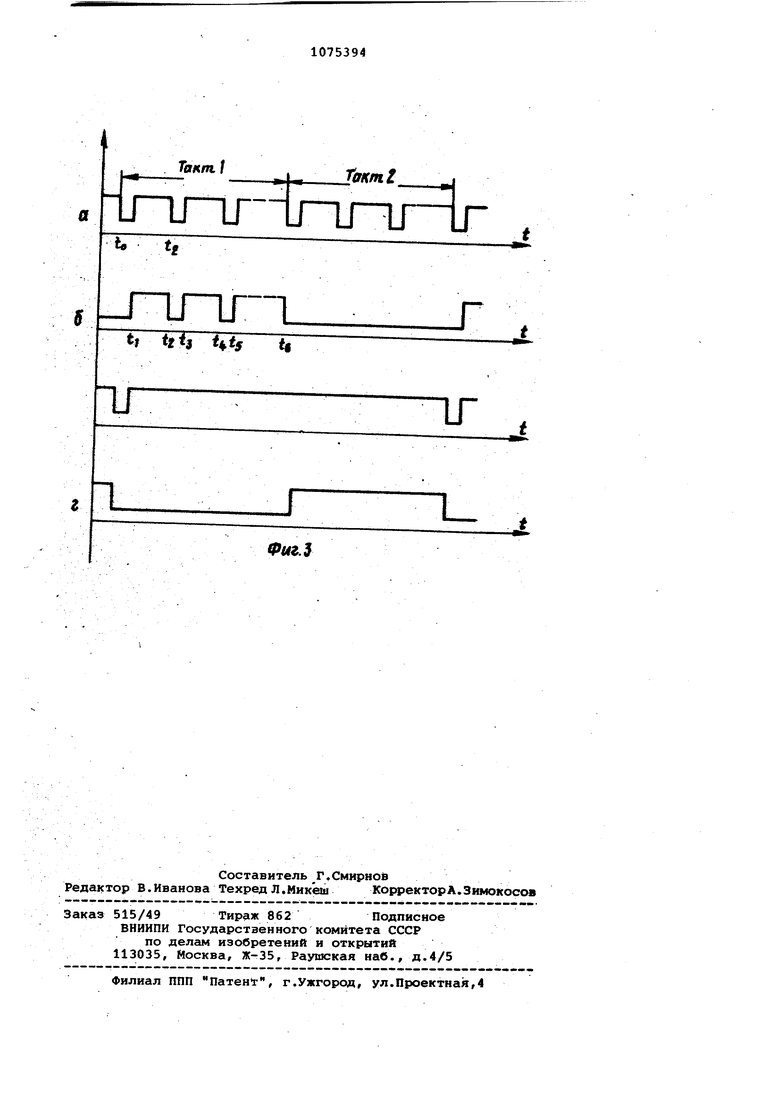

Устройство относится к импульсной технике, в частности к устройствам для контроля цифровых устройств с непрерывной сменой выходных логических состояний и выявления и локализа ции неисправностей в разветвленных взаимосвязанных цепях. Известно устройство для контроля счетчиков, содержащее счетчик и элемет:ы совпадения Ш . Данное устройство обладает недостаточными функциональными возможное тями. близким к изобретен1до йо технической сущностиявляется устройство для контроля цифровых блоков, содержащее элемент И, формирователь импульсов, мультиплексор, сиг нальные BxctQH которого подключены к соответствующим первьол входам всего ycTpoffecTBa, а входы управления - к выходам счетчика, счетный вход которого С оединен с выходом формирователя сигналов управления {2 . Однако известное устройство также не обладает достаточн № и функциональ , ньми &озможностя ш, поскольку не обе спечивает возможности локализации неисправностей взаимосвязанных устройств. Цель изобретения - расширение фун кциональных возможностей устройства. По : та8леиная цель достигается тем что в ycTpcrflcTBO для контроля цифровых Споков, содержащее злемент|( И, фО{ шрователь импульсов, мульт йплексор, сигнальные входы которого подключены к соответствующим парвьш вхо дам всего устройства, а вхоаа управлеиия - к выходам счетчика, счетньШ вход которого соединен с выходом фор миров 1теля сигналов управления, внеданы блок памяти, блок анализа неисправнсстей и формирователь импульсот первьк входы которого соединены с выход 1ми блока памяти, а второй вход подключен к второму выходу формиро. вателя сигналов управления, выход которого подключен к входу сброса блока памяти, а четвертый к второму входу элемента И, выход которого соединен с вторым входом блока памяти, адресные входы которого поразрядно соединены с соответствующими выходгши счетчика и с входами формирователя сигналов управления, причем выход мультиплексора соединен с первьм входом элемента И через формирователь импульсов. Кром того, блок памяти устройства может содержать дешифратор и регистр, вход сброса которого соединен с входом сброса блока памяти, вход записи с вторым входом блока памяти, а выходы выбора разрядов подключены к выходам дешифратора, входы которого соединены с адресными входами блока памяти. При этом блок анализа неисправносте.й содержит элементы И-НЕ, выходы . кото{дах подключены к соответствующим входам элемента ИЛИ, первые входы соединены с вторьм -входом блока анализа неисправностей, вторые входы через инвертор, а группы третьих входов непосредственно соединены с первыми входами блока анализа неисправностей. На фиг.1 представлена функциональиая схема устройства контроля цифровых блоков f на фиг.2 - схема блока анализа неисправностей на фиг.З вр енные диагргичмы, поясняющие работу устройства. Устройство содержит мультиплексор 1, сигнальные входы 2 которого являются входами устройства, формирователь 3 сигналов управления, счетчик 4, форми|рователь 5 импульсов, блок б памяти элемент И 7, 8 анализа неисправностей, блок памяти в своем составе содержит дешифратор 9 и ре..глстр 10. Ш:гходы 11 блока анализанеисправностей являются в&ходако .сигналов аварии устройства, выход 12 - выходом обобщенного сигнаЛа аварии, блок 8 анализа неисправностей имеет в своем составе m инверторов 13 и элемент ИЛИ 14 и m элементов И-НЕ 15. Отдельные узлы устройства .выполняют следующие функции.. Мультиплексор 1 обеспечивает коммутацию на свой выход сигналов, поступивших на вход, номер которого, соответствует коду, поданному на адресные входы мультиплексора. Адресны входы мультиплексора соединены с соответствующими выходами разрядов сче тчика , а выход подключен через форми рователь имплуьсных сигналов к перво му входу элемента И 7. Входы 2 мультиплексора 1 являются входс1ми, на ко торые подаются сигналы контролируемы устройств. ФорМ1фователь 3 сигналов управления предназначен для обеспечения взаимодействия всех составных частей устройства в необходимой временной последовательности. Формирователь 3 вырабатывает на своем первом выходе счетные импульсы (фиг.Зо), на своем втором выходе - сигнал ДНАЛИЗ (фиг.З На 3-м выходе - сигнал СБРОС (фиг.Зэ), и tta 4-м выходе - сигнал ПРОВЕРКА (фиг.3S ). Счетчик 4 является обычным .счетчи ком импульсов. Переключение счетчика происходит по переднему фронту счетных импульсов. Фо1 «ирователь 5 импульсных сигналов обеспечивает формирование кратковременных импульсов при поступлении на его вход импульсных сигналов или перепадов логических уровней. Длительности импульсов, вырабатывавмых фО1 1ирователем, должны быть мень ше длительности С импульсов сигнала ПРОВЕРКА (фиг.зб). При поступлении на вход формирователя постоянного логического О или 1 импульсы не вырабатыва ются, и на выходе фо{ ирователя устанавливается уровень логического О. Формирователь 5 может быть реализован на основе сочетания дифференцирующих цепей и логических элементов. Дешифратор преобразует входной двоичный код числа в сигнал на его соответств ощ«|4 выходе. Элемент И 7 является обЕлчным Двух входовым элементом совпадения одноикюнных логических уровней, например уровней 1. Регистр to представляет собой а-раэрядное ОЗУ с организацией m1, построенное, наприьюр, ka RS-триггеpax с элементами И на входе. Число m равно числу входов устройства, т.е. кантролируемБгх сигналов. Анализатор неисправностей 8 обеспечивает сопоставление поступающих на него G регистра 10 логических уровней отображёиощих исправное (логическая 1) или неисправное (логический О) состояние выходов взаимоёвязанных контролируемых устройств При возникновении неисправности анализатор путем сопоставления этих уровцей вырабатывает сигнал аварии неисправного устройства, локализуя тем самьм неисправность, а также формирует обобовенный сигнал аварии совокупности контролируемых устройств. Устройство работает следующим образом. . Весь цикл работы устройств.а состоит из- двух тактов - такта 1, в котором производится выявление неисправного контролируемого канала, и такта 2, в которсм осуп ествляеся анализ выявленных неисправностей и вырабатываются сигналы аварии неисправных устройств и обоС ценнцА сигнал аварии совокупности контролируемых устройств. В начале такта 1 вкчрабатывается сигнал СБРОС (фиг.ЗЬ), об- нуляющий все ячейки регистра 10. По первому фронту счетного импульса (фиг.За) счетчик 4 устанавливается в единицу, подключая тем самьш на выход мультиплексора 2 первый контролируемый канал. Если канал исправен, то предполагается, что в течение интервала времени (tg ,t2 ) на вход формирователя 5 поступит либо импульсный сигнал, либо перепад логического уровня, которые вызовут появление на выходе формиро1;ателя 5 импульсных сигнгшов. Эти сигналы поступают на элемент И 7, на второй вход которого поступает сигнал ПРОВЕРКА с фо1якирователя 3 сигналов управления (фиг.з1$ , интервал t ,tд ) . Поэтому, импульсные сигналы с формирователя 5 пройдут на выход элемента И 7 и поступят на импульсный взсоа регистра 10, установив в состояние 1 ячейку регистра, соответствующую Hontepy проверяемого в данный канала. Затем аналогичным образом проверяется следуюш1й канал, и если все каяалы исправны, к окончанию такта 1 все ячейки регистра будут наосодиться в ёдиничн М4 состоянии. Если жекакой-то канал неисправен, то в течение времени проверки этого канала на его выходе импульсных сигналов или перепадов логических уровней не появится, соответственно не будет импульсных сиг-, налов на выходе формирователя 5 и выходе элемента И 7 и поэтому .соответствующая данному каналу ячейка регисофа останется в нулевом состоянии. Перепад логического уровня, коТО1Ж1Й может возникнуть в момент переключения мультиплексора, вызовет появление импульса на выходе формирователя 5, свиако на выход элемента И 7 этот импульс не пройдет,, так как в мсялеит переключения мультиплексора на второй вход элемента И 7 подаетсязапрещающий логический уровень (фиг.З, иитервалы t, 45), t4, ty). По окоЪчании такта 1 формирователь 3 сигналов управления вырабатывает сигнал АНАЛИЗ (фиг.Зг) и прекращает на время действия этого сигнала выдачу сигналов ПРОВЕРКА на элемент И 7. Сигнал АНАЛИЗ поступает на блок 8 анализа неисправностей, разрешая его работу. Работа этого блока (фиг.2) при поступлении сигнала АНАЛИЗ происходит следующим образом. Входш x.j элементов И-НЕ подключены к выходам ячеек регистра 10 так.им образом, что на эти входы подаются сигналы с таких ячеек регистра, в которых по окончании такта 1 записана информация о наличии или отсутствии выходных сигналов тех контролируемых устройств, сигналы которых являются входными для i-ro устройства, форлирукшего из этих сигналов свой выходной сигнал. Состояние этого выхода отображается в соответствуюцей ячейке регистра 10 в виде логического уровня у|. Если i-e устройство исправно, у; а 1 и выходной сигнал инвертора 13.-1.й О, то на выходе элемента И-НЕ 1з1-1 в этом случае появится уро вень логической 1, что характеризует исправное состояние i-ro устрой ства . Если: П1Ж проверке в такте 1 выявлено отсутствие выходного сигнала i-ro устройства, это может быть след ствиях лшбо неисправности i-ro устройства, либо отсутствия одного из его входных сигналов. В первом случае все X|«4. О у 1 и, следовательно, элемент И-НЕ 15-1 сформирует на своем выходе уро- вень логического О, что и характеризует неисправное состояние i-го устройства. Так как выходные сигналы всех элементов 15 И-НЕ подаются на элемент 14 ИЛИ, появление сигнала неисправности любого контролируемого устройства обеспечит появление обобщенного сигнала аварии совокупности контролируемых устройств. Во втором случае один из х,- О и поэтому, несмотря на то, что у О, на выходе элемента И-НЁ 15-1 появится уровень логической 1, что соответствует исправному состоянию i-ro устройства. Сигнал неисправности будет в этом случае вццан для другого устройства, у которого, при наличии всех его входных сигналов, выходной сигнал отсутствует. Таким образом, блок 8 анализа неисправностей (фиг.2) в сочетании с другими узлами предложенного устройства обеспеч:ивает распознавание неисправных устройств из, совокупности взаимосвязанных устройств. Технико-экономический эффект предлагаемого устройства заключается в возможности обеспечения локализации неисправностей взаимосвязанных контролируемых устройств,в то время как известное устройство обеспечивает только выявление неисправного канала. Указанная возможность позволяет , восстанавливать работоспособность контролируемого объекта без дополнительных затрат времени на анализ данных, поступивших от устройства контроля.

Такт, 1

1Г1Г1Г1Г1Г 1Г 1Г

а

г. tt

LnnrT

f

tt ttij «T

IT

Фиг.

Такт I

Г

IT

1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля двухтактного двоичного счетчика | 1981 |

|

SU970375A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля импульсов | 1980 |

|

SU949793A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-23—Публикация

1982-07-28—Подача