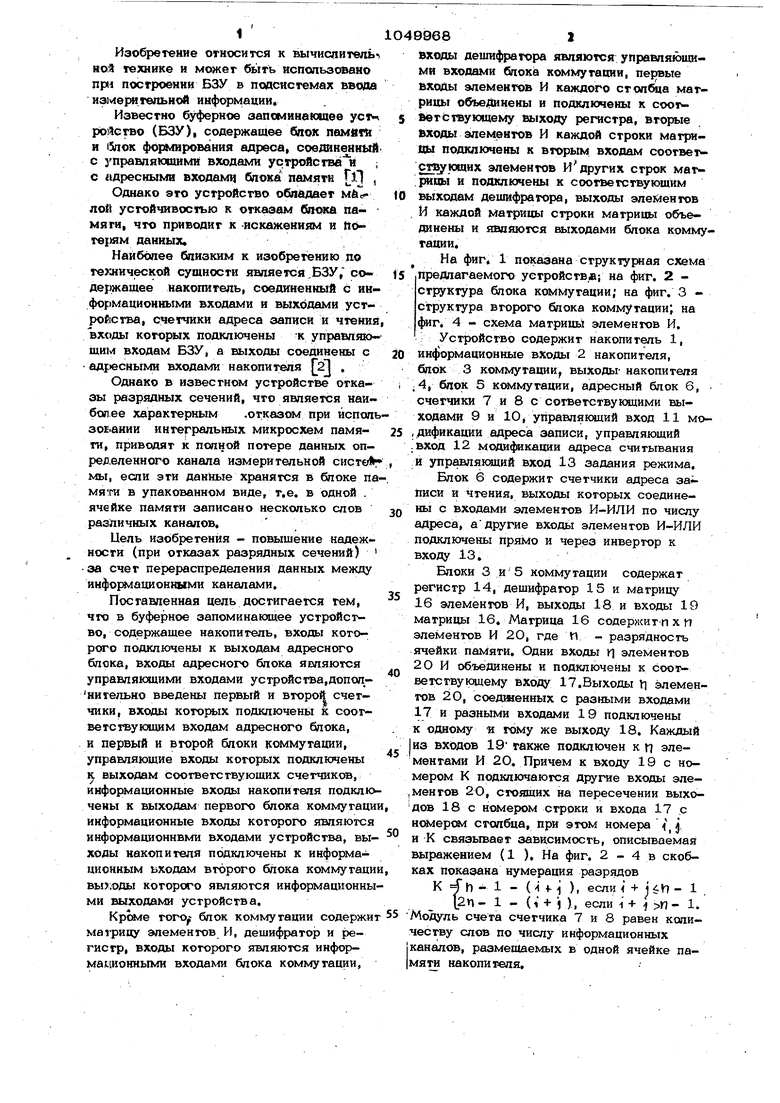

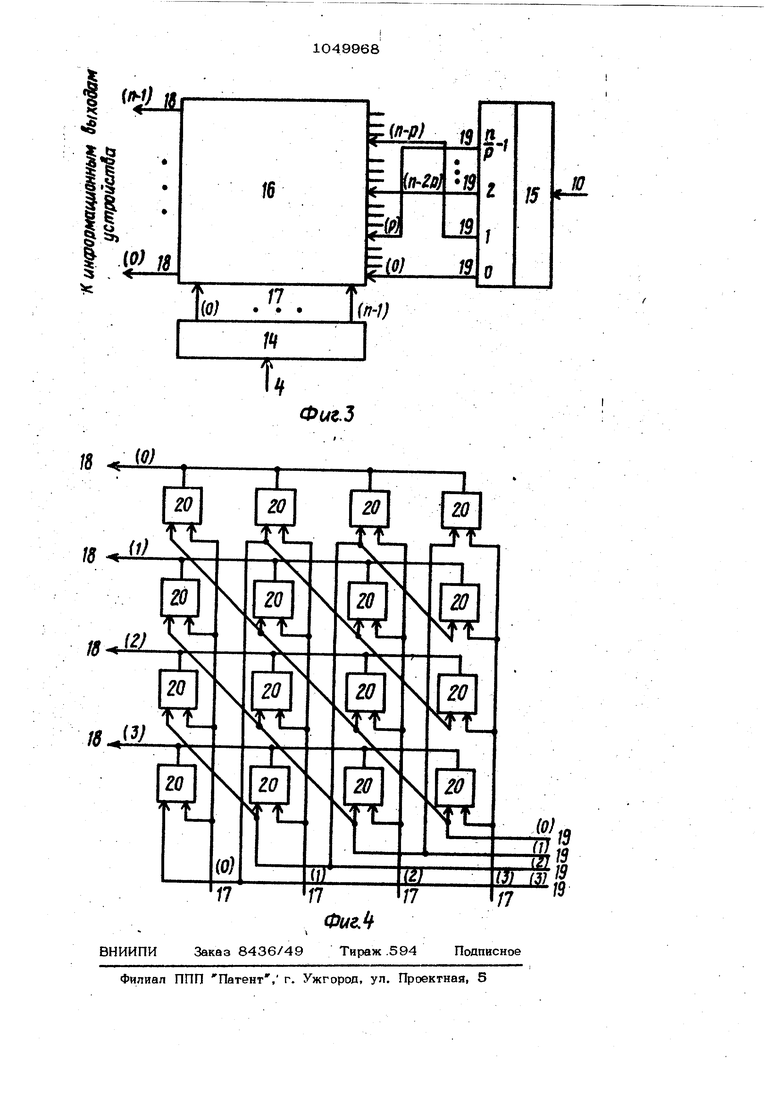

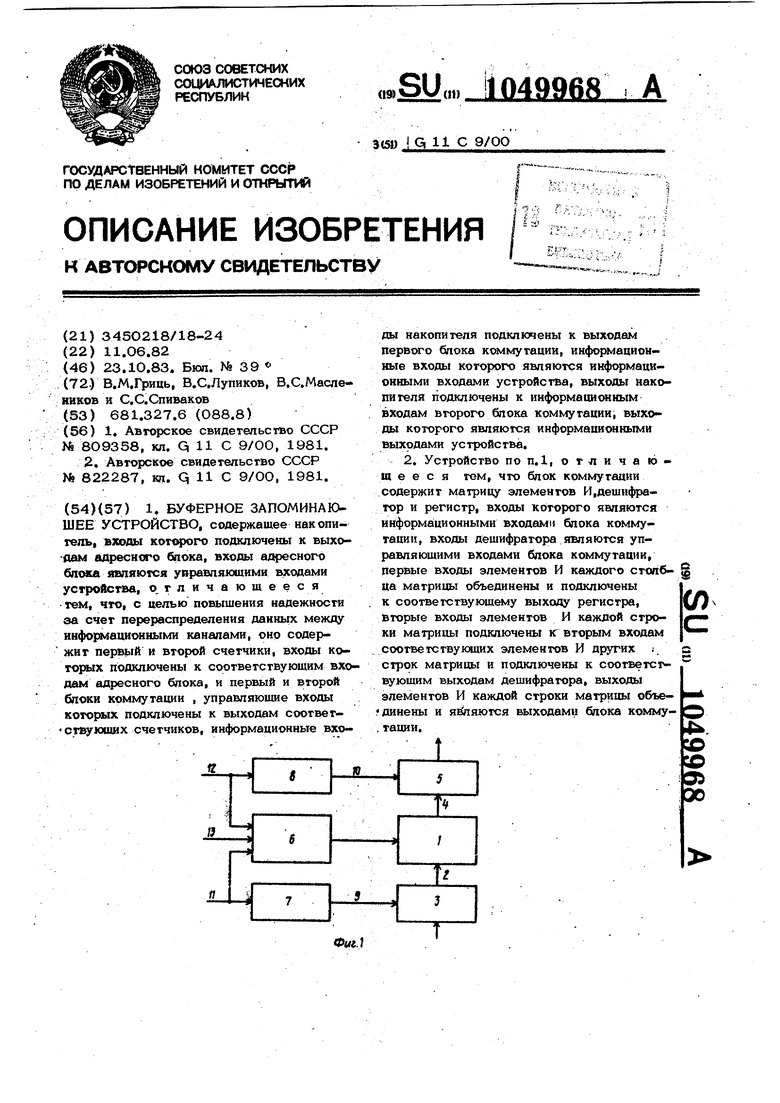

Изобретение огносится к вычислиrenь ной технике и может быть использовано npi построении БЗУ в подсистемах ввода измерительной информации.. Известно буферное запоминаюшее ус1ч poiDcTBo (БЗУ), содержащее блок памяти и блок фо1 лирования адреса, соедянш1ный с управляющими входами устройствв и ; с адресными входами блoкa памяти Til , Однако это устройство обладает устойчивостью к отказам блоха памяги, что приводит к -искажемням и tt данных. Наиболее близким к изобретению до ге}шической сущности является,БЗУ,содержащее накопитель, соединенный с информационными входами и выходами ус тpoficTBa, счетчики адреса записи и чтения входы которых подключены К управляю щим входам БЗУ, а вь1ходы соединены с ад1:1есными входами накопителя 2 . Однако в известном устройстве отказы разрядных сечений, что является наиболее характерным .отказом при йсполь зоЕ.ании интегральных микросхем памяти, приводят к полной потере данных определенного канала измерительной систеЛт мы, если эти данйые хранятся в блоке Па мяти в упакованном виде, т.е. в одной . ячейке памяти записано несколько слов различных каналов. Цель изобретения - повышение надеж ности (при отказах разрядных сечений) за счет перераспределения данных между инфор лационными каналами. Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее накопитель, входы которого подключены к выходам адресного блока, входы адресного блока являются управлякяцими входами ус тройства, дополнительно введены первый и второй счетчики, входы которых подключены к соответствующим входам адресного блока, и первый и второй блоки коммутации, управляющие входы которых подключены к выходам соответствующих счетчиков, информационные входы накопителя подшно чены к выходам первого блока коммутаци информационные входы которого являются информационнвми входами устройства, выходы накопителя подключены к информа ционным ьходам второго блока коммутаци выу.оды которого являются информационны ми выходами устройства. Кроме блок коммутации содержи ма1рицу элементов И, дешифратор и регистр, входы которого являются информанионньп ш входами блока коммутации, ВХОДЫ дещифратора являются управлякшшми входами блок(э коммутации, первые входы элементов И каждого cronGua матрицы объединены и подключены к соогветсгвующему выходу регистра, вторые входы элементов И каждой строки матрицы подключены к вторым входам соответся юинх элементов Идругих строк мат.рицы и подключены к соответствующим выходам дещифратора, выходы элементов И каждой Матрицы строки матрицы объединены и являются выходами блока коммутации. На фиг. 1 показана структурная cxeivia предлагаемого устройства; на фиг. 2 структура блока коммутации; на фиг. 3 структура второго блока коммутации; на фиг. 4 - схема матрицы: элементов И. Устройство содержит накопитель 1, информационные входы 2 накопителя, блок 3 коммутации, выходы-накопителя ;4, блок 5 К1 лмутации, адресный блок 6, счетчики 7 и 8 с сответствуклцими выходами 9 и 10, управляющий вход 11 мо,дификации адреса записи, управляющий вход 12 моди кации адреса считывания и управлякший вход 13 задания режима. Блок 6 содержит счетчики адреса записи и чтения, выходы которых соединены с входами элементов И-ИЛ И по числу адреса, а другие входы элементов И-ИЛИ подключены прямо и через инвертор к входу 13. Блоки 3 и5 коммутации содержат регистр 14, дешифратор 15 и матрицу 16элементов И, выходы 18 и входы 19 матрицы 16. Матрица 16 содержит-п х п элементов И 20, где И - разрядность ячейки памяти. Одни входы К элементов 20 И объединены и подключены к соответствующему входу 17.Выходы элементов 20, соедшенных с разными входами 17и разными входами 19 подключены к одному я тому же выходу 18. Каждый из входов 19 также подключен к п элементами И 2О. Причем к входу 19с номером К подключаются другие входы элементов 2О, стоящих на пересечении выходов 18с номером строки и входа 17 с HfHviepoM столбца, при этом номера i j, и К связывает зависимость, описываемая выражением (1 ). На фиг. 2 - 4 в скобках показана нумерация разрядов К h - 1 - (-1 4-1 ), если + - 1 . l2n - 1 - (i + J ), если 1 + - 1. Модуль счета счетчика 7 и 8 равен копичесгву слов по числу информационных каналов, размещаемых в одной ячейке паяти накопителя. Э1 Входы 19 матрицы 16 бдоки 3 комму тации подключены к выходам дешифратора 15 в порядке возрастания н(яиеров, причем подключается к дешифратору каждый р-й вход 19 начиная с нулевого. В бпоке 5 ксммутаиии порядок соединений входов 19 обратный, т.е. выходы деши4и рагора 15 в порядке возрастания номеров соединены с каждым р-м входом 19 в порядке убьгаания нскмеров нулевого.. Устройство работает следующим образом, V При записи информации на информада-OHHbie входь устройства подается ёходное слово, которое содержит данные от нескольких П /р измерительных каналов, причём все измерения представляются словами одинаковой разрядности р. Одновременно на вход 13 поступает сигнал операции Запись. При помощи этого сигнала с выхода адресного блока 6 на адрёсныё входы накопителя 1 подается адрес записи, после ;чего в выбранную ячейку памяти записывается входное словно, которое проходит через блок 3 без преобразования, тик как с выхода счетчика 7 на входы дешифратора 15 подаетс нулевой код, В результате этого нулевой вход 19 разрешает прохождение инфор мации из регистра 14 блока 3 через элементы И 20 без сдвига. После этого сигиалом модификации адреса записи .пос тупающим на вход 11, модифицируется адрес записи, формируемый блоком 6, и содержимое счетчика 7. При записи сле. дующего входного слова код счетчика 7 68создает разрешающий сигнал на следующем (первом) выходе дешифратора 15 блока 3, который поступает на Р-Й уп равляющий вход 19, разрешающий прохождение информации из регистра 14 на выходы 18 со сдвигом на Р разрядов, т.е. данные первого канала занимают место данных последнего канала, а данные остальных каналов сдвигаются, занимая место данных предыдущего 1санала. Если одно из разрядных сечений накопителя 1 отказывает, то .сечение проходит ереэ даннне нескольких каналов, упакованных в одно слово, а не через данные одного канала. Тем самым потери информации распределяются между нескопькими каналами. При чтении информации из устройства производится- сдвиг в обратаую сторону, тем самым восстанавливается исходный формат входных данных. Для осуществления обратного Ьдвига используется блок 5 коммутации, управляемый счетчиком 8. Оба блока 3 и 5 идентичны и отличаются друг от друга только порядком соединения управляющих входов 19 матрицы 16 с выходами дешифратора 15. Содержимое счетчика 8 модифицируется после каждого цик;ла чтения сигналом модификация адрёбй|чтения, поступающего на вход 12. Предлагаемое устройство позволяет повысить надежность устройства и избежать полной потери данных одного канала при отказе разрядного сечения.за счет распределения этих потерь между несколькими каналами, что при избыточности измерительной информация является допустимым в определенных пределах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163358A1 |

| Устройство коммутации | 1980 |

|

SU894866A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

1. БУФЕРНОЕ ЗАПОМИНАЮШЕЕ УСТРОЙСТВО, содержащее накопитель, входы кот«фого подключены к выходам адресного блока, входы адресного блока яяпяются уяравпякшими входами устройства, о гличаюшееся тем, что, с целью повышения надежности за счет перераспределения данных между информационными каналами, оно содер жит первый и второй счетчики, входы которых подключены к соответствующим входам адресного блока, и первый и второй блоки коммутации , управляющие входы которых подключены к выходам соогветствуюших счетчиков, информационные входы накопителя подключены к выходам первого блока коммутации, информационные входы которого являются информационными входами устройства, выходы накопителя подключены к информационным входам второго блока коммутации; выходы которого являются информационными выходами устройства. 2. Устройство поп. 1, отлнча1бШ е е с я том, что блок коммутации содержит матрицу элементов И,дещифратор и регистр, входы которого являются информационными входами блока коммутации, входы дешифратора являются управляющими входами блока коммутации, первые входы элементов И каждого столбца матрицы объединены и подключены (Л к соответствующему выходу регистра, звторые входы элементов И каждой строс ки матрицы подключены к вторым входам соответствующих элементов И других Строк матрицы и подключены к соответствующим выходам дешифратора, выходы элементов И каждой строки матрицы объе- единены и яЕ ;пяются выходами блока комму ;о со .тации. Од 00

.г.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-10-23—Публикация

1982-06-11—Подача