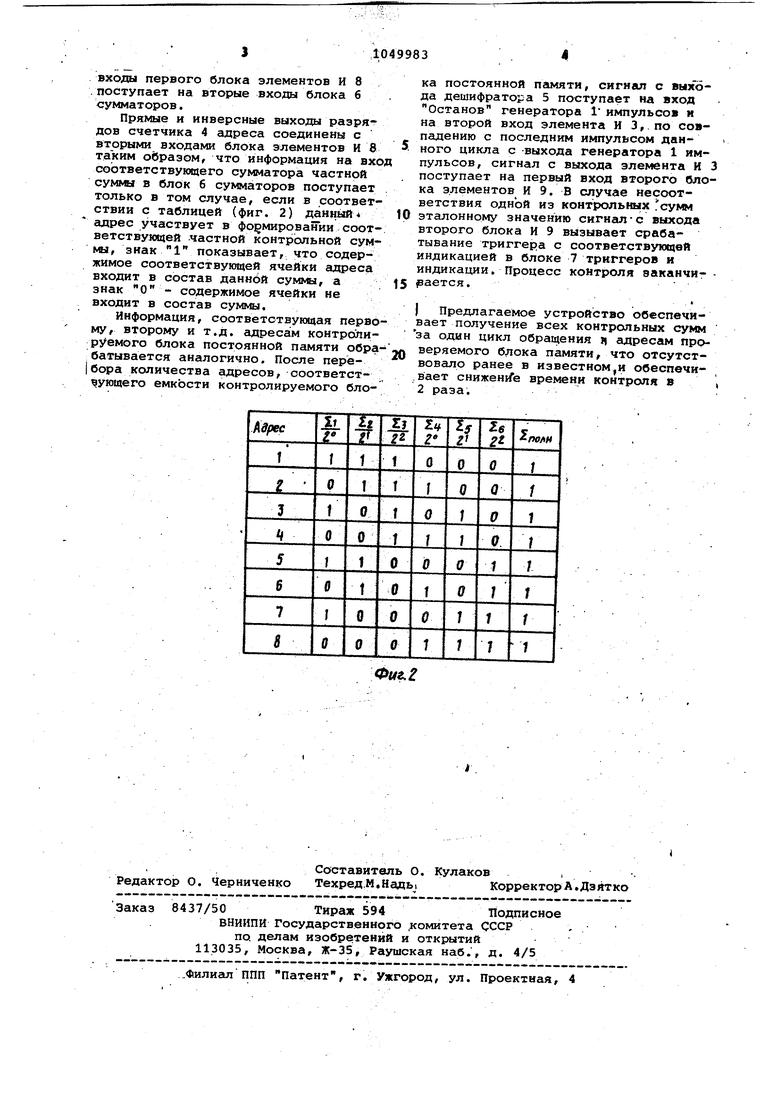

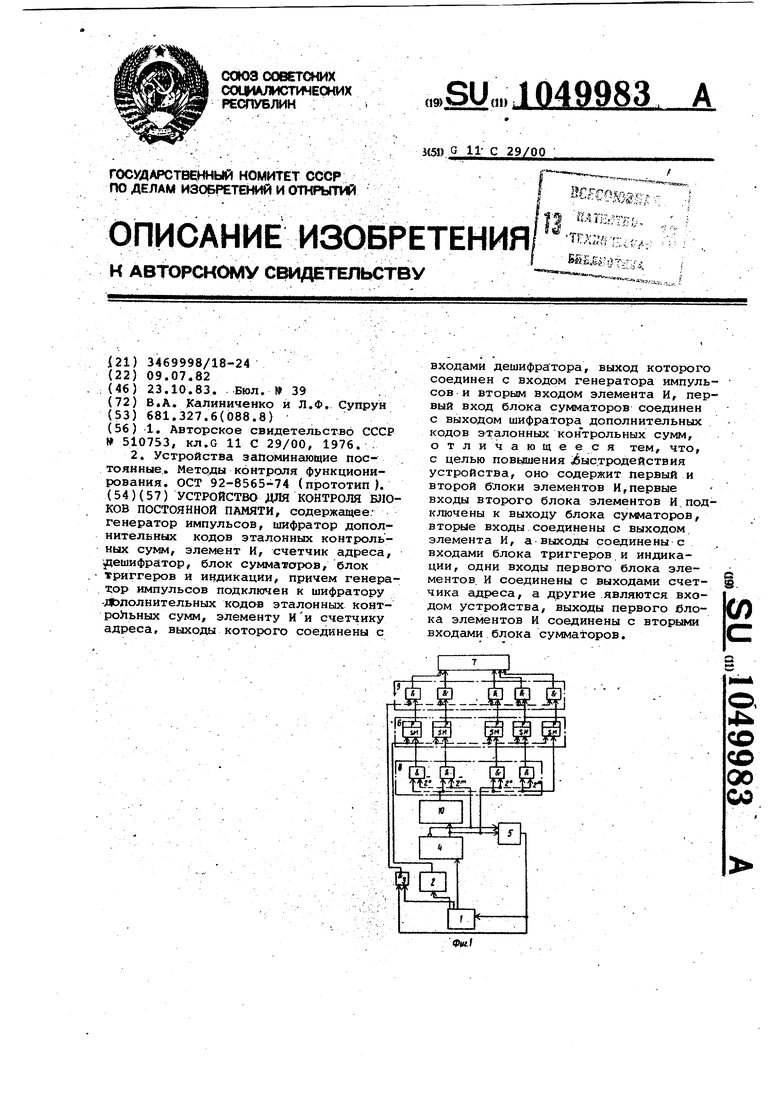

Изобретение относится к запоминающим устройствам, а именно к устройствам контроля блоков постоянной памяти. Известно устройство, содержащее считывающий блок, подключенный к входам блока управления и регистра адреса, и блок сравнения, счетчик и сумматор, входы которого подключены к выходам регистра адреса и одним входом блока сравнения, а выходы - к входам счетчика, выходы которого соединены с другими входами блока сравнения, выход которого подключен к блоку управления 1. Однако это устройство содержит . в своем составе считывающий блок, что снижает быстродействие устройства, а также не содержит в свое составе схем, обеспечивающих провер ку блоков постоянной памяти по полным и частным контрольным суммам. Наиболее близким к изобретению по технической сущности является устройство для контроля блоков постоянной памяти методом полных и частных Контрольных суим, содержащее блок управления, счетчик адреicoB, счетчик сумм, дешифратор,устройство установки, бл.ок ОЗУ, сумматор, сборку разрядов сумматора,- бло сравнения. В этом устройстве формирование и проверка частных и полных контрольн сумм на соответствие эталонным осущ ствляется путем. (-П+1) кратного просчета контрольных сумм по всем адре сам проверяемого блока постоянной памяти, где п --количество разрядов счетчика адреса Г2 J.. Недостатком известного устройств является низкое быстродействие, так как для получения контрольных сукм требуется (п+1) циклов обращения к адресам проверяемого блока постоянной памяти. . Цель изобретения - повышение быс родействия yc-fpoacTBa за счет получ . ния всех контрольных сумм за один цикл обращения к адресам проверяемо го блока памяти. Поставленная цель достигается те что в устройство,содержащее генератор импульсов, шифратор дополнитель ных кодов эталонных контрольных сум элемент и, счетчик адреса, дешифратор, блок сумматоров, блок триггеро и индикации, причем генератор импул сов подключен к шифратору дополмй-г кодов эталонных контрольных сумм, элементу И и счетчику адреса, выходы которого соединены с входами дешифратора, выход которого соедине с входом генератора импульсов и вто рым входом элемента И, первый вход блока сумматоров соединен с выходом (шифратора дополнительных кодов эталонных контрольных суке введены пер вый и второй блоки элементов И, первые входы второго блока элементов И подключены к выходу блока сумматоров, вторые входы соединены с выходом элемента И, а выходы соединены с входами блока триггеров и и ндикации, одни входы первого блока элементов И соединены с выходами счетчика адреса, а другие являются входом устройства, выходы первого блока элементов И соединены с вторыми входами блока сумматоров. Нафиг. 1 представлена схема предлагаемого устройства; на фиг. 2 закономерность формирования сигналов на вторых .входах первого блока эле- . ментов И для блока постоянной памяти на восемь чисел. Устройство для контроля блоков постоянной памяти содержит генератор 1, шифратор 2 дополнительных кодов эталонных контрольньк сумм, -элемент ИЗ, счетчик 4 адреса, дешифратор 5, блок б сумматоров, блок 7 триггеров и индикации, дополнительные первый и второй блоки элементов И 8 и 9. Первый выход генератора 1 импульсов подключен к входу дешифратора 2 дополнительных кодов эталонных контрольных суьФ1, второй выход генератора 1 импульсов подключен к первому входу элемента И 3 и входу счетчика 4 адреса. Прямые и инверсные выходы счетчика 4 адреса соединены с входами дешифратора 5, выход которого соединен с входом генератора 1 импульсов, и вторым входом элемента И 3. Блок 6 сумматоров первым входом подключен к выходу шифратора 2 дополнительных ходрв эталонных контрольных сумм. Первые входы второго блока элементов И 9 подключены к выходам блока 6 сумматоров, второй вход соединен с выходом элемента ИЗ, а выходы соединены с входами блока 7 триггеров и .-i индикации. Первый блок элементов И 8 первцми входами соединен с выходами проверяемого блока постоянной памяти 10, а вторыми выходами соединел:. с прямыми и инверсными выходами счётчика 4. адреса, выходы первого блока элементов И 8 соединены с вторыми входами блока б сумматоров. Устройство работает следующим образом. I Первый импульс нулевого цикла ге|нератора 1 импульсов поступает на вход шифратора 2 дополнительных кодов эталонных контрольных сумм, с выхода которого дополнительны е коды эталонных полной и частных контрольных сумм поступают Пна й.ервые входы блока б сумматоров. Koii нулевого адреса с выхода счетчика 4 адреса поступает на вход контролируемого блока постоянной памяти. Информация с выхода контролируемого блока постоянной памяти через первые

входы первого блока элементов И 8 .поступает на вторые входы блока 6 сумматоров.

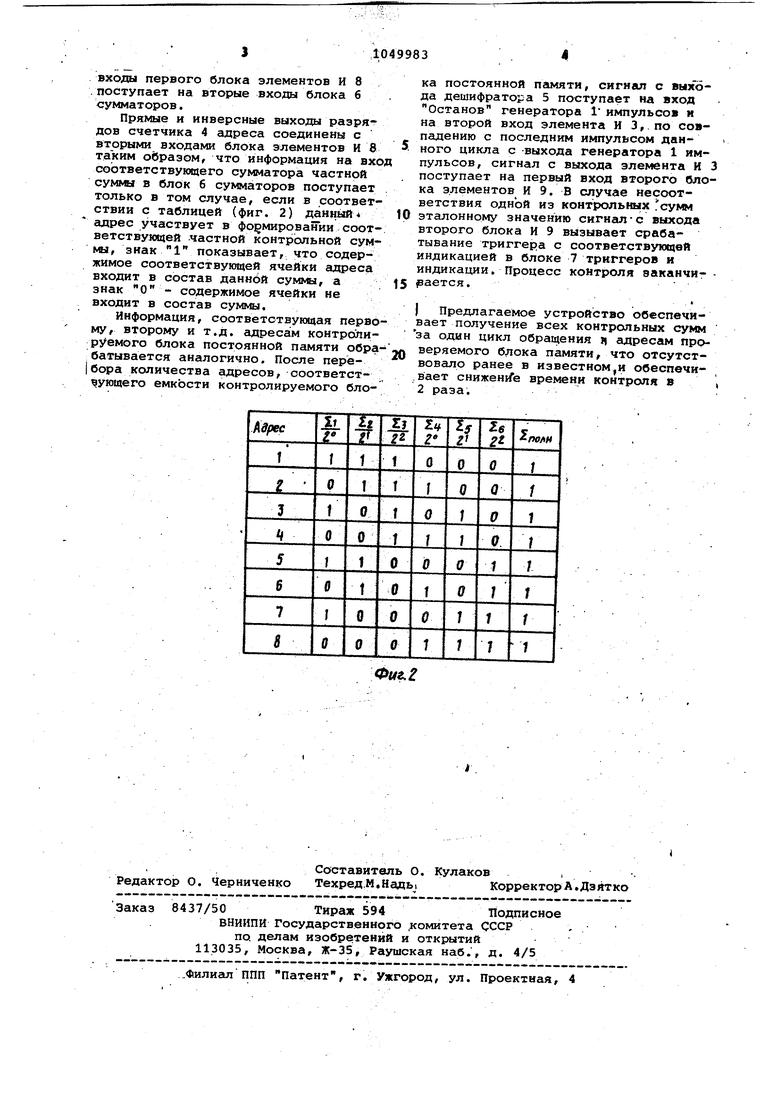

Прямые и инверсные выходы разряд дов счетчика 4 адреса соединены с вторыми входами блока элементов И 8 таким образом, что информация на вход соответствующего сумматора частной сумке в блок б сумматоров поступает только в том случае, если в соответствии с таблицей (фиг. 2) данный сшрес участвует в формировании соот-. ветствующей частной контрольной сумлы, знак 1 показывает, что содержимое соответствующей ячейки адреса входит в состав даннбй суммы, а знак О - содержимое ячейки не входит в состав суммы.

Информация, соответствующая первому, второму и т.д. адресам контро 1Ируемого блока постоянной памяти обрабатывается аналогично. После перё|бора количества адресов, соответст- . дующего емкости контролируемого блока постоянной памяти, сигнал с выхбда дешифратора 5 поступает на вход Останов генератора 1 импульсов и на второй вход элемента И 3,-ПО совпадению с последним импульсом данного цикла с выхода генератора 1 импульсов, сигнал с выхода элемента И поступает на первый вход второго блока элементов И 9. В случае несоответствия одной из контрольных . сумм эталонному значению сигнал-с выхода второго блока И 9 вызывает срабатывание триггера с соответствующей индикацией в блоке 7 триггеров и индикации. Процесс контроля ааканчирается.

- .

) Предлагаемое устройство обеспечивает получение всех контрольных сумм за один цикл обращения ч адресам проверяемого блока памяти, что отсутствовало ранее в известном,и обеспечивает снижение времени контроля в 2 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля блоков постоянной памяти | 1988 |

|

SU1575241A1 |

| Устройство для обучения и контроля знаний обучаемых | 1982 |

|

SU1065869A1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1310904A1 |

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для программного счета витков из гибкого материала | 1985 |

|

SU1298783A1 |

| Адаптивное устройство для защиты памяти | 1983 |

|

SU1103291A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

Фиг, 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля постоянных запоминающих блоков | 1974 |

|

SU510753A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройства запоминающие постоянные | |||

| Методы контроля функционирования | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-09—Подача