Изобретение относится к вычислительной технике и может быть использовано для контроля блоков постоянной памяти в динамическом режиме на рабочей частоте.

Целью изобретения является повышение достоверности контроля.

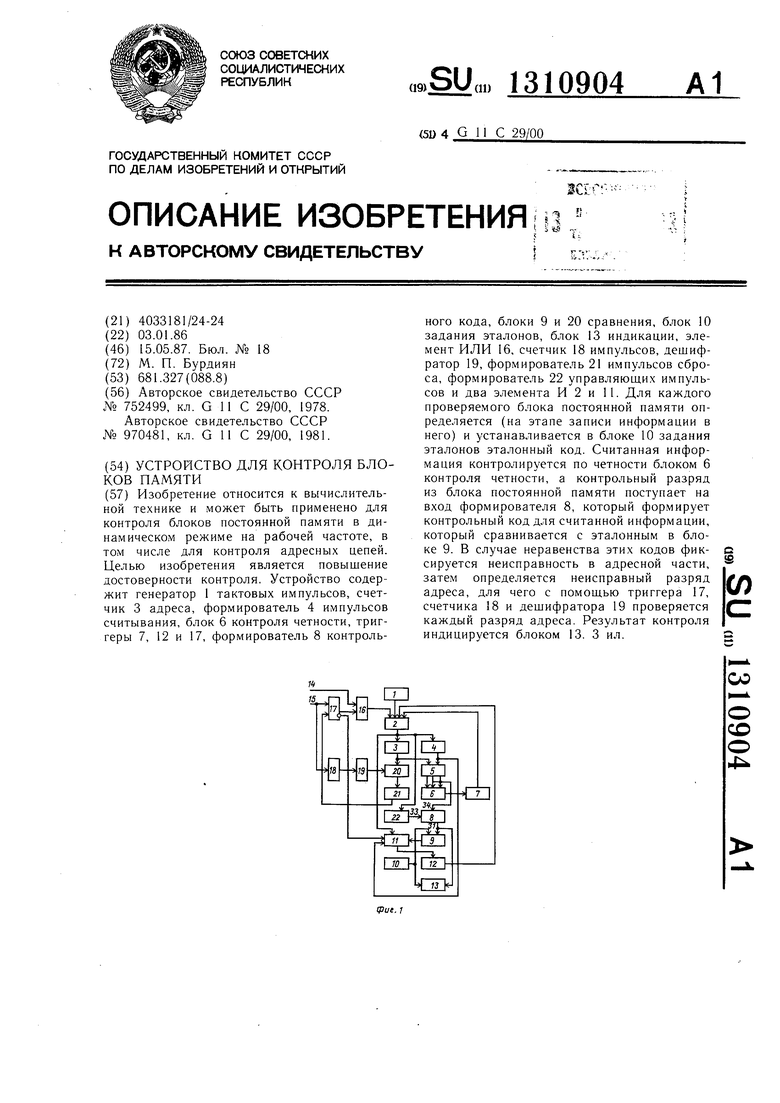

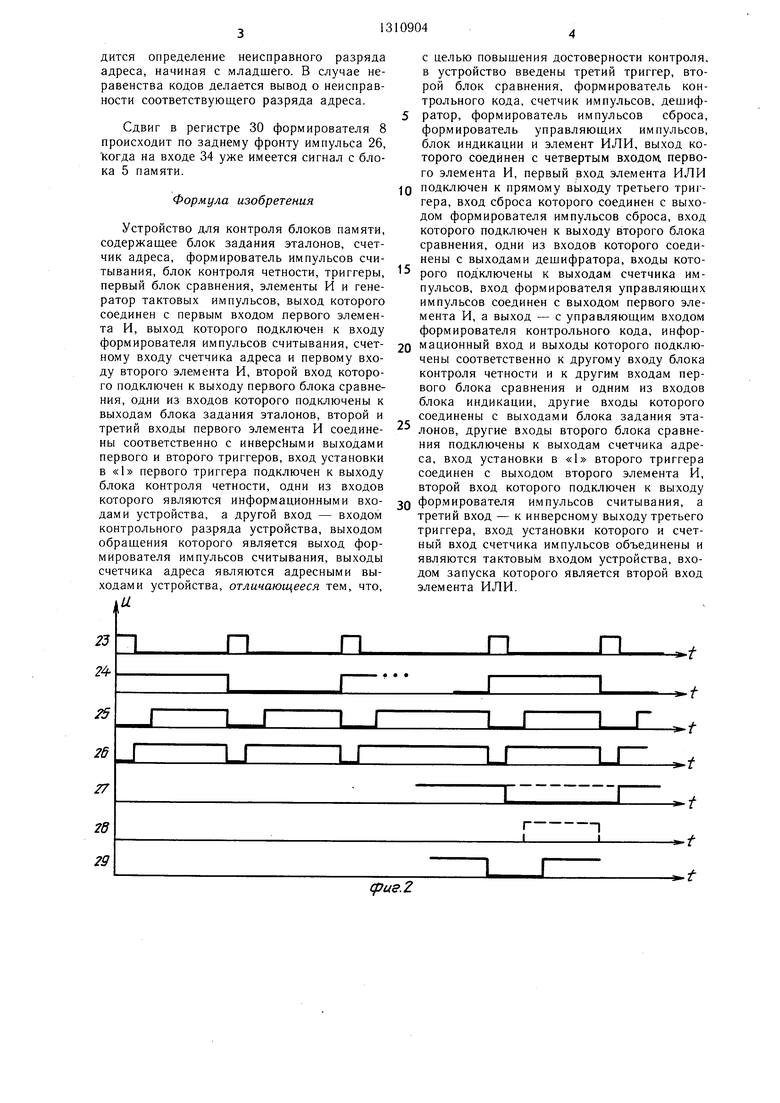

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства; на фиг. 3 - функциональная схема формирователя контрольного кода.

Устройство содержит (фиг. 1) генератор 1 тактовых импульсов, первый элемент И 2, счетчик 3 адреса, формирователь 4 импульсов считывания. На фиг. 1 изображен проверяемый блок 5 постоянной памяти.

Устройство содержит также блок 6 контроля четности, первый триггер 7, формирователь 8 контрольного кода, первый блок 9 сравнения, блок 10 задания эталонов, второй элемент И 11, второй триггер 12, блок 13 индикации. На фиг. 1 обозначены вход 14 запуска и тактовый вход 15 устройства.

Устройство содержит также элемент ИЛИ 16, третий триггер 17, счетчик 18 импульсов, дешифратор 19, второй блок 20 сравнения, формирователь 21 импульсов сброса и формирователь 22 управляюш.их импульсов.

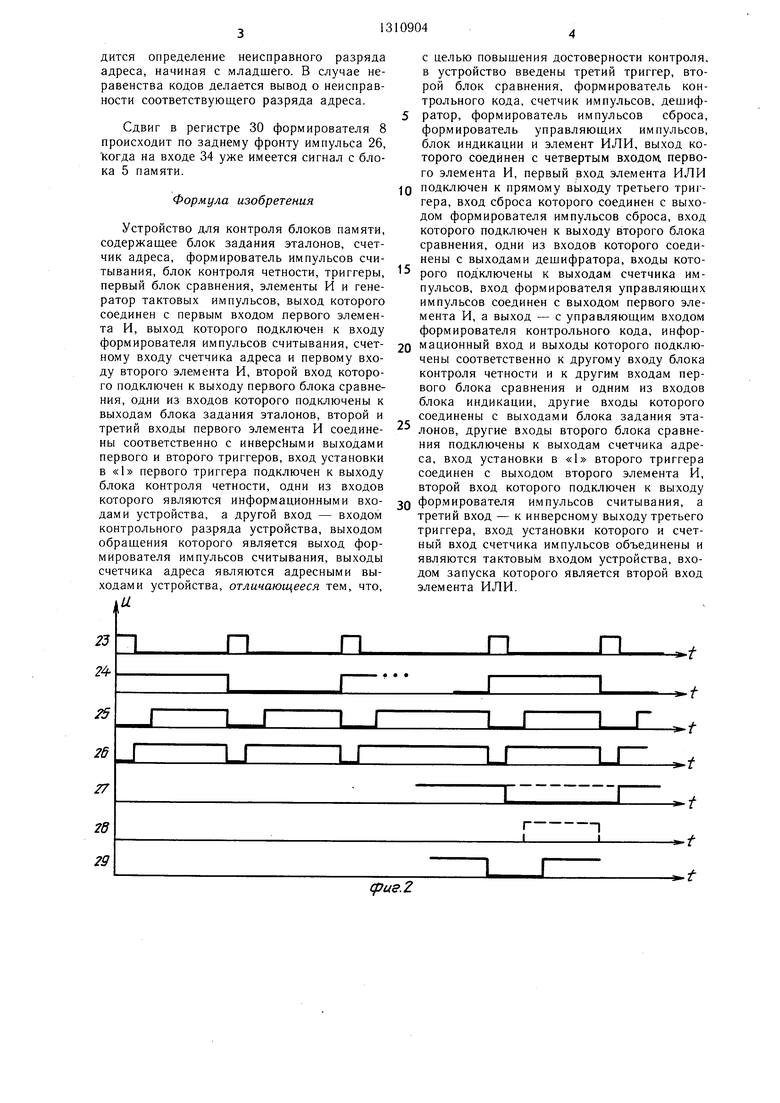

На фиг. 2 показаны импyльcьJ 23 на выходе элемента И 2, импульсы 24 - на выходе счетчика 3, импульсы 25 считывания - на выходе формирователя 4, импульсы 26 - на выходе формирователя 22, импульсы 27 - на выходе блока 9 сравнения, импульсы 28 - на выходе формирователя 21.

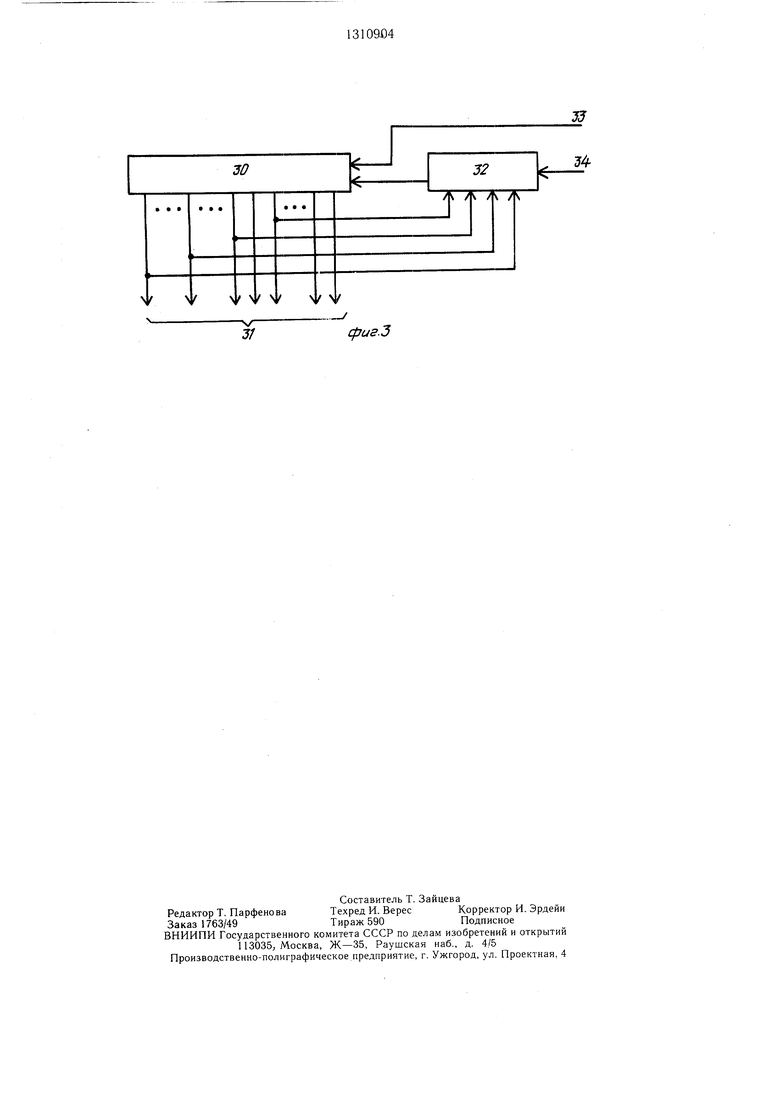

Формирователь 8 контрольного кода содержит (фиг. 3) регистр 30 сдвига с выходами 31, сумматор 32 по модулю два. На фиг. 3 обозначены управляюш,ий 33 и информационный 34 входы формирователя 8. Седьмой девятый, двенадцатый и шестнадцатый выходные разряды регистра 30 соединены с входами сумматора 32.

Устройство работает следуюш,им образом.

Производится начальный сброс устройства (цепи начального сброса не показаны). На вход 14 (фиг. 1) подается сигнал логической «1, который через элемент ИЛИ 16 подается на вход элемента И 2. Импульсы 23 (фиг. 2) с выхода генератора 1 поступают через элемент И 2 на счетчик 3 и формирователь 4. С выходов счетчика 3 код адреса поступает в проверяемый блок 5 (на фиг. 2 показан только импульс 24 младшего разряда адреса). С выхода формирователя 4 в блок 5 поступают импульсы 25 управления. Считанная из блока 5 информация контролируется блоком 6 по четности. В случае четной информации триггер 7 устанавливается в «1, на его инверсном выходе - логической «О, работа устройства прекращается и фиксируется

5

сбой. Контрольный разряд блока 5 поступает на вход 34 формирователя 8, на вход 33 которого с формирователя 22 поступают импульсы 26, в результате чего формирователь 8 начинает формирование контрольного кода. При считывании информации из блока 5 по последнему адресу на выходе формирователя 8 формируется код, равный эталонному коду в блоке 10. Блок 9 сравнива0 ет их и выдает импульс 27, поэтому на выходе элемента И 11 логический «О (импульс 28), и триггер 12 сбоя не фиксирует. В случае неравенства кодов с выходов 31 формирователя 8 и блока 10 блок 9 выдает логическую «1 (импульс 27, показанный на

фиг. 2 пунктиром) и происходит установка в «1 триггера 12. Сигнал с инверсного выхода триггера 12 прекращает работу устройства, и фиксируется неисправность в адресной части. Эталонный код для каждого

0 блока 5 памяти определяется на этапе записи информации в него и устанавливается предварительно в блоке 10. С выхода формирователя 4 сигнал подается также на вход элемента И 11 для того, чтобы по последнему адресу не формировать ложного сигнала сбоя, пока не будет сформирован контрольный код.

Описанный режим позволяет определить исправность или неисправность информационной и адресной части блока 5 памяти.

п В случае обнаружения неисправности адресной части блока 5 памяти для определения неисправного разряда адреса используется режим диагностики. Для этого на входе 14 устанавливается логический «О, а на вход 15 кратковременно подается сигнал

5 логической «1. Происходит установка в «1 триггера 17, и тактовые импульсы начинают поступать на счетчик 3 адреса, формирователи 22 и 4, на выходе элемента И 11 - логический «О. Одновременно происходит прибавление « + 1 в счетчик 18 и, поскольку на первом выходе дешифратора 19 появляется логическая «1, происходит чтение из первой ячейки блока 5. На выходе блока 20 появляется логическая «1 и формирователь 21 вырабатывает импульс 29,

5 по заднему фронту которого триггер 17 сбрасывается и работа устройства прекращается. Далее оператор сравнивает контрольный код на выходе блока 13 с эталонным для младшего разряда адреса. При равенстве кодов кратковременно подается сигнал логичес0 кой «1 на вход 15, описанный процесс повторяется, но информация уже считывается из двух ячеек блока 5 памяти. Сравнивают контрольный и эталонный коды для следующего разряда адреса и т. д. Количество

г сравнений, необходимых для диагностики адресной части блока 5 памяти, равно количеству разрядов адреса, что значительно меньше, чем применение эталона с равным объемом памяти. Таким образом произво0

дится определение неисправного разряда адреса, начиная с младшего. В случае неравенства кодов делается вывод о неисправности соответствующего разряда адреса.

Сдвиг в регистре 30 формирователя 8 происходит по заднему фронту импульса 26, когда на входе 34 уже имеется сигнал с блока 5 памяти.

Формула изобретения

Устройство для контроля блоков памяти, содержащее блок задания эталонов, счетчик адреса, формирователь импульсов считывания, блок контроля четности, триггеры, первый блок сравнения, элементы И и генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, выход которого подключен к входу формирователя импульсов считывания, счетному входу счетчика адреса и первому входу второго элемента И, второй вход которого подключен к выходу первого блока сравнения, одни из входов которого подключены к выходам блока задания эталонов, второй и третий входы первого элемента И соединены соответственно с инверсными выходами первого и второго триггеров, вход установки в «1 первого триггера подключен к выходу блока контроля четности, одни из входов которого являются информационными входами устройства, а другой вход - входом контрольного разряда устройства, выходом обращения которого является выход формирователя импульсов считывания, выходы счетчика адреса являются адресными выходами устройства, отличающееся тем, что.

0

5

с целью повыщения достоверности контроля, в устройство введены третий триггер, второй блок сравнения, формирователь контрольного кода, счетчик импульсов, дешифратор, формирователь импульсов сброса, формирователь управляющих импульсов, блок индикации и элемент ИЛИ, выход которого соединен с четвертым входом, первого элемента И, первый вход элемента ИЛИ подключен к прямому выходу третьего триггера, вход сброса которого соединен с выходом формирователя импульсов сброса, вход которого подключен к выходу второго блока сравнения, одни из входов которого соединены с выходами дешифратора, входы которого подключены к выходам счетчика импульсов, вход формирователя управляющих импульсов соединен с выходом первого элемента И, а выход - с управляющим входом формирователя контрольного кода, информационный вход и выходы которого подключены соответственно к другому входу блока контроля четности и к другим входам первого блока сравнения и одним из входов блока индикации, другие входы которого соединены с выходами блока задания эталонов, другие входы второго блока сравнения подключены к выходам счетчика адреса, вход установки в «1 второго триггера соединен с выходом второго элемента И, второй вход которого подключен к выходу 0 формирователя импульсов считывания, а третий вход - к инверсному выходу третьего триггера, вход установки которого и счетный вход счетчика импульсов объединены и являются тактовым входом устройства, входом запуска которого является второй вход элемента ИЛИ.

0

5

JZ7

/

N V

f f

N/

J/

J2

n

ериг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU970481A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

Изобретение относится к вычислительной технике и может быть применено для контроля блоков постоянной памяти в динамическом режиме на рабочей частоте, в том числе для контроля адресных цепей. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор 1 тактовых импульсов, счетчик 3 адреса, формирователь 4 импульсов считывания, блок 6 контроля четности, триггеры 7, 12 и 17, формирователь 8 контрольного кода, блоки 9 и 20 сравнения, блок 10 задания эталонов, блок 13 индикации, элемент ИЛИ 16, счетчик 18 импульсов, дешифратор 19, формирователь 21 импульсов сброса, формирователь 22 управляющих импульсов и два элемента И 2 и II. Для каждого проверяемого блока постоянной памяти определяется (на этапе записи информации в него) и устанавливается в блоке 10 задания эталонов эталонный код. Считанная информация контролируется по четности блоком 6 контроля четности, а контрольный разряд из блока постоянной памяти поступает на вход формирователя 8, который формирует контрольный код для считанной информации, который сравнивается с эталонным в блоке 9. В случае неравенства этих кодов фиксируется неисправность в адресной части, затем определяется неисправный разряд адреса, для чего с помош.ью триггера 17, счетчика 18 и дешифратора 19 проверяется каждый разряд адреса. Результат контроля индицируется блоком 13. 3 ил. (Л

| Устройство для контроля памяти | 1978 |

|

SU752499A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU970481A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-03—Подача