Изобретение относится к вычислительной технике и предназначено для использования в качестве одного из элементов управления матрицей памяти интегрального запоминающего устройства с произвольной выборкой информации.

Известны многоканальные дешифраторы, состоящие из входных и выходных дещифрирующих каскадов 1.

Недостатками дешифраторов являются сложность построения, низкая степень интеграции на кристалле и значительное потребление мощности.

Известен также дешифратор, состоящий из симметричного входного каскада,, содержащего в каждом из двух-каналов переключающий и инвертирующий П-р-ц транзисторы с объединенными между каналами эмиттерами, и выходного каскада, содержащего в каждой из четырех групп П-р-П транзисторы и инжектирующие p-fi-p транзисторы с объединенными базами, причем коллекторы р-п-р транзисторов каждой группы соединены с базой выходного Л-ру транзистора той же группы, а также содержащий щины питания, нулевого потенциала, две входные и четыре выходные щины, при этом коллекторы выходных /7-р-/1транзисторов каждой группы соединены с соответствующей выходной шиной, а эмиттеры всех инжектирующих р-п-р транзисторов связаны с шиной питания 2.

Не.аостатком его является сравнительно невысокое быстродействие и низкая нагрузочная способность.

Цель изобретения - повышение быстродействия и нагрузочной способности устройства.

Эта цель достигается тем, что в дещифраторе, состоящем из симметричного входного каскада, содержащего в каждом из двух каналов переключающий и инвертирующий/г-/7-/г транзисторы с объединенными между каналами эмиттерами, и выходного каскада, содержащего, в каждой из четырех групп п-р-П транзисторы и инжектирующие р-Пгр транзисторы с объединенными базами, причем коллекторы р-П-р транзисторов каждой группы соединены с базой выходного 1-р-п транзистора той же группы, а также содержащий шины питания, нулевого потенциала, две входные и четыре выходные щнны, при этом коллекторы выходных/г-р-/г транзисторов каждой группы соединены с соответствующей выходной щиной, а эмиттеры всех инжектирующих р-П-р гранзисторов связаны с шиной питания, база переключающего транзистора подключена к коллектору первого инжектирующего транзистора и к соответствующей входной шине, объединенные эмиттеры переключающих и базы первых инжектирующих транзисторов соединены с объединенными эмиттерами инвертирующих и базами вторых инжектирующих транзисторов и с шнной нулевого по

тенц11ала, коллекторы инвертирующих тран зисторов каждого из каналов связаны с соответствующим объединением базы П-р-П и Коллектора р-п-р выходных транзисторов, коллекторы переключающих транзисторов каждого из каналов соединены с соответствующим объединением базы инвертирующего и коллектора второго инжектирующего транзисторов того же канала и с соответствующим об ъединение.м базы/г-р-/ги коллектора p-fi-p выходных транзисторов, причем эмиттеры/1-р-/т.базы и базы р-гьр выходных транзисторов попарно объединены и соединены с шиной нулевого потенциала, а объединенные попарно коллекторы выходных/t-p-. транзисторов подключены к соответствующей выходной шине.

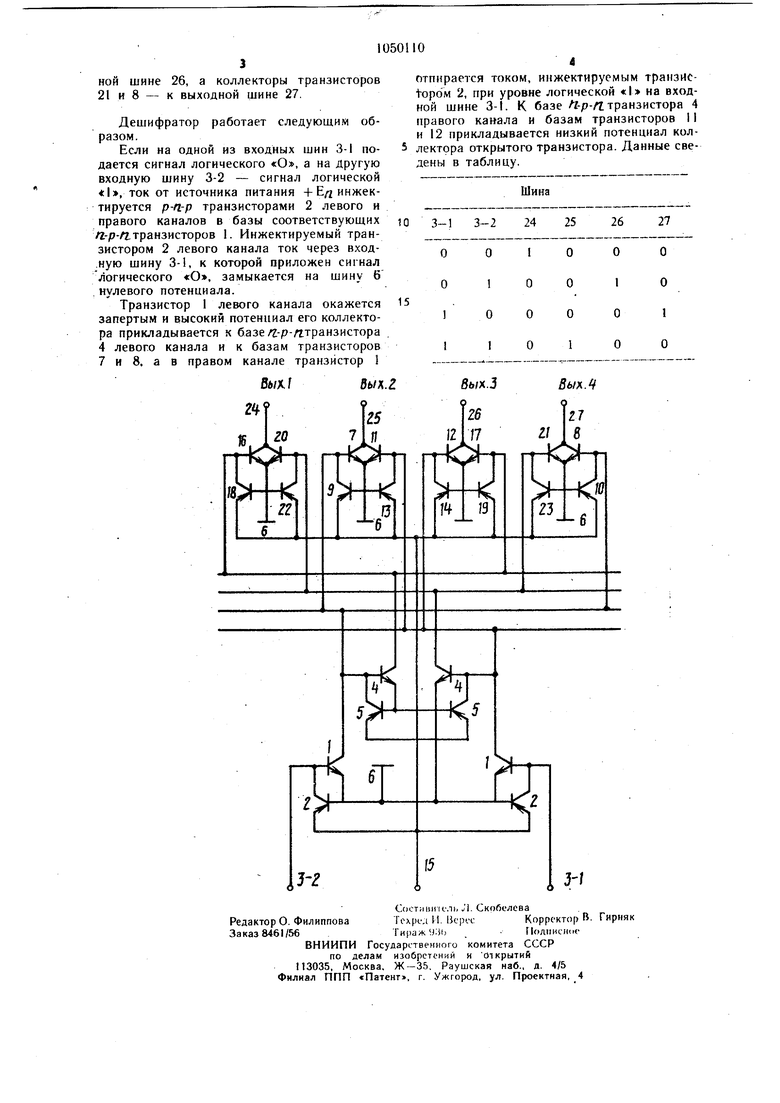

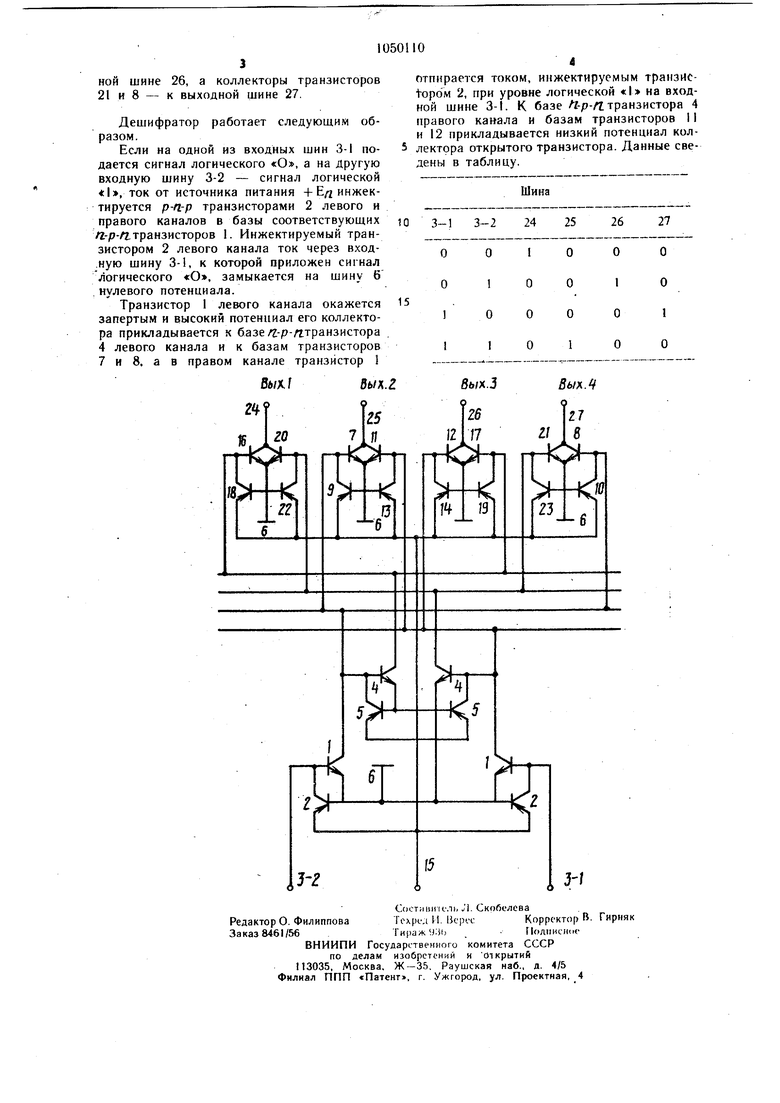

На чертеже показано предлагае.мое устройство.

Дешифратор содержит в каждом канале входного каскада переключающий транзистор 1, эмиттер которого объединен с базой первого инжектирующего р-п-р транзистора 2. База переключающего транзистора I объединена с коллектором транзистора 2 и подсоединены к соответствующей входной шине 3-1 и 3-2. Ба.эы первых инжектирующих транзисторов 2 обоих каналов со аннены с эмиттерами транзисторов I и подсоединены к объединенным эмнтер ру fl-p-ft инвертирующего транзистора 4 и соединенным между собой базам вторы.х инжектирующих р-п-р транзисторов 5 обоих каналов, а также к шине 6 нулевого гю.тенциала. Коллектор переключающего транзистора I соединен с базой инвертирующего транзистора 4 и с коллектором второго инжектирующего транзистора 5 того же канала, а также с объединением баз А7-р-/7 транзисторов 7 и 8, и коллекторов р-п-р выходных транзисторов 9 и 10 для левого канала входного каскада и соответственно с объединением баз п-р-п транзисторов 11 и 12 и коллекторов р-п-р выходных транзисторов 13 н И для правого канала входного каскада. Эмиттеры первых инжектирующих р/г-р транзисторов 2 обоих каналов присоединены к шине 15 питания. Коллекторы транзисторов 4 подсоединены к объединениям баз/г-рл и коллекторов р-п-р выходных транзисторов 16-19 для левого канала входного каскада и соответственно к объединениям баз n-p-fi и коллекторов p-ti-p выходных транзисторов 20-23 для правого канала входного каскада.

Эмиттеры транзисторов 5, 9, 10, 13, 14, 18, 19, 22 и 23 связаны с шиной 15 питания. Эмиттеры и базы транзисторов 16 и 20, 18 н 22, 7 и II, 9 и 13, 12 и 17, 14 и 19, 8 и 2, 10 и 23 объединены попарно и подсоединены к шине 6 нулевого потенциала коллекторы транзисторов 16 и 20 подключены к выходной шине 24. коллекторы транзисторов 7 н II - к выходной шине 25, коллекторы транзисторов 12 и 17 - к выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1975 |

|

SU610298A1 |

| Формирователь импульсов | 1975 |

|

SU656192A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU693434A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Устройство для пожарной сигнализации | 1977 |

|

SU669373A1 |

| Коммутатор | 1977 |

|

SU684742A1 |

| Дифференциальный усилитель | 1981 |

|

SU1083341A2 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

| Аналоговый N-канальный коммутатор широкополосных видеосигналов | 1988 |

|

SU1598153A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

ДЕШИФРАТОР; состоящий иЛ симметричного входного каскада, содер жащего в каждом из двух каналов переключающий и инвертирующий п-р-п транзисторы с объединенными между каналами эмиттерами, и выходного каскада, содержащего в каждой из четырех групп/г-р-А транзисторы и иижектирующне р-п-р транзисторы с объединенными базами, причем коллекторы р-л-р транзисторов каждой группы соединены с выходногол-р-/1ТранЯйсгбратб же группы, а такЖе содержа1а1ЯЙ шияы питания, нулевого потенциала, , входные н четыре выходные Шины, при этом к оллекторы выходных л -р-п транзисторов каждой группы соединены с соответствующей выходной щиной, а эмиттеры всех инжектирук щих рц-р транзисторов связань с шиной питания, отличающийся тем, что, : с целью повышения быстродействия и нагру. зочной способности, база переключающего транзистора подключена к коллектору первого инжектирующего транзистора и к соответствующей входной щиие, объединенные эмиттеры переключающих и базы первых инжектирующих транзисторов соединены с объединенными эмиттерами инвертирующих с базами втбрых инжектирующих транзисторов и с щиной нулевого потенциала, коллекторы нивертнрующих транзисторов каждого из каналов связаиы с соответствующим : объединением базы п-р-п н коллектора р-п-р Выходных транзисторов, коллекторы переключающих транзисторов каждого из ка налов соединены с соответствующим объеi динением базы инвертирующего и коллекто ра второго инжектирующего траизисторов СЛ . того же канала и с соответствующим объединеннем базып-р-п коллектора р-п-р выхо-. дных транзисторов, причем эмиттеры п-р-П и базы р-п-р выходных транзнсторов по: парно объединены н сЬед

| I | |||

| Каталог электронных схем фирмы «Texas instruments std | |||

| England, 1971, pp | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-10-23—Публикация

1977-05-19—Подача