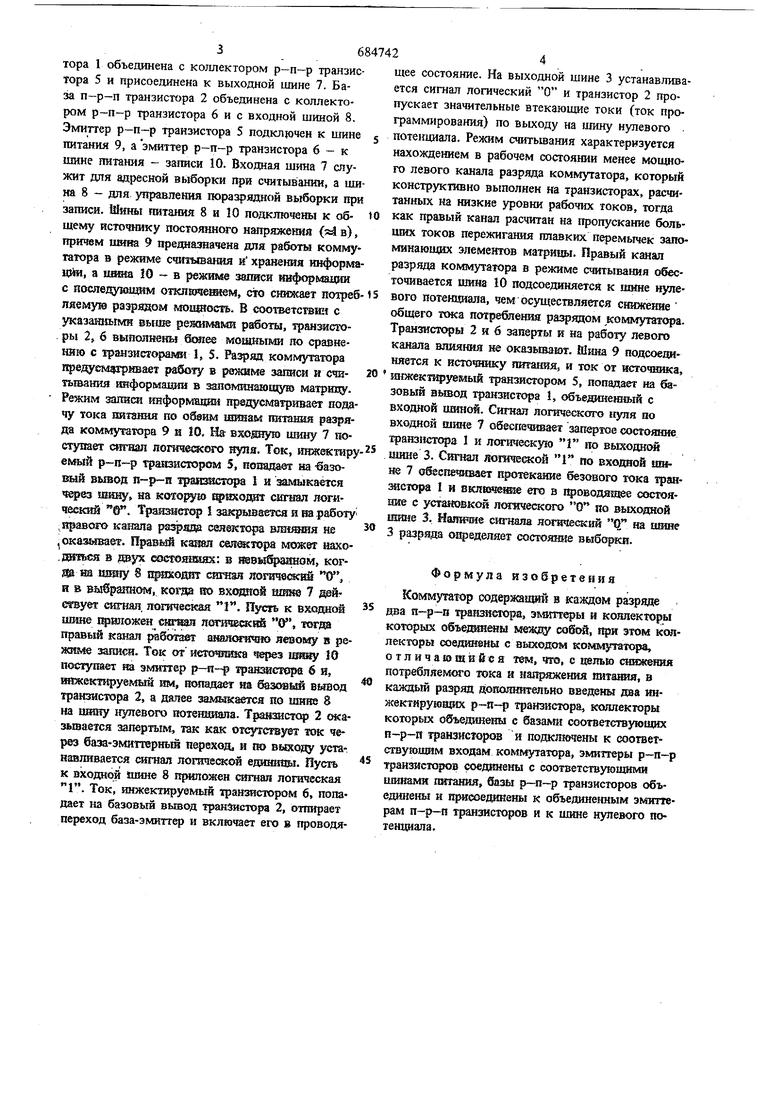

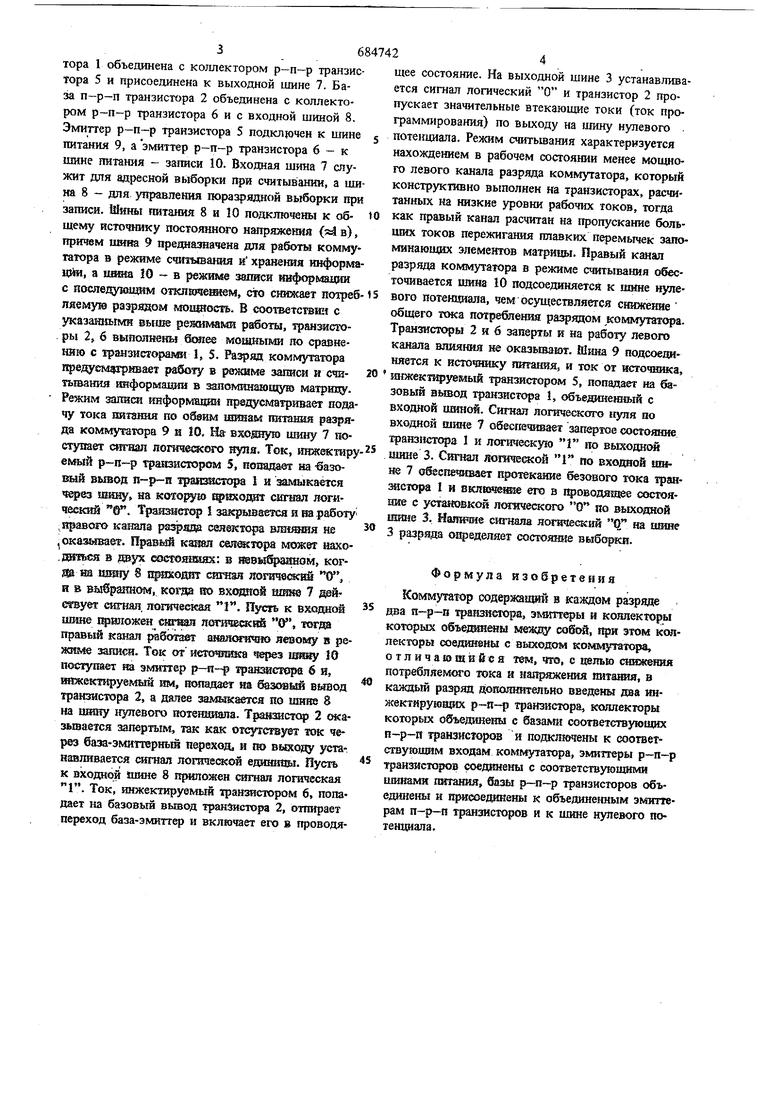

Изобретение касается вычислительной техш1ки. Оно преда азиачено, например, для управления матрицей постоянного, электрически программируемого запоминающего устройства про- извольной емкости. Известен коммутатор, каждый разряд которого выполнен на двух п-р-п транзисторах и резисторах, причем змиггеры транзисторов объединены между собой и соединены с ншной нулевого потенциала, коллекторы также объединены между собой и подключены к выходу устройства и через резистор - к шине питаюш, а базы транзисторов связаны через резисторы с соответствующими входами селектора. К недостаткам данного устройства относятся сравнительно высокое напряжение питания и высокое потребление тока от источютка питания. Известен также коммутатор содержащий в каждом разряде два п-р-п транзистора, эмшхеры и коллекторы которых объединены, при этом коллекторы, подключены к выходу коммутатора Однако этот коммутатор также имеет высоко напряжение питания и повышенное потребление тока. Цель изобретешь - снижение потребляемого тока и напряжения питания. Это достигается тем, что в коммутатор, содержащий в каждом разряде два п-р-н траюистора, эмиттеры и коллекторы которых объединены между собой, при зтом коллекторы соедииешл с выходом коммутатора, в каждый разряд дополтйггельно введены два инжектирующих р-п-р транзистора, коллекторы которых объединены с базаш соответствумщюс п-р-н транзисторов и подключены к соответствующим входам коммутатора, эмиттеры р-п-р транзисторов соединены с соответствуюиасми шинами питакия, базы р-п-р транзисторов объединены и присоединены к объединенным эмиттерам п-р-п транзисторов и к шине нулевого потенциала. На чертеже приведена принцнп1 алъная схема коммутатора. В разряде коммутатора котшекторы п-р-п транзисторов 1 и 2 объединены и соединены с вь ходной шиной 3. Э.миттеры этих же транзисторов объединены и соединены с шиной нулевого потенциала 4нс базами ннжекгируюших р-п-р транзисторов 5 и 6. База п-р -п транзистора 1 объединена с коллектором р-п-р транзистора 5 и присоединена к выходной шине 7. База п-р-п транзистора 2 объединена с коллектором транзистора бис входной шиной 8. Эмиттер р-п-р транзистора 5 подключен к шине питания 9, а эмиттер транзистора 6 - к шине питания - записи 10. Входная шина 7 служит для адресной выборки при считывании, а шина 8 - для управления поразрядной выборки при записи. Шины питания 8 и 10 подключб{а1 к общему истошику постоянного напряжения {я4 в), причем игаш 9 предаазначена для работы коммутатора в режиме счшъшашш и хршгешгя информации, а шша 10 - в режиАве записи информации с последующим отключешем, сто снижает потребяяему® разрядом моошоста. В соответстви:{ с указанньгмн выше режимами работы, транжеторы 2, б выполнены &)see мощными по сравнению с JTpaHSHCTopaivffi 1, 5. Разряд коммутатора предусматривает работу в рзяшме зашгси и считывания информахдац в ззпомшшощуго ма-фш. Режим записи информации itpectycMaipHBaet подачу тока витзния по обеим ишнам Ш{таЕшя разряда коммутатора 9 и 10. На входауго шину 7 ноетунает с ггиал лоти окого нуля. Ток, инжекшру емый р-п-р транзистором 5, ношдавт на базовый вывод п-р-и траизастора 1 и замыкается Шйну, на которую ЕЩ йходат сштл логический б. Тршш1етор закрывается и гоработу .правого ктяпа psspsi сеяекто|т вяшгшя не оказывает. кзшл сш жторз может нахо, даться в рвух аэетояшшх: в яваыбрзшом, ког® ш №smfy 8 яртходйт снпшя яогичвокй О, R в BbtSparaiOM, когда ко входной шш№ 7 дейetsyet Сигнал, логическая 1. Пусть к входной шине прйиожен &№тя логический О, тогда правый канал { ботзвт яе0ому в режйме задней. Ток о йеточшаса через 10 поступает на эмиттер р-й--р грая стора 6 я, ш же спфуемый им, попадает ш 6030S{| EI вывод транзистора 2, а далее замыкается по шине 8 на цншу нулевого нотендаапа. Трашистор 2 оказывается запертым, так как отсутствует ток через бай-змиттерный переход, и по вьвищу устанавливается шгнал логаческой едавшщл. Пусть к входной агане 8 приложен оптяая логическая 1. Ток, ишкектируемьй чранзястором 6, попадает на базовый вьтод транзистора 2, отпирает переход база-эмиттер и включает его 8 гфоводящее состояние. На выходной шине 3 устанавливается сигнал логический О и транзистор 2 проускает значительные втекающие токи (ток программирования) по выходу на 1лину нулевого . потенциала. Реясим считьшания характеризуется нахождением в рабочем состоянии менее мощного левого канала разряда коммутатора, который конструктивно выполнен на транзисторах, расчитанных на низкие уровни рабочих токов, тогда как правый канал расчитан на 1 пускание больших токов пережигания плавких перемычек запоминающих элементов матрицы. Правый канал разряда коммутатора в режиме считывания обесточивается шина 10 подсоединяетсй к шине нулевого потенциала, чем осуществляется снижение общего кжа потребления разрядом коммутатора. Транзисторы 2 н б заперты н на работу левого канала влияния не оказьшают. Шша 9 подсоединяется к истоадику питшшя, я ток от источника, шшекпфуек ый транзистором 5, попадает на базовый вывод транзистора 1, объеданешпяй с входной иошой. Сигнал логическотчэ суля по входной шине 7 обеспечивает запертое состояние транзистс а 1 и логическую 1 по выходной шине 3. Сигнал логачеекоЙ 1 по входной шине 7 обеспечивает протекание базового тока транзистора 1 и Бключйше его в проводящее состояаие с устайоВкой лошческого О яо выхсздной Шине 3. Наядаие сигнала яогнче жий О на шине 3 разряда снфеделяет состояние выберси. Формула изобретения Коммутатор содерязщяй в каждом разряда два п-р-п трашйегора, эмштеры и коялекторы которых объедяйшы между собой, этом ксялекгоры совдга1еиы с выходом коммутатора, отличаю щи йен тем, чте, с дапью снижения потребляемого тока н напряжения шташм, в каждый разряд дополишепьно введены два ннжектируювдак р-п-гр транзистора, к««шекторы которых объединены с базалш соответств тощих и-р-п транзисторов и подключены к соответствуголцим входам коммутатора, эмиттеры р-п-р транзисторов соединены с соответств)то1цими Евшамя питания, базы р-п-р транзисторов объединены и пртсеоедннены к объединенным эмиттерам п-р-п транзисторов и к шине нулевого потенциала.

н

-н

-

Ч

-

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1975 |

|

SU610298A1 |

| Логическое устройство | 1977 |

|

SU738171A1 |

| Дешифратор | 1975 |

|

SU547968A1 |

| Формирователь импульсов | 1975 |

|

SU656192A1 |

| Запоминающий элемент | 1975 |

|

SU561221A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU693434A1 |

| Дешифратор | 1977 |

|

SU1050110A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| Счетный триггер | 1980 |

|

SU924835A1 |

-f6i- -о- -фн

о

«

-1бь

-ОL-ZIIJ

«

Авторы

Даты

1979-09-05—Публикация

1977-04-14—Подача