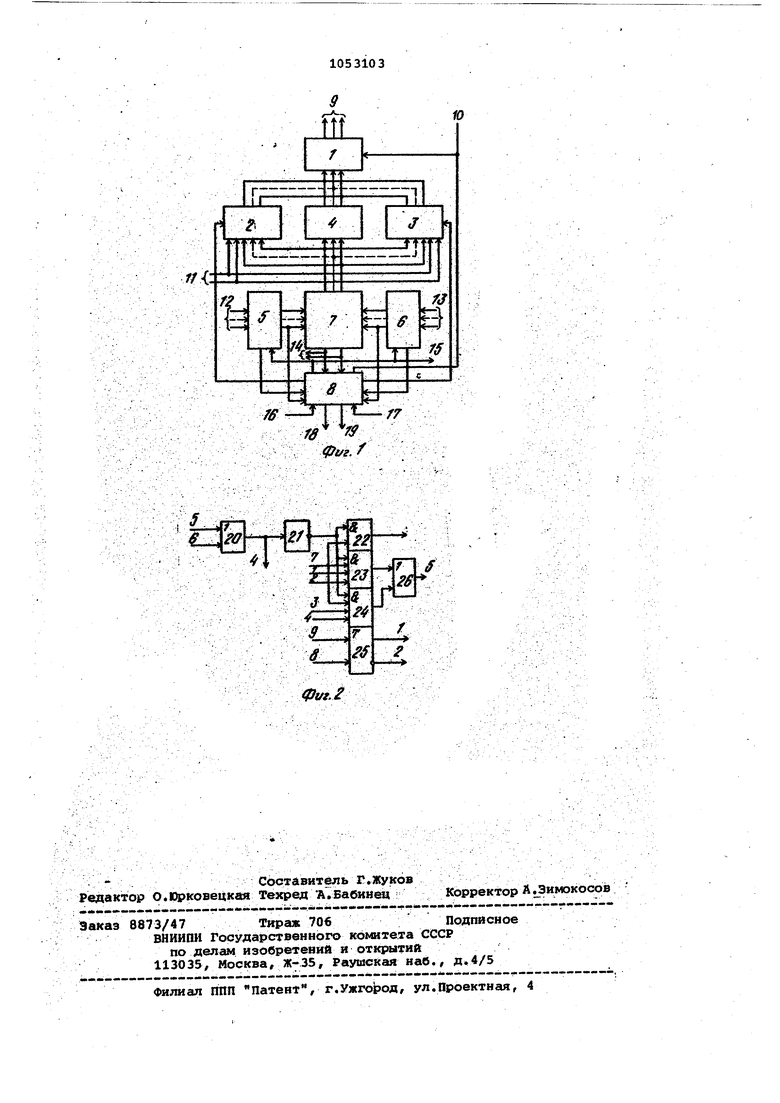

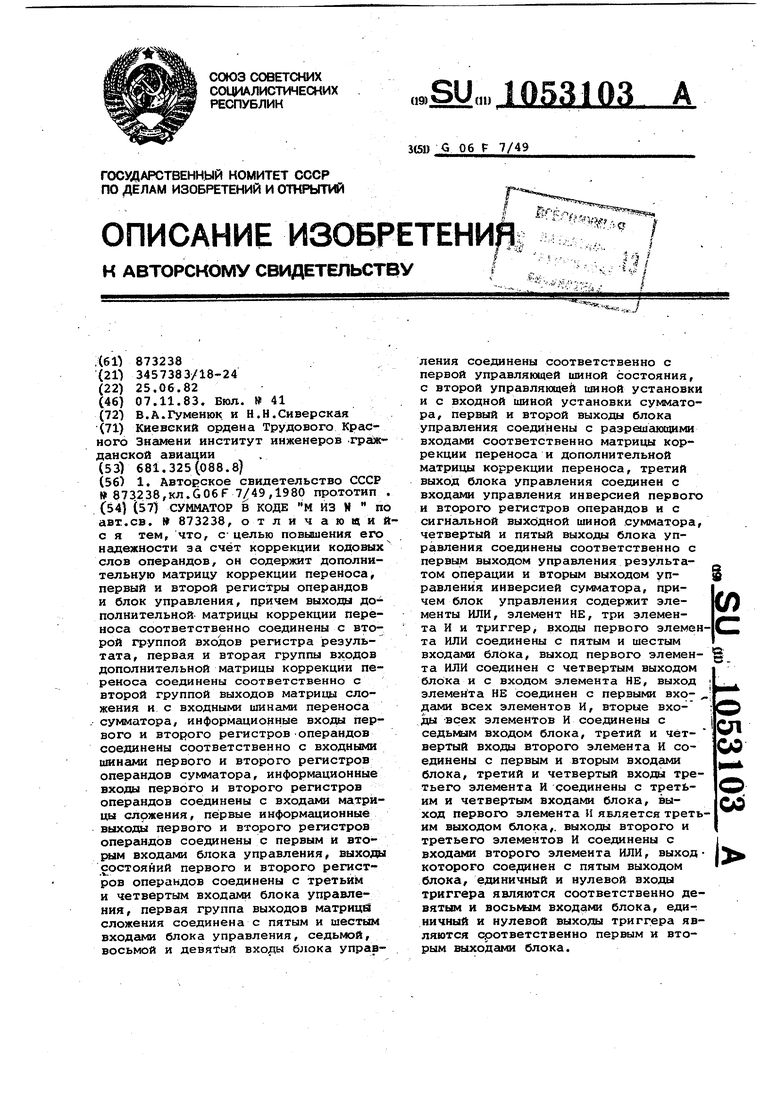

Изобретение относится к вычислительной технике и предназначено для суммирования чисел, представленных в коде М из N (где Н - количес во позиций в кодовом слове,. М - .количество единиц в кодовом слове). По основному авт.св. № 873238 из-вестен сумматор в коде М из N содержащий регистр результата, матрицу сложения, матрицу коррекции переноса и блок коммутации, причем входы матрицы сложения соединены Со ответственно с входными шинами первого и второго операндов сумматора, выходы ;регист|Э1а1 результата - с выходными тинами сумматора, первая группа входов регистра результата соединена с входной шиной установки сумматора, первая группа выходов матрицы сложения - с выходными шина сумматора, вторая группа выходов матрицы сложения - с первой группой входов матрицы коррекции переноса., те из этих-выходов, которым соответ ствуют независимые от переноса неповторяю1даеся позиции в кодовых ело вах всех возможных результатов, сое динены непосредственно с соответстВУЮ1ЦИМИ входами второй группы входо регистра результата, другие выходы второй группы выходов матрицы ело.жения, которым соответствуют независимые от переноса повторяющиеся позиции в кодовых словах всех возможных результатов, соединены с вхо дами блока коммутации, выходы блока коммутации соединены с соОтветствуЮШИМИ входами второй группы входов регистра результата, вторая группа входов матрицы коррекции переноса .соединена с входными шинами переноса сумматора Щ . Недостатком устройства является то, что возникновение неисправносте например обрыв любой связи в матрице слоясения, содержащей большую часть элементов устройства, приводи к потере функциональной полноты пос ледним, т.е. к выходу из строя всего устройства. .Целью изобретения является повы..шение надежности сумматорй в коде М из N за счет коррекции кодовых слов операндов. Поставленная цель достигается тем что сумматор в коде М из N содержит дополнительную матрицу коррекции переноса, первый и второй ре гистры операндов и блок управления, причем выходы дополнительной матрицы коррекции переноса Соответственно соединены с второй группой входо регистра результата, первая и втора группы входов дополнительной матрицы коррекции переноса соединены соответственно с второй группой выходов матрицы сложения и с входными ш нами переноса сумматора, информационные входы первого и второго регистров операндов соединены соответственно с входными шинами первого и второго резгистров операндов сумматора, информационные входы первого и второго регистров операндов соединены с входами матрицы сложения, первые информационные выходы первого и второго регистров операндов соединены с первым и вторым входами блока управления, выходы состояний первого и второго регистров операндов соединены с третьими четвертьм входами блока управления, первая группа выходов матрицы сложения соединена с пятым и шестым входшл блока управления, седьмой, восьмой .и девятый входы блока управления соединены соответственно с первой управляющей шиной СОСТОЯНИЯ, с второй управляющей шиной установки и с входной, шиной установкги сумматора, первый и второй выхода блока управления соединены с разрешающими входами соответственно матрицы коррекции переноса и допол нитедьной Матрицы коррекции переноса, третий выход блока управления соединен с входами управления инверсией первого и второго регистров операндов и с сигнальной выходной шиной сумматора, четвертый и пятый выходы блока управления соединены соотвеТс вейно с первым выходом управления результатом операции и вторым выходом;управления инверсией сумматора, причем блок управления содержит элементы или, элемент НЕ, три элемента И и триггер, входы первого элемента ИЛИсоединены с пятым и шестым входами блока, вьисод первого элемента ИЛИ соединен с четвертым выходом блока и с входом элемента НЕ, выход элемента НБ .соединен з первыми входами всех элементов И, входы всех элементов и соединены с седьмым входом блока. Третий и четвертый входаа второго элемента И соединены с первым и вторым входами блока третий и четвертый входы третьего элемента И соединены с третьим и четвертым входами блока, выход п рвогО элемента И Является Т ретьим выходом блока, выходы второго и третьего элементов И соединены с входами второго элемента или, выход которого соединен с пятым выходом блока, единичный и нулевой входы триггера являются соответственно девятым и восьмым входшл блока, единичный и нулевой выходы триггера - первым и вторЕйм выходс1Ми блока. . На фиг.1 изображена блок-схема, сумматора в коде М N ; .2схема блока управления. °Сумматор фиг. содержит рематрицу 2 коргистр 1 результата. рекции переноса, дополнительную матрицу 3 коррекции переноса, блок 4. коммутации, первый 5 и второй б регистры операндов, матрицу 7 сложения блок 8 управления, выходную шину 3 сумма, входную шину 10 установки, входную шину 11 переноса, входные шины 12 и 13 первого и второго операндов, выходную шину 14 переноса/, сигнальную Выходную шину 15, первую. управляющую шину 16 состояния, з торую управляющую шину 17 установки, первый выход 18 управления результатом olieрадии, йторой выход 19 управления инверсией.. ; : . : , ... , , j Выйодырегистра 1 результата соединены с выходными шинами 9 суммы устройства, первая группа входов регистра 1 результата соединена с вход ной шиной 10 установки сумматора, с этой же шиной соединен девятый вход блока 8 управления, выходы матрицы 2 коррекции переноса, дополнительной матрица 3 коррекции переноса и блока 4 коммутации соответственно соединены с второй группой входов регистра Iрезультата, входы матрицы 2 коррекции переноса и вторые группы входов ; дополнительной матрицы 3 коррекции переноса соединены с входными шинами IIпереноса сумматора, информационные входы первого 5 и второго 6 регистров операндов соединены соответственно с г ;входными шинами 12 и J.3 первого и второ; то. регистров операндов сумматор а, и к формационные выходы первого 5 и второго 6 регистров операндов соединены с входами матрицы 7 сложения, первые информационные выходы первого и второго регистров операндов соединены с первым и вторым входами блока 8 управ ления, выходы состояний первого 5 и второго б регистров операнд 1ов соединены с третьим и четвертым входами блока 8 управления, первая группа выходов матрицы 7 сложения соединена с первыми группами входов матрицы 2 коррекции переноса и дополнительной матрицы 3 коррекции переноса и с. входами блока 4 коммутации, первая группа выходов матрицы 7 сложения -соединена с пятым и шестым входами ,блока 8 управления и с выходными шинами 14 переноса сук 4атора, разрешающие входы матриц 2 коррекции переноса и дополнительной матрицы 3 коррекции переноса соединены соответствен но -С первым и вторым выходами блока 8 управления, третий выход блока В управления соединен с входами упрадления. инверсией первого 5 и второго 6 регистров операндов и с сигнальной выходной шиной 15 сумматора, седьмой и восьмой входы блока 8 управления соединена соответственно с первой уп ;равляющей шиной 16 состояния и второй управляющей шиной 17 установки сумматора, четвертый и пятый выходы блока 8 упра вления соединены соответственно с первым выходом 18 управления результатом операции и вторым выходом 19 управления инверсией сумматора. Регистр 1 результата представляет собой группу из М триггеров, единичные входы которых образуют первую группу входов, а нулевые вторую группу входов регистра 1 результата. Единичные выходы триггеров образуют группу выходов регистра 1 результата. Матрица .2 коррекции переноса и дополнительная матрица 3 коррекции переноса представляют собой прямоугольные матрицы элементов И, кажгдый из которых имеет по три входа. Такая матрица имеет размеры: 2р (содержит р пар элементов и), где р - основание системы счисления. Первые ВХОФ1 элементов И матрицы, составляющих нечетные пары, соединены с одноименными входами первой группы входов матрицы. Первые входы элементов И матрицы, составляющих дечетные пары,соединены с одноименными входами первой группы входов латрицы; Первые входы элементов И гатрицы, составляющих четные пары, соединены с такими номерами входов первой группы входов мат- . ;эицы, кототрые на две единицы меньше одноименных. Вторые и третьи входы; элементов И матрицы соединены соответственно с одним из входов второй группы входов матрицы и с разрешающим входом матрицы. Выходы ; элементов И матрицы, соответствующих одинаковым позициям кодового слова результата, соединены выходными диагональныьш шинами с соответствующими выходами матрицы. Во второй группе входов матрицы 3 коммутация противоположна той, что принята для матрицы 2, Блок 4 коммутации представляет собой группу из р/2 элементов ИЛИ. Количество входов блока 4 коммутации равно р . Входы блока 4, соответст-. вукхдие каждой независящей от переноса и. повторяивдейся позиции в кодовых слоях (представленных в коде,, противоположном коду М из } по уровням напряжений) всех возможных результатов, соединены с входами одного и того же элемента ИЛИ. Выходы элементов ИЛИ являются выходами блока 4 коммутации. Регистры 5 и б представляют собОй группы из триггеров, ксшдый из которых содержит элементы И-НЕ (ИЛИ-НЕ), позволякяцие ему в зависимости от режима работы устройства выполнять функции К -триггера ( в нормальном режиме работы) или Т-триггеров (в ава рийном режиме работы). Матрица 7 сложения представляет собой матрицу многовходовых элементов И, Количество входов элемента И равно 2м. Входы элементов И матрицы 7 сложения соединены с определенным входами блока, согласно выбранному алфавиту. Причем алфавит выбирается таким образом, что кодовые слова, которые соответствуют соседним (в алфавите) цифрг1М имеют различия тол ко в двух позициях (т.е. минимальны различия), а кодовие слова, соответ ствуюище парам цифр, сдвинутых по числовой оси друг относительно друг на величину р/2, имеют различия во всех позициях. Например, следукхций алфавит: 0-OOllj 1 - 0101; 2 - 1001 3 - 1100; 4 - 1010; 5 - оно, где . Шины, объединяющие выходы элементов И, соответствую1«их одинаковым результатам операции, соединены с выходами матрицы 7 сложения. БЛОК 8 управления содержит (фиг.2 первый элемент ИЛИ 20, элемент НЕ 2 три элемента И 22-24, триггер 25 и второй элемент ИЛИ 26. Входы элемента ИЛИ 20 соединены с пятым и шестым входами блока 8. Выход первого элемента ИЛИ 20 соединен с четвертым вы ходом блока 8 и с входом элемента НЕ 21. Выход элемента НЕ 21 соединен с первыми входами элементов И 22-24 Вторые входы элементов И 22-24 соединены с седыллм входом блока 8. Тре тки и четвертый входы элемента И 23 соединены с первым и вторым входами блока 8. Выход элемента И 22 является третьим выходом блока 8. Выходы элементов И 23 и 24 соединены с входами второго элемента ИЛИ 26, выход которого соединен с пятым выходом блока 8. Единичный и нулевой входы триггера 25 соответственно являются девятым и восьмым входами блока 8, а единичный и нулевой выходы триггера 25 - первым и вторым выходами блока 8. Сумматор работает следующим обраПредварительно на первую группу входов регистра 1 результата и на де вятый вход блока 8 управления поступает сигнал из входной шины 10 установки сумматора. Операнды в коде М из N поступают на информационные входы соответствующих регистров S и б операндов. Если на их выходах образуются правильные кодовые слова, срабатывает один из многовходовых элементов И матрицы 7 сложения, и с его выходов сигналы, соответствующие результату операции, поступают на один из входов матрицы 2 коррекции переноса и дополнительной матрицы 3 коррекции переноса, на одну из выходных шин 14 переноса, на один из входов блока 8 управления, на соответствующий вход блока 4 кои мутации. Одновременно с этим на один из входов второй группы входов матриц 2 и 3 поступает сигнал по входной шине 11 переноса сигнала, на седьмой вход блока 8 управления поступает сигнал, соответствукяций появлению сигнала на одном из выходов матрицы сложения в другом (младшем) разряде сумматора или наличию специального сигнала из устройства управления ЭВМ, с первой управляющей шины 16 состояния сумматора, сигнал с первого выхода блока 8 управления поступает на разрешающий вход матрицы 2 коррекции переноса. Зятем срабатывает соответствующий элемент И матрицы 2 коррекции переноса и соответству«яааК элемен.т ИЛИ блока 4 коммутации. С четвертого выхода блока 8 упргшления си,гнал, соответствукяций появлению результата операции, поступает на первый выход 18 управления результатом операции сумматора. Сигналы с выходов блока 2 и 4 поступают на соответствующие входы второй группы входов регистра 1 результата, образуя Ходсзвое слово результата в коде, противоположном (по уровням напряже- , ний) коду М изМ . Последние сигна-) лы воздействуют на соответствующие триггеры регистра 1 результата (на нулевые входы), предварительно установленные в единичное состоян1 е.После этого На выходёк регистра 1 образуется кодовое слово, соответствующее результату операции в коде М из « Появление ошибочных кодовых слов операндов с большим, чем положено, количеством единиц приводит к появлению на выходах матрицы 7 сложения сразу нескольких сигналов, которые затем шифруются матрицей 2 коррекции переноса и блоком 4 коммутации как результаты нескольких прггвяпьнах операций, появившихся одновременно, в коде, противоположном (по уровням напряжений) коду М из N . Вследствие этого, на выходах регистра 1 результата образуется кодовое слово с меньшим, чем положено, количеством единиц, так как большее,чем нужно, количество триггеров (установленных ранее в единичное состояние) будет переведено в нулевое состояние, поэтому ошибка будет обнаружена и не получит дальнейшего распространения. Если поступят правильные кодовые слова операндов, но соответствукиций им элемент И матрицы 7 сложения неисправен (например, обрыв одной или группы связей элемента), отсутствие сигналов на всех выходах этой матрицы приведет к постоянному отсутствию

сигнала на выходе элемента ИЛИ 20 блока 8 управления и, следовательно, к появлению разрешающего сигнала на первых входах элементов И 22-24 в тот момент времени, когда на вторые входы этих элементов поступит через седьмой вход блока 8 сигнал, соответствующий появлению какого-либо- результата в другом-(младшем) разряде сумматора или специальный управляю щий сигнал). А если оба кодовых елова операндов в нулевых позициях имеют одинаковы е символы, (сигналы с первых информационнызг выходов регистров операндов), соответствуквдие сигналы поступят на третий и четвертый входы элементов И 23 или 24 Тогда в результате срабатывания одного из двух последних элементов с пятого выхода блока 8 сигнал поступит на. второй выход 19 управления инверсией сумматора; в результате срабатывания элемента И 22 сигнал с третьего выхода блока 8 поступит в сигнальнуют выходную шину 15 сумматора и на iexoды управления инверсией первого 5 и второго 6 регистров операндов, при этом все триггеры первого 5 и второ-т го б регистров операндов будут переведены в противоположные состояния. Дёшьнейшая- работа сумматора аналогична.

. Бели в данный и в младсаий 1многораэ:рядног6 сумматора поступят правильные кодовые слова операндов, а в младшем разряде им соответствует неисправный элемент И матрицы сложения, .то вследствие отсутствия V сигнала переноса в данный разряд в нем так же, как и в младшем раз- ; ряде,не образуется кодовое слово результата, пока в младшем разряде не произойдет коррекция слов рпераН дов и не сработает другой элемент И матрицы сложения. Если при этом кодовые слова операндов младшего разряда имеют одинаковые символы в нулевых позициях, на втором выходе 19 управления инверсией младшего разряда сумматора появится сигнал, сооттве ствую1дай необходимости инвертирования переноса из младшего разряда. Этот сигнал поступит на восьмой вход блока 8 управления данного разряда сумматора и переведет триггер 25 в противоположное состояние. После

5 этого разрешающий сигнал будет подаваться не на разрешаквдий вход матрицы 2 коррекции.переноса, а на разрешающий вход дополнительной матрицы 3 коррекции переноса, которая имеет

О противоположную коммутацию во второй группе входов блока.

Появление на выходах регистра 1 результата кодового слова с меньшим, чемположено, количеством единиц

S после проведения коррекции кодовых слов операндов в этом же разряде сумматора (началу такой коррекции соот. ветствует сигнал на сигнальной выходной шине 15 сумматора) свидетельQ ствует о том, что хотя бы одно из ко.довых слов операндов содержало до коррекции меньшее, чем положено, количество единиц, „..

5 П р и мер. При необходимости корректировать пару операндов: 0101 i(цифра 1) и 1001 (цифра 2), которой :соответствует кодовое слово резульJ тата 1100 (цифра З) и перенос О в

j старший разряд, получаем следующую пару кодовых слов операндов: 1010 (цифра 4) и ОНО (цифра 5), которой соответствует кодовое слово результата 1100 и перенос в старший раз ряд 1. Поскольку нулевые (крайние

5 справа) позиции кодовых слов операндов (сигналы с первых информационных выходов регистров операндов) содержат одинаковые символы, на вТороМ выходе 19 управления инверсией

0 сумматора появится сигнал, соответствующий необходимости инвертировать перенос.

Положительный эффект изобретения заключается в повышении надежности

5 сумматора за счет того, что при возникновении определенных типов неисправностей в матрице сложения осуществляется коррекция кодовых слов операндов.

vtJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в коде "м из N | 1982 |

|

SU1051533A2 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

СУММАТОР В КОДЕ М ИЗ М ПО авт.св. 873238, отличающийс я тем, что, с-целью повышения его надежности за счёт коррекции кодовых слов операндов, он содержит дополнительную матрицу коррекции переноса, первый и второй регистры операндов и блок управления, причем выходы дополнительной матрицы коррекции переноса соответственно соединены с второй группой входов регистра результата, первая и вторая группы входов дополнительной матрицы коррекции переноса соединены соответственно с второй группой выходов матрицы сложения и с входными шинами переноса сумматора, информационные входы первого и второго регистров операндов соединены соответственно с входными шинами первого и второго регистров операндов сумматора, информационные входы первого и второго регистров операндов соединены с входами матрицы сложения, первые информационные выходы первого и второго регистров операндов соединены с первым и вторым входами блока управления, выходы состояний первого и второго регистров операндов соединены с третьим и четвертым входами блока управления, первая группа выходов матрица сложения соединена с пятым и шестым входами блока управления, седьмой, восьмой и девятый входы блока управ..J ления соединены соответственно с первой управляющей шиной состояния, с второй управляющей шиной установки и с входной шиной установки сумматора, первый и второй выходы блока управления соединены с разрешающими входами соответственно матрицы коррекции переноса и дополнительной матрицы коррекции переноса, третий выход блока управления соединен с входами управления инверсией первого и второго регистров операндов и с сигнальной выходной шиной сумматора, четвертый и пятый выходы блока управления соединены соответственно с первым выходом управления результа§ том операции и вторым выходом управления инверсией сумматора, причем блок управления содержит элементы ИЛИ, элемент НЕ, три элемента И и триггер, входы первого элемента ИЛИ соединены с пятым и шестым §. входами блока, выход первого элемента ИЛИ соединен с четвертым выходом блока и с входом элемента НЕ, выход элемента НЕ соединен с первыми входами всех элементов И, вторые входа -всех элементов И соединены с сл седьмым входом блока, третий и четМ вертый входы второго элемента И соединены с первым и вторым входами блока, третий и четвертый входы третьего элемента И соединены с третьим и четвертым входами блока, выоо ход первого элемента И является третьим выходом блока,, выходы второго и третьего элементов И соединены с входами второго элемента ИЛИ, выходкоторого соединен с пятым выходом блока, единичный и нулевой входы триггера являются соответственно девятым и вось№Ш входами блока, единичный и нулевой выходы триггера являются срответственно первым и вторым выходами блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения чисел | 1979 |

|

SU873236A1 |

Авторы

Даты

1983-11-07—Публикация

1982-06-25—Подача