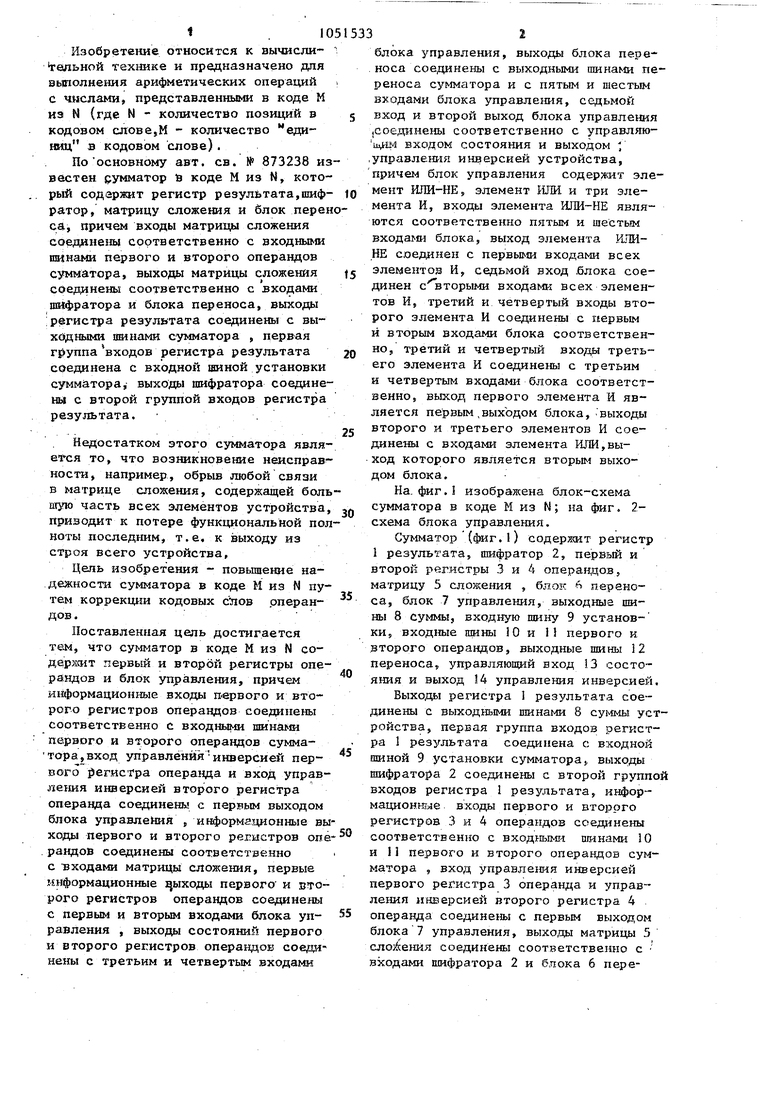

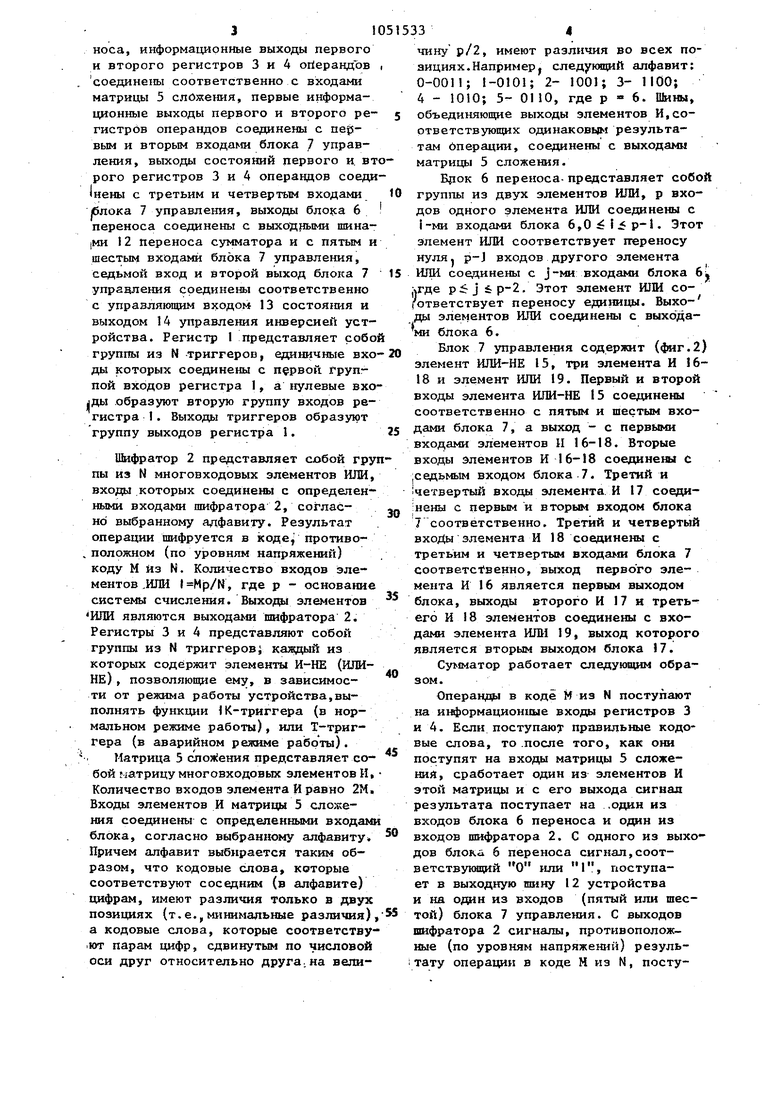

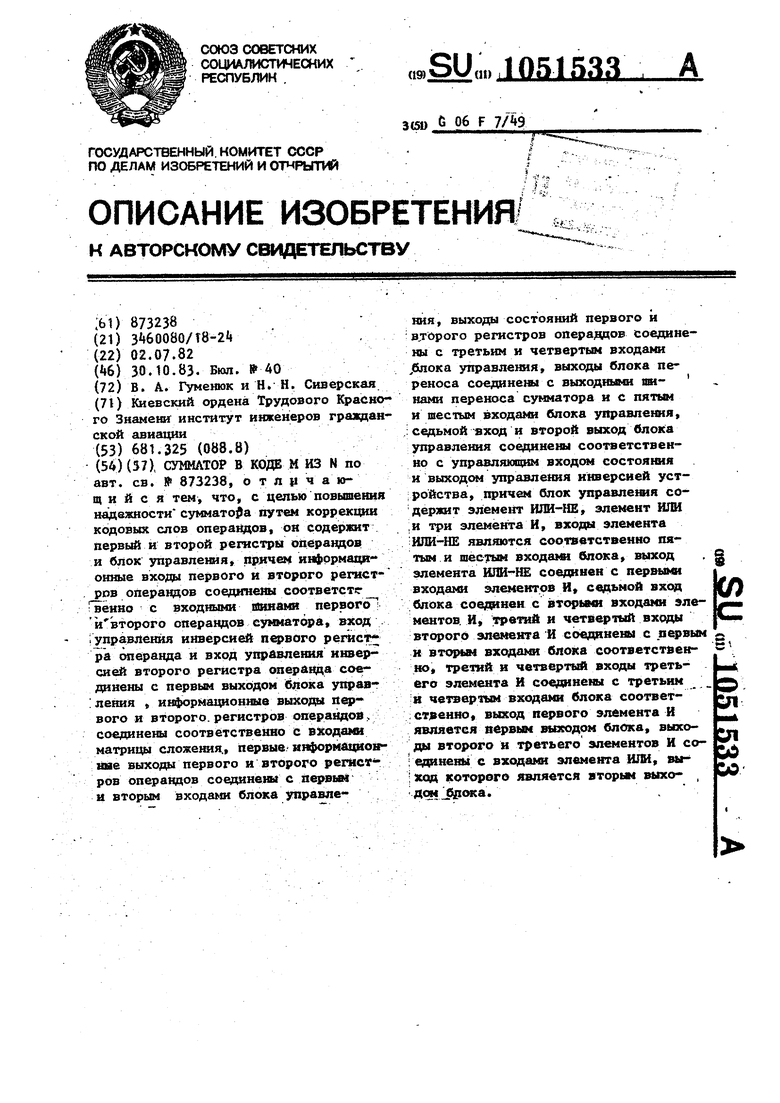

1 . 10 Изобретение относится к вычислительной технике и предназначено для выполнения арифметических операций с чнслами, представленными в коде М из N (где N - количество позиций в кодовом слове,М - количество единиц э кодовом слове). Поосновному авт. св. № 873238 из вестен румматор 18 коде М из N, который содержит регистр результата,шифратор, матрицу сложения и блок перен са, причем входы матрицы сложения соединены соответственно с входными шинами первого и второго операндов сумматора, выходы матрицы соложения соединены соответственно с входами Шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора , группа входов регистра результата соединена с входной шиной установки сумматора, выхода шифратора соединены с второй группой входов регистра результата. . Недостатком этого сумматора является то, что возникновение ненсправ ности, например, обрьш любой связи в матрице сложения, содержащей боль тую часть всех элементов устройства приводит к потере функциональной пол ноты последним, т.е. к выходу из строя всего устройства. Цель изобретения - повышение надежности сумматора в коде М из N путем коррекции кодовых ёпов операндов. Поставленная цепь достигается тем, что сумматор в коде М из N содерхсит первый и второй регистры операндов и блок управления, причем информационные входы п-ервого и второго регистров операндов соеда1нены соответственно с входныьш шинами первого и второго операндов сумматора,вход управленияинверсией первого егистра операнда и вход управлегшя инверсией второго регистра операнда соединены с первым выходом блока управления , и ормазц1онные вы ходы первого и второго регистров опе . рандов соединены соответственно с входами матрицы сложения, первые информационные ыходы первого и STOрого регистров операндов соединены с первым и вторым входами блока управления , выходы состояний первого и второго регистров операндов соединены с третьим и четвертым входами 2 блока управления, выходы блока переноса соединены с выходными шинами переноса сумматора и с пятым и шестым входами блока управления, седьмой вход и второй выход блока управления .соединены соответственно с управляюш т входом состояния и выходом , управле1шя инверсией устройства, причем блок управления содержит элемент ИЛИ-НЕ, элемент ИЛИ и три элемента И, входы элемента являются соответственно пятым и шестым вxoдa Jи блока, выход элемента ИЛИНЕ соединен с первыми входами всех элементов И, седьмой вход .блока соединен с вторыми входами всех элементов И, третий и четвертый входы второго элемента И соединеш) с первым и вторым входами блока соответственно, третий и четвертый входы третьего элемента И соединены с третьим и четвертым входами блока соответственно j выход первого элемента И является первым ,выходом блока,-выходы второго и третьего элементов И соединею) с входами элемента ИЛИ,выход которого является вторым выходом блока. На. фиг.I изображена блок-схема сумматора в коде М из N; на фиг. 2схема блока управления. Сумматор (фиг.О содержит регистр 1 результата, шифратор 2, первый и второй регистры 3 и 4 операндов, матрицу 5 сложения , блок А переноса, блок 7 управления, выходные шины 8 суммы, входную шину 9 установки, входные яшны 10 и П первого к второго операндов, выходные шины 12 переноса, управляющий вход 13 состояния и выход 14 управления инверсией. Выходы регистра 1 результата соединены с выходными шинами 8 устройства, первая группа входов регистра 1 результата соединена с входной шиной 9 установки сумматораj выходы шифратора 2 соединены с второй группой входов регистра 1 результата, информационшле входы первого и второго регистров 3 и 4 операндов соединены соответственно с входными шинами 10 и 11 первого и второго операндов сумматора 5 вход управления инверсией первого регистра 3 операнда и управления инверсией второго регистра 4 операнда соединены с первым выходом блока 7 управления, выходы матрицы 5 соединены соответственно с входами шифратора 2 и блока 6 переноса, информационные выходы первого и второго регистров 3 и 4 ойерандов соединены соответственно с входами матрицы 5 сложения, первые информационные выходы первого и второго регистров операндов соединены с первым и вторым входами блока 7 управления, выходы состояний первого и. вт рого регистров 3 и 4 операндов соеди «нены с третьим и четвертым входами (блока 7 управления, выходы блока 6 переноса соединены с выходными шина|МИ 12 переноса сумматора и с пятым и шестым входами блока 7 управления, седьмой вход и второй выход блока 7 управления соединены соответственно с управляющим входом 13 состояния и выходом 14 управления инверсией устройства. Регистр I представляет собо группы из N триггеров, единичные вхо ды которых соединены с первой Группой входов регистра 1, а Нулевые вхо лды образуют вторую группу входов регистра 1. Выходы триггеров образуют группу выходов регистра 1, Шфратор 2 представляет собой гру пы из N многовходовых элементов ИЛИ, входы которых соединены с определенными входами шифратора 2, согласно выбранному алфавиту. Результат операции шифруется в коде противо. положном (по уровням напряжений) коду М из N. Количество входов элементов .ИЛИ , где р - основание системы счисления. Выхода элементов ИЛИ являются выхода ш шифратора 2. Регистры 3 и 4 представляют собой группы из N триггеров; каждый из которых содержит элементы И-НЕ (ИЛИНЕ), позволяющие ему, в зависимости от режима работы устройства,выполнять функции Ж-триггера (в нормальном режиме работы), или Т-триггера (в аварийном режиме работы). Матрица 5 сложения представляет собой матрицу многовходовых элементов И, Количество входов элемента И равно 2М. Входы элементов И матрицы 5 сложения соединены с определенными входами блока, согласно выбранному алфавиту Причем алфавит выбирается таким образом, что кодовые слова, которые соответствуют соседним (в алфавите) цифрам, имеют различия только в двух позициях (т.е.,минимальные различия) а кодовые слова, которые соответствуЮТ парам цифр, сдвинутым по числовой оси друг относительно друга на величину р/2, имеют различия во всех позициях. Например следукяций алфавит: 0-0011; 1-0101; 2- 1001; 3- 1100; 4 - 1010; 5- ОНО, где р - 6. Шины, объединяющие выходы элементов И,соответствующих одинаковь)м результатам Операции, соединены с выходами матрицы 5 сложения. Брок 6 переноса- представляет собой группы из двух элементов ИЛИ, р входов одного элемента ИЛИ соединены с i-ми входами блока 6,. Этот элемент ИЛИ соответствует переносу нуля. P-J входов другого элемента ИЛИ соединены с j-ми входами блока 6j, лгде &р-2. Этот элемент ИЛИ со/ответствует переносу еди1шш 1. Выходы элементов ИЛИ coe щнeны с выходами блока 6. Блок 7 управления содержит (4мг.2) элемент ИЛИ-НЕ 15, три элемента И 1618 и элемент ИЛИ 19. Первый и второй входы элемента ИЛИ-НЕ 15 соединены соответственно с пятым и шестым входами блока 7, а выход - с первыми входами элементов И 16-18. Вторые входы элементов И 16-18 соединены с ;седьмым входом блока 7. Третий и четвертый входы элемента И 17 соеди:нены с первым и вторым входом блока 7 соответственно. Третий и четвертый входы элемента И 18 соединены с третьим и четвертым входами блока 7 соответственно, выход первого элемента И 16 является первым выходом блока, выходы второго И 17 и третьего И 18 элементов соединены с входами элемента ИЛИ 19, выход которого является вторым выходом блока 17. Сумматор работает следующим образом. Операнды в коде М из N поступают на информационные входы регистров 3 и 4. Если поступаю правильные кодовые слова, то .после того, как они поступят на входы матрицы 5 сложений, сработает один из элементов И этой матрицы и с его выхода сигнал результата поступает на .один из входов блока 6 переноса и ода{Н из входов 01ифратора 2. С одного из выходов блока 6 переноса сигнал,соответствуниций О нли 1, поступает в выходную шину 12 устройства и на ода1н из входов (пятый или шестой) блока 7 управления. С выходов шифратора 2 сигналы, противополож№ле (по уровням напряжений) результату операции в коде Низ N, поступят на нулевые входы триггеров регистра 1 результата, предваритель. но установленные в единичные состояния, Управлянщкй сигнал (например, сигнал, соответствующий появ леник результата операиьии в младшем разряде многоразрядного сумматора, или сигнал из устройства управления, если сумматор одноразряд МйЙ)э который поступает на управляющий вход 13 состояния устройства (седьмой вход блока 7), не приводит к появленш) сигналов на выходах блока 7, поскольку на первых входах элементов И 16-18 в этот момент отсутствует разрешающий сигнал.На выходах регистре результата образуется кодовое inioBO соответствующее результату операции в коде М из N. Появление ошибочных кодовых слов операндов с большим , чемположено, |КОйичёством еданшц, приводит к пояЁвяению на выходах элементов И матри цы 5 сложе1шя лразу нескольких сиг налов , которые шифруются в коде, ЬбратнОм (по уровням напрякений) коду М из {4 шифратором 2, как резуль татад нескольких правильных операций появившихся одновременно. Вследствие этого на выходах шифратора 2 появляется кодовое слово с б {яьшим., чем положено, количеством единиц. Сигналы, соответствующие единицам это го кодового слова, поступают на нулеаые входы соответствующих триггеров (предварительно установленш.1х в еди1шчное состояние) регистра 1 результата. На выходах этого регистра образуется кодовое слово с мень шим, чем положено, количеством единиц , поэтому ошибка будет обнаруже на и не получит дальнейшего распрос ранения . . - Если поступят правилышё Кодовые Слова операвдов, но соответствующгф им элемент И матрицы 5 сложе кия неисправен (например, обрыв одной, или группы связей элемента), .отсутст&иа.сигналов на всех выходах этой матрицы приведем к появлению разрешающего сигнала на первых входах элементов И 16-18. С первого йьисода блока 7 на входах управления инверсией блоков 3 и 4при наличии управлякяцего сигнала на управ , ляияцем входе состояния блока 7 по явится сигнал, под воздействие которогю все триггеры блоков 3 и 4 переходят в противоположные состояния. Если триггеры, соответств тащие нулевым позициям кодовых слов первого и второго операндов, нахо- дятся в одинаковых состояниях (поступают сигналы с выходов..состояний блоков 3 и 4), то сигналS соответствующий необходимости инвертировать перенос, появится на выходе 14 управления инверсией устройства {со второго выха,ца блока 7), Дальнейшая работа устройства аналогична рассмотренной ;.анее. . Следует отметить что появление на выходах регистра 1 результата кодового слова с меньшим5 чем положено, количеством единиц, после проведения коррекции кодовых слов операндов (сигнал, поступающий на входы управления инверсией регистров 3 и 4, может быть выв еден также в спе циальную выходную шину устройства :при необходимости), свидетельствует о том, что хотя бы одно из кодовых слов операндов содержало до коррекции меньшее,, чем положено, количество единиц. Следовательно, нужно повторить запись кодовых слов операндов в регистры 3 и Л из соответствующик блоков Сблока) ЭВМ, П р и.М е р . При необходимости корректировать пару операндов ООП (цифра 0) и 1001 (цифра 2), которой соответствует кодовое слово результата 1001 иLnepeHoc О, получаем следующую пару операндов : 1100 (цифра 3) и 0110 (цифра 5), которой соответствует кодовое слово ре зультата 1001 и перенос 1. Посколь ку нулевые позиции кодовых слов первого и второго операндов (сигналы с. первых информационных выходов .регистров операндов) содержат одинаковые символы (в любом случае),на выходе управления инверсией сумматора появится сигнал, соо гветствуюш;ий необ ходамости инвертировать перенос. Положител 5ный эффект от внедредаш предлагаемого сумматора заключается в повышении его надежности по сравнению с прототипом за счет TOrOj, что при возникновении опррдеяеншйг типов неисправностей в матрице сложения осуществляется коррекция кодовых слов операндов су|- матора.

/о|:

//

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| Сумматор в коде "М из @ | 1982 |

|

SU1053103A2 |

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

| Двоично-десятичное арифметическое устройство | 1976 |

|

SU731436A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

. СУММАТОР В КОДЕ М ИЗ N по авт. ев, 873238, о т я ii ч а ющ и и с я тем, что, с цепью повышения надежности сумматора путем коррекции кодовых слов операндов, он соде:ржит первь и второй регистры операвдов и блок управления, прячем информационные входы первого и второго регист.ров операвдов соединены соответстг Гвённо с входными оишамя первогсП ивторого операндов сумматора, вход . Гуправления инверсией левого регаст ра операнда и вход управления инверсией второго регистра операнда соединены с первым выходом блока упрааг : лении , информационные выхода леу вого и второго, регистров операндов соединены соответственно с входами матрицы сложения., первые информационшяе выходы первого и второго регистров операндов соединены с первьм ц вторым входаьш блока управления, выходы состояний первого и в торого регистров операддов соединеiQd с третьим и четвертым входами jблoкa управления, выходы блока пе реноса соединены с выходшлми вннами переноса сумматора и с пятым и шестым входами блока управления, :седьмой вход и второй выход блока управления соединены соответственно с управляющим входом состояшя и выходом управления инверсией уст:ройства, причем блок управления содержит элеме11т ИЛИ-НБ, элемент ИШ ;и три элемента И, входы элемента ИЛИ-НЕ являются соответственно пятым и шестым входами блока, выход элемента ШШ-Н соединен с первыми (О входами элементов И, ссуцьмой вход блока соединен с вторыми входами элес ментов. И, третий и четйертый входы второго элемента И соединены с первым § и втсфьм входа в1 блока соответственно, третий и 4eTBepTtdA входы третьего элемента И соединены с третьим Р:Н входами блока соответUI :ственно, выход первого элемента И является вервым выходом блока, выхо:jn да второго и третьего 9л ентов И со: :с i едане1Ш с входами элемента ШМ, выг |ход которого является вторым выхо- , (жа..

Т I

/э /«

Фиа.4

Фиг.2.

Авторы

Даты

1983-10-30—Публикация

1982-07-02—Подача