(54) СУММАТОР В КОДЕ М ИЗ N

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Сумматор в коде "М из @ | 1982 |

|

SU1053103A2 |

| Сумматор в коде "М из N | 1981 |

|

SU985781A1 |

| Сумматор в коде "м из N | 1982 |

|

SU1051533A2 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

1

Изобретение относится к вычислительной технике и предназначено для суммирования чисел, представленных в коде М изН .

Известен двух разрядный сумматор в коде М из N , младший разряд которого содержит блок вьщачи результата, шифратор, матрицу элементов И, блок, переноса и блок контроля, старший разряд содержит.два блока вьщач,и результата, два шифратора, матрицу элементов И, блок переноса и блок контроля, причем выходы матрицы младшего разряда соединены с входами блока переноса и шифратбра младшего . разряда, выходы матрицы cTajSiiero разряда соединены с входами блока пер1вноса и Обоих шифраторов старшего разряда, выходы шифрат ора и блока контроля младшего разрада соединены с входами блока 20 выдачи младшего разряда, выходы блока Tieреноса младшего разряда иобоих шифраторов старшего разряда соединены с входами соответствугоших блоков выдачи

.старшего разряда, выходы блока контроля старшего разр$ща соединены с входами блоков вьщачи старшего разржща,. выходы блоков выдачи младшего и старшего разрядов и блока переноса старшего разряда соединены с соответствуюшими шинами устройства 1 .

Недостатками этого устройства являются сравнительно невысокое быстродействие из-за необходимости прохождения сигналов, соответствующих результату выполненной операции, через блоки выдачи результата, и большие аппаратурные затраты на реализацию блоков контроля и вьщачи результата.

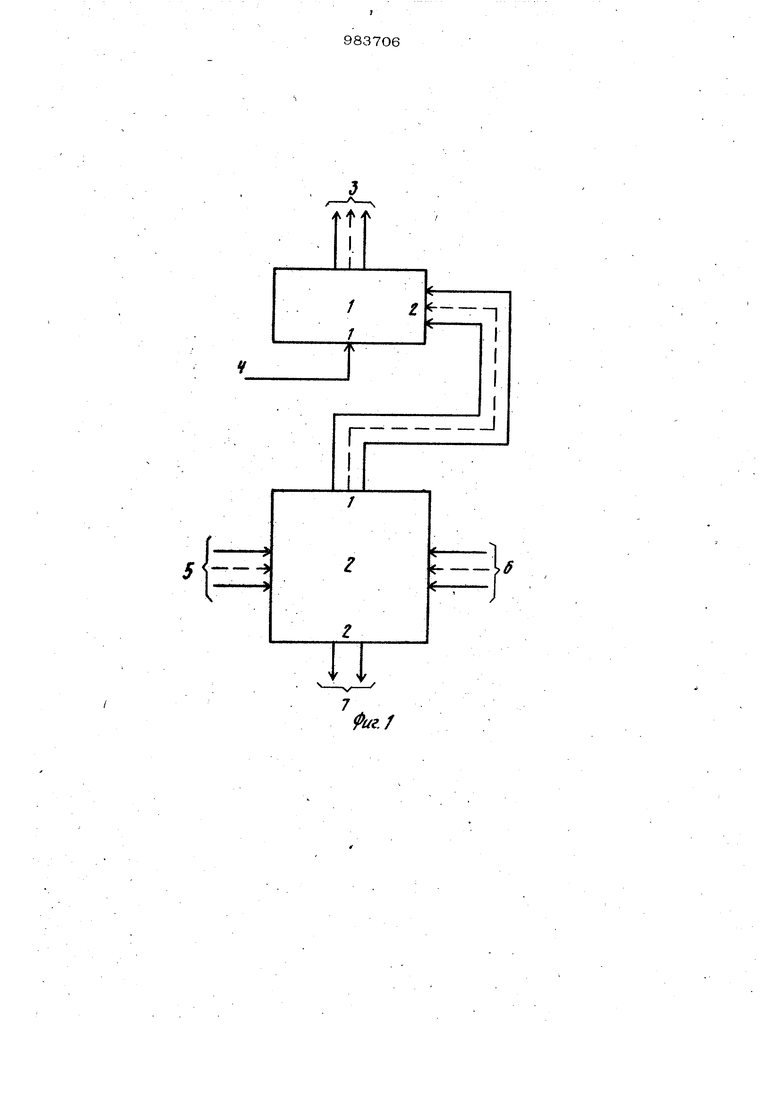

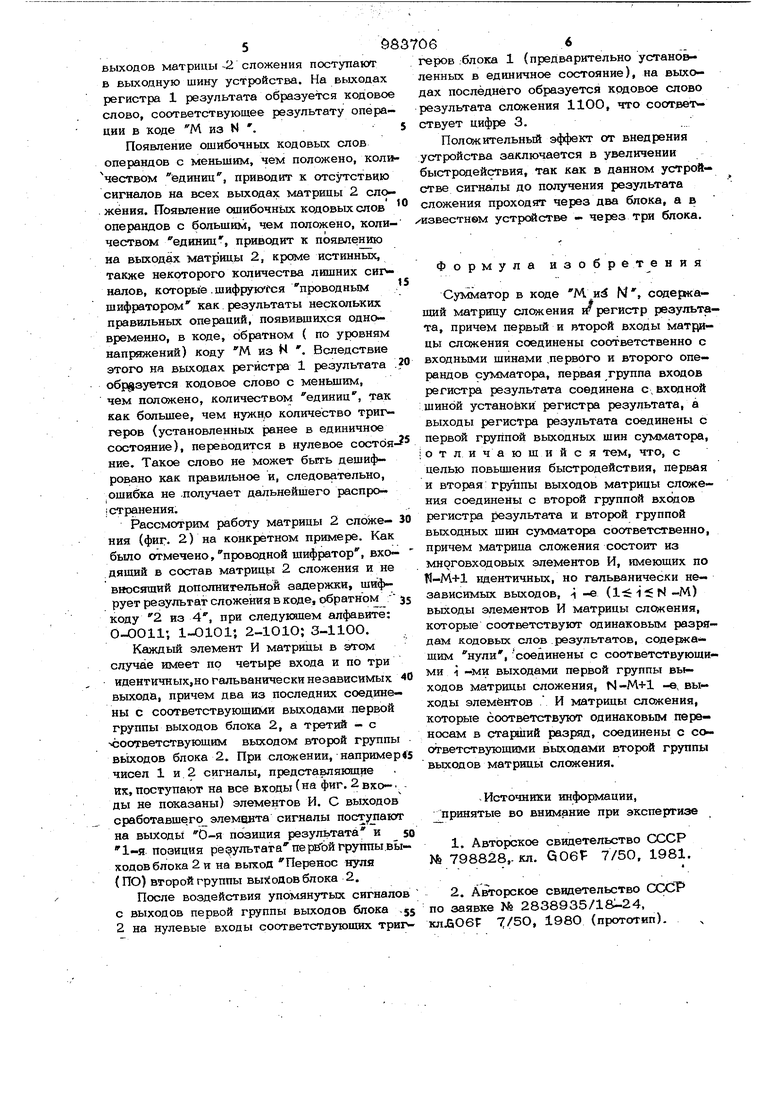

Наиболее близким к изобретению является сумматор в коде М , кото рый содеркит регистр результата, шифратор, матрицу сложения и блок переноса, причем входы матрицы сложения соединены соответственно с входами шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена с входной шиной установки сумматора, выходы шифратора соединены с второй группой входов регистра результата 2 . Недостатком этого устройства является сравнительно невысокое быстродействие вследствие необходимости прохождения входных сигналов до формирования результата на выходах устройства последовательно через три блока: матрицу ело,,жения, шифратор и регистр результата. ; Цель изобретения - повьшение быстродействия сумматора в коде М из N . Поставленная цель достигается тем, что в сумматоре в коде М из N , содержащем матрицу сложения и регистр .результата, причем первый и второй входы матрицы сложения соединены соответствен но с входными шинами перврго и второго операндов сумматора, первая группа входов регистра результата соединена с вход ной шиной установки регистра результата ,а выходы регистра результата соединены с первой группой выходньтх шин сумматора, . первая и вторая группы выходов матрицы / сложения соединены с второй группой входов регистра результата и второй груп пой выходных шин сумматора соответст- Беннр, причем матрица сложения состоит из многовходовых элементов И, имеюшйх по М-М+1 идентичных, но гальванически независимых выходов, i -е (l$-isN-M) выходы элементов И матрицы сложения, которые соответствуют одинаковым разрядам кодовых слов результатов, содержашим нули, соединены с соответствующи: ми ii-ми выходами первой группы выходо матрицы сложения, W-М+1 -е выходы элементов И матрицы сложения, которые соответствуют одинаковым переносам в старший разряд, соединены с соответствующими, выходами второй группы выходов матрицы сложения. На фиг. 1 представлена блок-схема сумматора в коде М из ,М ; на фиг. 2матрица сложения при использовании кода 2 из, 4, основании системы счисления рР4 си следующем алфавите: 0-4DO11, 1-0101; 2-1010; 3-11ОО, где О-я по; зиция кодового слова - крайняя справа. Устройство содержит регистр 1 резул тата, матрицу 2 слйжения. Группа выходов блока 1 соединена с первой группой выходных .шин 3 устройст f&, первый вход блока 1 соединен с вход ной шиной 4 установки регистра результата, первая группа выхадов блока 2 сое динена с второй группой входов блока 1, первая и вторая группы входов блока 2 соединены с группами входных шин 5 и 6 устройства, вторая группа выходов блока 2 соединена с выходными шинами 7 устройства. . Блок 1 устройства представляет собой регистр из N триггеров, единичные входы которьк образуют первую группу входов блока, а нулевые - вторую группу входов блока. Единичные выходы триггеров образуют группу выходов блока. Блок 2 устройства представляет собой матрйпу мнЬговходовых элементов И. Количество входов элемента И равно 2М. Входы элементов И матрицы 2 соединены с определенными шинами кодов операндов, согласно выбранному алфавиту. Шины кодов операндов соединены с входами матрицы 2. Каждый элемент И имеет по Ы-М+1 идентичных, но гальванически независимых: выходов. Такой элемент может представлять, например, группу из N-М+ +1 многоэмиттерных транзисторов по 2М эмиттеров в йаждом. -е выходы элементов И матрицы 2 (1 $ -f $ Ы -М), которые соответствуют одинаковым позициям кодовых слов результатов, содержащим единицы, соединены шинами с соответствующими i -ми выходами первой группы выходов матрицы 2, образуя при этом так называемый проводной шифратор в коде, обратном коду М из N , N-M+1 -е выходы элементов И матрицы сложения, которые со ответствуют одинаковым переносам в старший разряд, соединены с соответствующими выходами (ПО,П1) второй группы выходов матрицы сложения. Устройство работает следующим обра-, зом. Операнды в коде М из N поступаюо- . на входы матрицы 2 сложения. Если поступают правильные слова, срабатцвает один из элементов И и с его выходов сигналы, соответствующие результату операции, поступают на N-M выходов первой группы выходов таким оЬ разом, что на них образуется кодовое слово результата в коде, обратном коду М из N , и на соответствующий выход переноса второй группы выходов. С выходив первой группы выходов матриц 2 сложения сигналы поступают на соответствующие входы второй группы входов регистра 1 результата, на нулевые входы триггеров, предварительно установленных в единичное состояние. Сигналы с выходов второй группы 5$63 выходов матрицы-2 сложения поступают в выходную шину устройства. На выходах регистра 1 результата образуется кодовое слово, соответствующее результату операции в коде М из N ..5 Появление ошибочных кодовых слов операндов с меньшим, чем положено, коли чеством единиц, приводит к отсутствию сигналов на всех выходах матрицы 2 сложения. Появление ошибочных кодовых слов операвдов с большим, чем положено, количеством единиц , приводит к появлению на выходах матрицы 2, кроме истинных, также некоторого количества лишних сипналов, которые .шифруюгся проводным шифратором как результаты нескольких правильных операций, появившихся одновременно, в коде, обратном ( по уровням напряжений) коду М из N . Вследствие этого на выходах регистра 1 результата .0 образуется кодовое слово с меньшим, чем положено, количеством единиц, так как большее, чем нужно количество триггеров (установленных ранее в единичное состояние), переводится в нулевое состояJ кие. Такое слово не может быть дешифровано как правильное и, следовательно, ошибка не .получает дальнейшего распро странения. Рассмотрим работу матрицы 2 сложе- 30 ния (фиг. 2) на конкретном примере. Как бьшо отмечено, проводной шифратор, входящий в состав матрицы 2 сложения и не вносящий дополнйгельной задержки, шифруетрезультатсложениявкоде, обратном -35 коду 2 из 4, при следукшем алфавите: 0-0011, 1-0101; 2-1О1О; 3-1100. Каждый элемент И матрицы в этом случае имеет по четыре входа и по три идентичных,но гальванически независимых 40 выхода. причем два из последних соединены с соответствующими выходами первой группы выходов блока 2, а третий - с соответствуюшим выходом второй группы . выходов блока 2. При сложении, например45 чисел 1 и.2 сигналы, представляющие , их, поступают на все входы (на фиг. 2 вхо- v ды не показаны) элементов И. С выходов сработавшего элемента сигналы постзшают на выходы Ь-я позиция результата и so l-H позиция результата нервойгруппы.выходов блока 2 и на выход Перенос нуля (ПО) второй группы ВЫ540ДОВ блока 2. После воздействия упомянутых сигналов с выходов первой группы выходов блока ,55 2 на нулевые входы соответствующих триг 066геров .блока 1 (предварительно устаноаленных в единичное состояние), на выходах последнего образуется кодовое слово результата слежения 1100, что соответствует цифре 3. Положительный эффект от внедрения устройства заключается в увеличении быстродействия, так как в данном устройстве сигналы до получения результата сложения проходят через два блока, а в известнем устройстве - через три блока, , Формула изобретения Сумматор в коде М, я М , соде|рисащий матрицу сложения {/регистр результата, причем первый и второй входы матрицы сложения соединены соответственно с входными шинами .первого и второго операндов сумматора, первая группа входов регистра результата соединена с,входной шиной установки регистра результата, а выходы регистра результата соединены с группой выходных шин сумматора, отличающийся тем, что, с . повьш1ения быстродействия, первая вторая группы выходов матрицы сложе соединены с второй группой входов регистра результата и второй группой выходных шин сумматора соответственно, причем матрица сложения состоит из многовходовых элементов И, имеющих по W-M+1 вдентичных, но гальванически независимых выходов, -е () выходы элементов И матрицы сложения, которые соответствуют одинаковым разря кодовых слов .результатов, содеги а« им нули, соединены с соответствуюши выходами первой группы матрицы сложения, N-M+l -е, элементов И матрицы сложения, которые соответствуют одинаковым первносам в станций разряд, соединены с соответствуташими выходами второй группы вькодов матрицы сложения, -Источники информации, принятые во внимание при экспертизе 1.Авторское сввдетельство СССР № 798828,- кл. Q06P 7/50, 1981. 2.Авторское свидетельство CGCP о заявке М 2838935/18 24, кл.бО6Р 7,/5О, 198О (прототип).

И

fe/

Авторы

Даты

1982-12-23—Публикация

1981-07-17—Подача