(54) СУММАТОР В КОДЕ fA ИЗ «

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Сумматор в коде "М из @ | 1982 |

|

SU1053103A2 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| Сумматор в коде "м из N | 1982 |

|

SU1051533A2 |

| Сумматор в коде "М из N | 1981 |

|

SU985781A1 |

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

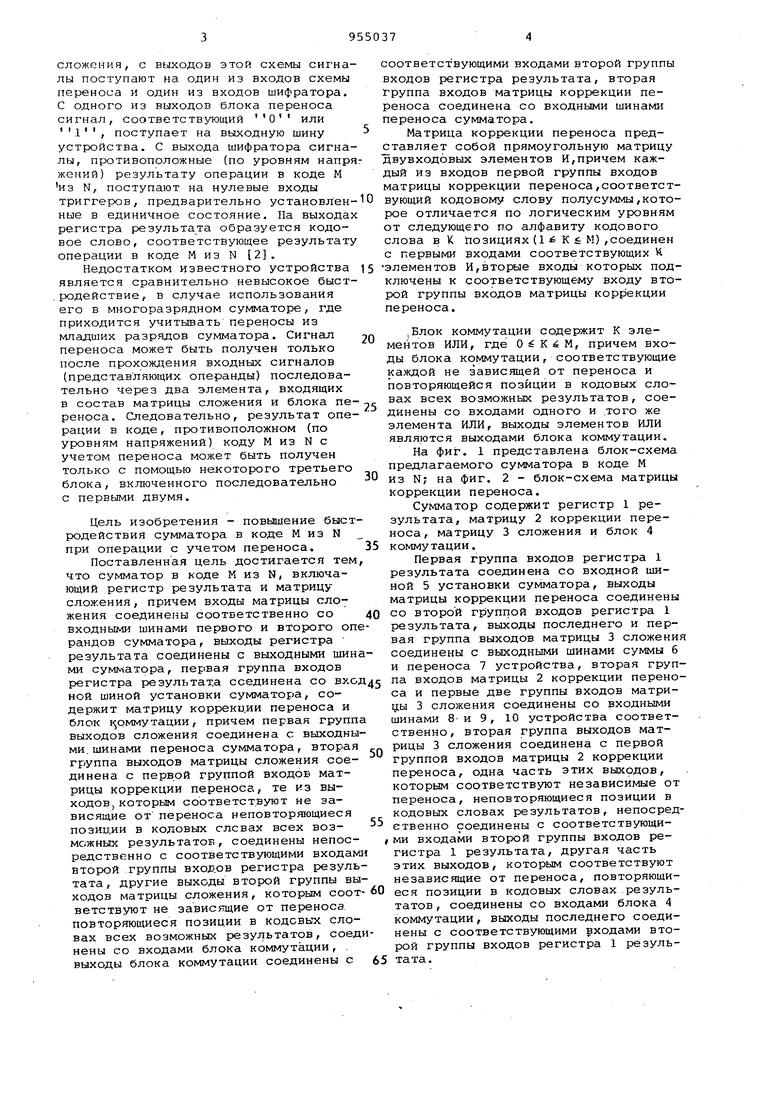

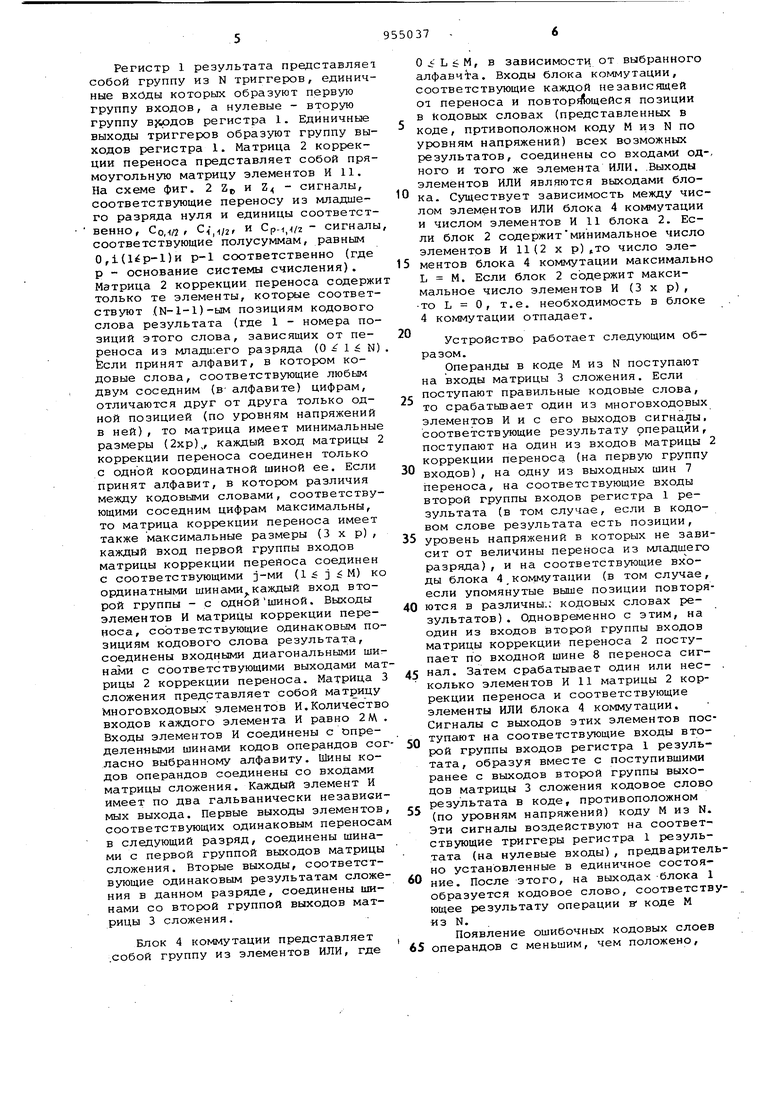

Изобретение относится к вычислительной технике и предназначено для суммирования чисел, представленных в коде М из N (где N - количество позиций в кодовом слове; М - количество единиц в кодовом слове). Известен двуразрядный сумматор в коде М из N, младший разряд которого содержит схему выдачи результата, шифратор, матрицу элементов И, схему переноса и схему контроля, старший разряд содержит две схемы выдачи результата, два шифратора, матрицу элементов И, схему переноса и схему контроля, причем выходы матрицы млад шего разряда соединены со входами схемы переноса и шифратора младшего разряда, выходы матрицы старшего ра ряда соединены со входами схемы переноса и обоих шифраторовстаршего разряда, выходы шифратора и схемы контроля младшего разряда соединены со входами схемы выдачи младшего ра ряда, выходы схемы переноса младшего разряда и обоих шифраторов старшего разряда соединены со входами со ответствующих схем выдачи старшего разряда, выходы схемы контроля стар|Шего разряда соединены со входами схем выдачи старшего разряда,, выходы dxeM выдачи младшего и старшего разрядов и схемы переноса старшего разряда соединены с соответствующими шинами устройства 1. Недостатки данного устройства сравнительно невысокое быстродействие из-за необходимости прохождения сигналов, соответствующих результату выполненной операции, через схемы выдачи результата и большие аппаратурные затраты на реализацию схем контроля и схем выдачи результата , Наиболее близок к предлагаемому по технической сущности сумматор в коде М из N, который содержит регистр результата, шифратор, матрицу сложения и блок переноса, причем входы матрицы сложения соединены соответственно со входными шинами первого и второго сумматора, выходы матрицы сложения соединены соответственно со входами шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со входной шиной установки сумматора, выходы шифратора соединены со второй группой входов регистра результата. Операнды в коде М из N поступают на входы матрицы сложения, с выходов этой схемы сигналы поступают на один из входов схемы переноса и один из входов шифратора, С одного из выходов блока переноса сигнал, соответствующий О или , поступает на выходную шину устройства. С выхода шифратора сигналы, противоположные (по уровням напря жений) результату операции в коде М из N, поступают на нулевые входы триггеров, предварительно установленные в единичное состояние. Па выходах регистра результата образуется кодовое слово, соответствующее результату операции в коде М из N 2. Недостатком известного устройства является сравнительно невысокое быст.родействие, в случае использования его в многоразрядном сумматоре, где приходится учитьшать переносы из младших разрядов сумматора. Сигнал переноса может быть получен только после прохождения входных сигналов (представляющих операнды) последовательно через два элемента, входящих в состав матрицы сложения и блока переноса. Следовательно, результат oneрации в коде, противоположном (по уровням напряжений) коду М из N с учетом переноса может быть получен только с помощью некоторого третьего блока, включенного последовательно с первыми двумя. Цель изобретения - повышение быстродействия сумматора в код-е М из N при операции с учетом переноса. Поставленная цель достигается тем что сумматор в коде М из N, включающий регистр результата и матрицу сложения, причем входы матрицы сложения соединены соответственно со входными шинами первого и второго опе рандов сумматора, выходы регистра результата соединены с выходными шина ми сумматора, первая группа входов регистра результата ссединена со вход ной шиной установки сумматора, содержит матрицу коррекции переноса и блок 1 рммутации, причем первая групп выходов сложения соединена с выходными, шинами переноса сумматора, вторая группа выходов матрицы сложения соединена с первой группой входов матрицы коррекции переноса, те из выходов, которым соответствуют не зависящие от переноса неповторяющиеся позиции в кодовых слсвах всех возможных результатов, соединены непосредственно с соответствующими входам второй группы входов регистра резуль тата, другие выходы второй группы вы ходов матрицы сложения, которым соот ветствуют не зависящие от переноса повторяющиеся позиции в кодовых еловах всех возможных результатов, соед нены со входами блока коммутации, . выходы блока коммутации соединены с оответствующими входами второй группы входов регистра результата, вторая Группа входов матрицы коррекции переноса соединена со входными шинами переноса сумматора. Матрица коррекции переноса предтавляет собой прямоугольную матрицу двувходовых элементов И,причем каждый из входов первой группы входов матрицы коррекции переноса,соответствующий кодовому слову полу суммы, ко торое отличается по логическим уровням от следующего по алфавиту кодового слова в К позициях(1 К М) ,соединен с первыми входами соответствующих К элементов И,вторые входы которых подключены к соответствующему входу второй группы входов матрицы коррекции переноса. |Блок коммутации содержит К элементов ИЛИ, где О i К ii М, причем входы блока коммутации, соответствующие каждой не зависящей от переноса и повторяющейся позиции в кодовых словах всех возможных результатов, соединены со входами одного и .того же элемента ИЛИ, выходы элементов ИЛИ являются выходами блока коммутации. На фиг. 1 представлена блок-схема предлагаемого сумматора в коде М из N; на фиг. 2 - блок-схема матрицы коррекции переноса. Сумматор содержит регистр 1 результата, матрицу 2 коррекции переноса, матрицу 3 сложения и блок 4 коммутации. Первая группа входов регистра 1 результата соединена со входной шиной 5 установки сумматора, выходы матрицы коррекции переноса соединены со второй группой входов регистра 1 результата, выходы последнего и первая группа выходов матрицы 3 сложения соединены с выходными шинами суммы б и переноса 7 устройства, вторая группа входов матрицы 2 коррекции переноса и первые две группы входов матрицы 3 сложения соединены со входными шинами 8- и 9, 10 устройства соответственно, вторая группа выходов матрицы 3 сложения соединена с первой группой входов матрицы 2 коррекции переноса, одна часть этих выходов, KOTopfcJM соответствуют независимые от переноса, неповторяющиеся позиции в кодовых словах результатов, непосредственно соединены с соответствующими входами второй группы входов регистра 1 результата, другая часть этих выходов, которым соответствуют независящие от переноса, повторяющиеся позиции в кодовых словах,результатов, соединены со входами блока 4 коммутации, выходы последнего соединены с соответствующими входами второй группы входов регистра 1 результата. Регистр 1 результата представляе собой группу из N триггеров, единич ные входы которых образуют первую группу входов, а нулевые - вторую группу в}йрдов регистра 1. Единичные выходы триггеров образуют группу вы ходов регистра 1. Матрица 2 коррекции переноса представляет собой пря моугольную матрицу элементов И 11. На схеме фиг, 2 Z и Z - сигналы, соответствующие переносу из младшего разряда нуля и единицы соответст венно, Со,/2 f i, и Ср.1,/2 - сигнал соответствующие полусуммам, равным 0,1()и р-1 соответственно (где р - основание системы счисления). Матрица 2 коррекции переноса содерж только те элементы, которые соответ ствуют .(N-1-1)-ым позициям кодового слова результата (где 1 - номера по зиций этого слова, зависящих от переноса из младшего разряда (О 1i N Если принят алфавит, в котором кодовые слова, соответствующие любым двум соседним (в- алфавите) цифрам, отличаются друг от друга только одной позицией (по уровням напряжений в ней), то матрица имеет минимальны размеры (2хр), каждый вход матрицы коррекции переноса соединен только с одной координатной шиной ее. Если принят алфавит, в котором различия между кодовыми словами, соответствующими соседним цифрам максимальны, то матрица коррекции переноса имеет также максимальные размеры (3 х р) , каждый вход первой группы входов матрицы коррекции переноса соединен с соответствующими j-ми (1 $ j М) ко ординатными шинами каждый вход второй группы - с однойшиной. Выходы элементов И матрицы коррекции переноса, соответствующие одинаковым позициям кодового слова результата, соединены входными диагональными шинами с соответствующими выходами мат рицы 2 коррекции переноса. Матрица 3 сложения представляет собой матрицу многовходовых элементов И.Количество входов каждого элемента И равно 2М Входы элементов И соединены с определенными шинами кодов операндов сог ласно выбранному алфавиту. Шины кодов операндов соединены со входами матрицы сложения. Каждый элемент И имеет по два гальванически независимых выхода. Первые выходы элементов соответствующих одинаковым переносам в следующий разряд, соединены шинами с первой группой выходов матрицы сложения. Вторые выходы, соответствующие одинаковым результатам сложения в данном разряде, соединены шинами со второй группой выходов матрицы 3 сложения. Блок 4 коммутации представляет .собой группу из элементов ИЛИ, где 0 L М, в зависимости от выбранного алфавита. Входы блока коммутации, соответствующие каждой независящей 01переноса и повтор5 1ощейся позиции в кодовых словах (представленных в коде, пртивоположном коду М из N по уровням напряжений) всех возможных результатов, соединены со входами од-, ного и того же элемента ИЛИ. .Выходы элементов ИЛИ являются выходами блока. Существует зависимость между числом элементов ИЛИ блока 4 коммутации и числом элементов И 11 блока 2. Если блок 2 содержитминимальное число элементов И 11(2 х р)„то число элементов блока 4 коммутации максимально L М. Если блок 2 содержит максимальное число элементов И (3 х р), то L О, т.е. необходимость в блоке 4 коммутации отпадает. Устройство работает следующим образом. Операнды в коде М из N поступают на входы матрицы 3 сложения. Если поступают правильные кодовые слова, то срабатывает один из многовходовых элементов И и с его выходов сигналы, соответствующие результату операции, поступают на один из входов матрицы 2 коррекции переноса (на первую группу входов), на одну из выходных шин 7 переноса, на соответствующие входы второй группы входов регистра 1 результата (в том случае, если в кодовом слове результата есть позиции, уровень напряжений в которых не зависит от величины переноса из младшего разряда), и на соответствующие входы блока 4 коммутации (в том случае, если упомянутые выше позиции повторяются в различны.; кодовых словах результатов) . Одновременно с этим, на один из входов второй группы входов матрицы коррекции переноса 2 поступает по входной шине 8 переноса сигнал. Затем срабатывает один или нес- . колько элементов И 11 матрицы 2 коррекции переноса и соответствующие элементы ИЛИ блока 4 коммутации. Сигналы с выходов этих элементов поступают на соответствующие входы второй группы входов регистра 1 результата, образуя вместе с поступившими ранее с выходов второй группы выходов матрицы 3 сложения кодовое слово результата в коде, противоположном (по уровням напряжений) коду М из N. Эти сигналы воздействуют на соответствующие триггеры регистра 1 результата (на нулевые входы), предварительно установленные в единичное состояние. После этого, на выходах блока 1 образуется кодовое слово, соответствующее результату операции в- коде М из N. Появление ошибочных кодовых слоев операндов с меньшим, чем положено. количеством единиц приводит к отсутствию сигналов на всех выходах матри 11ы 3 сложен1 я. Появление ошибочных кодовых слов операндов с большим, чем положено, количеством единиц приводит к появлению на выходах матрицы 3 сложения сразу нескольких сиг налов, которые затем, шифруются матрицей 2 коррекции переноса, блоком 4 коммутации, и непосредственными связями матрицы 3 сложения с регистром 1 результата как результаты нескольких правильных операций, появившихся одновременно в коде, противоположном (по уровням напряжений) коду М из N. Вследствие этого, на выходах регистр 1 результата образуется кодовое -слово с меньшим, чем положено, количест вом единиц, так как большее, чем нуж но, количество триггеров (установленных ранее в единичное состояние) будут переведены в нулевое состояние Такое слово не может быть дешифроваtio как правильное и, следовательно, ошибка не получит дальнейшего распространения. Пример. Примем следующий алфавит для кода 2 из 4 при р 6. 0- ООН 3 - ОНО; 1- 0101; 4 - 1010; 2- 1001; 5 - 1100, где нулевая позиция - крайняя справа Матрица коррекции в этом случае содержит шестнадцать элементов И 11 Непосредственно соединены со входами регистра 1 результата следующие выходы матрицы 3 сложения; Ср у - со входом, соответствующим 3-ей ПОЗИЦИИ; Су /2 - входом, соответствующим 1-ой позиции.. Выходы матрицы 3 сложения и C4,-f/2 соединены со входами элемента ИЛИ, в единственном числе предста ляющем в данном случае блок 4 коммутации. Выход этого элемента соединен со входом регистра 1 результата, соответствующим 0-ой позиции (здесь и ранее речь идет о второй группе входов блока 1). Сложим, например, числа 1 и 3, с учетом переноса единицы из младшего разряда. На одном из выходов первойгруппы выходов матрицы 3 сложения появится сигнал Перенос нуля . Одновременно появляется сигнал на выходе С /i/g второй группы выходов матрицы з сложения и поступает вместе с сигналом Перенос еди ницы (Z) на вход элемента матрицы коррекции переноса 2 (фиг. 4). Кроме того, сигнал поступает на вход элемента ИЛИ блока 4 коммутации С выходов указанных элементов сигнал поступают на входы, соответствующие 1-ой (сигнал с выхода матрицы 2 коррекции переноса) и 0-ой (сигнал с выхода блока коммутации 4) позициям кодового слова результата сложения в коде, противоположном (по уровням напряжений) коду М из N, второй группы входов регистра 1 результата. Поскольку все триггеры регистра 1 результата должны быть к тому моменту установлены в единичное состояние (сигналом, поступившим на первую группу входов), то сигналы, соответствующие 0-ой и 1-ой позициям кодового слова, поступая на нулевые входы триггеров переводят их в нулевое состояние. На выходах регистра результата 1 образуется кодовое слово результата в данном разряде 1100, соответствукддее цифре 5. Положительный эффект от внедрения устройства заключается в повышении быстродействия не менее чем на 25% при построении многоразрядного сумматора, так как в отличие от прототипа значение переноса из младшего разряда (или группы младших разрядов) учитывается в следующем после матрицы сложения блоке - матрице коррекции переноса при образовании (кодового слова результата операции. Формула изобретения 1. Сумматор в коде М из N , содержащий регистр результата и матрицу сложения, причем входы матрицы сложения соединены соответственно с вход-, ными шинами первого и второго опёран дов сумматора, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра результата соединена со входной шиной установки сумматора, отли.Чающийся тем, что, с целью повышения быстродействия, сумматор содержит матрицу коррекции переноса и блок коммутации, причем первая группа выходов матрицы сложения соединена с выходными шинами сумматора, вторая группа выходов матрицы сложения соединена с первой группой входов матрицы коррекции переноса, те из этих выходов, которым соответствуют не зависимые от переноса неповторяющиеся позиции в кодовых словах всех возможных результатов , соединены непосредственно с соответствующими входами второй группы входов регистра результата, другие выходы второй группы выходов матрицы сложения, которым соответствуют не зависимые от переноса повторяющиеся позиции в кодовых словах всех возможных результатов, соединены со входами блока коммутации, выходы блока коммутации соединены с соответствующими входами второй группы входов регистра результата, вторая группа входов матрицы коррекции: переноса соединена со входными шинами переноса сумматора.

2,Сумматор no п. 1, о т л и ч аю щ и и с я тем, что матрица коррекции переноса представляет собой прямоугольную матрицу двувходовых элементов И, причем каждый из входов первой группы ВХОДОВ матрицы коррекции переноса, соответствующий кодовому слову полусуммы, которое отличается по логическим уровням от следующего по алфавиту кодового слова в К позициях (), соединен с первыми входами соответствующих К элементов И, вторые входы которых подключены к соответствующему входу второй группы входов матрицы коррекции переноса.

0

Источники информации, принятые во внимание при экспертизе

кл. G 06 F 7/50,1978.

5 по заявке № 2838 35/18-24,

кл. G 06 F 7/50, 1979 (прототип).

.-

ЛЧ f

ТТ

I atrdj

I

и

1ff

.

11

le}1

1

Т

Ci.li/ вь,х.1 f

Co,4t

Фм.г

n

Т

Cpi.fl

Sf.Z

Sfr.i

Bt.t

Авторы

Даты

1982-08-30—Публикация

1980-12-18—Подача