выход второго инвертора подключен к третьим входам элементов ЗИ второго €лока промежуточной памяти, управляю щие входы аналоговых ключей которого связаны с выходом третьего элемента 2И, третий вход второго элемента «И, второй вход второго элемента 2И и

вход третьего формирователя импульсов связан с первым входом элемента 2И-НЕ, второй вход которого подключен к выходу первого элемента (И, а четвертый вход второго элемента И связан с выходом первого инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Балансировочное устройство | 1981 |

|

SU991207A1 |

| Устройство для коррекции дисбаланса коленчатого вала | 1986 |

|

SU1406456A1 |

| Измерительное устройство к балансировочному станку | 1983 |

|

SU1146562A1 |

| Устройство для коррекции дисбаланса | 1985 |

|

SU1273758A1 |

| Измерительное устройство к балансировочному станку | 1987 |

|

SU1415092A1 |

| Измерительное устройство станка для балансировки коленчатых валов | 1986 |

|

SU1366893A1 |

| Система управления стендом для диагностирования технического состояния транспортных средств | 1988 |

|

SU1553875A1 |

| Устройство для динамической балансировки роторов лучом лазера | 1987 |

|

SU1434301A1 |

| Способ двухцикловой балансировки роторов и устройство для его осуществления | 1987 |

|

SU1446506A1 |

| Измерительное устройство к балансировочному станку | 1983 |

|

SU1096511A1 |

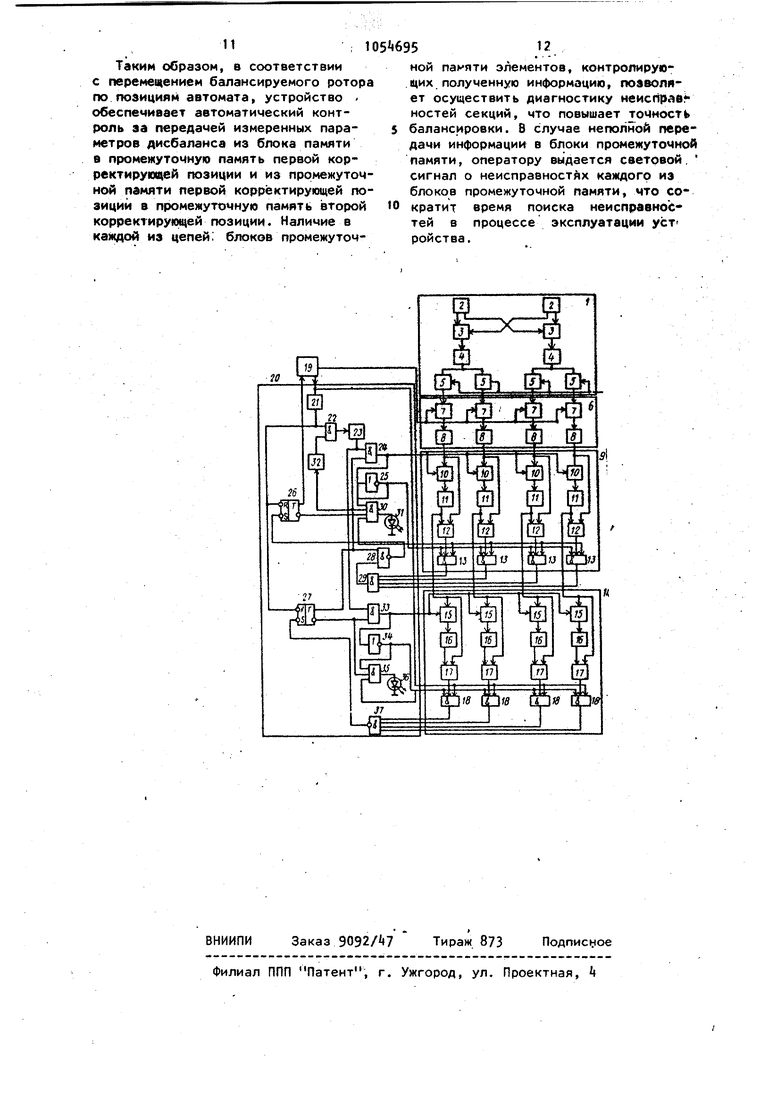

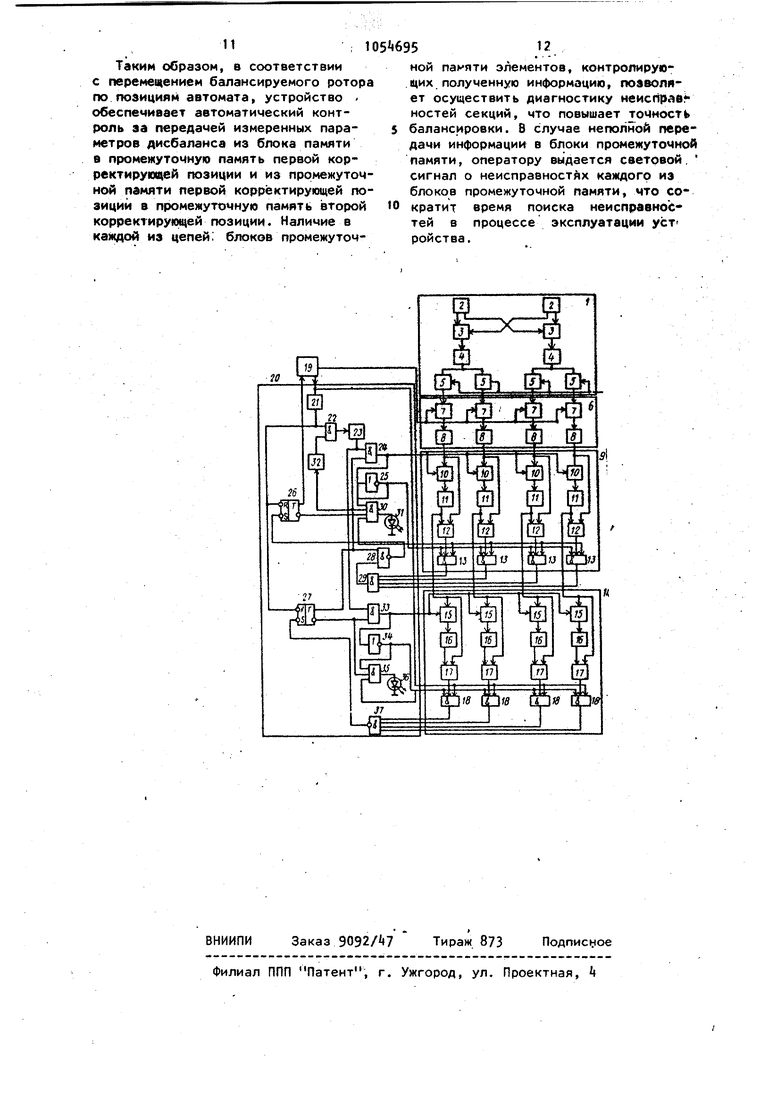

БАЛАНСИРОВОЧНОЕ УСТРОЙСТВО, содержащее после;довательно соединенные двухканальные блок измерения дисбаланса, блок памяти и блок промежуточной памяти, каждый канал которого имеет две цепи, выполненные каждая в виде последовательно соединенных аналогового ключа, запоминающего блока, компаратора, второй вход которого связан с сигнальным входом . аналогового ключа и соответствующим ВЫХОДОМ6noj a памяти, И логического элемента ЗИ, блок управления и блок формирования сигнала, включающий формирователь импульсов, вход которо го соединен с выходом блока управления и вторыми входами элементов JM, триггер, R-вход которого соединен с выходом формирователя импульсов, а выход - с входом блока управления, инвертор, вход которого соединен с управляющими входами ключей, а выход - с третьими входами элементов ЗИ, и элемент 4И, каждый вход KOTOJ рого соединен с выходом одного из j элементов ЗИ, а второй выход блока управления связан с управляющим входом блока памяти, отличающееся тем, что, с целью повышения точности балансировки, оно снабжено вторым, блоком промежуточной памяти, выполненным аналогично первому, последовательно соединенными элементом 2И, вход которого связан с выходом формирователя импульсов, вторым формирователем импульсов и вторым элементом 2И, выход которого связан с входом инвертора, последовateльнo соединенными вторым три|- гером, R-вход которого подключен к R-входу первоГо триггера, и элемен(Л том 2И-НЕ, выход которого соединен с S-входом первого триггера, последовательно соединенными вторым элементом 4И, вход которого связан с инверсным выходом первого триггера, и индикатором, третьим формирователем импульсов, выход которого связан с вторым входом первого элемента 2И, ел последовательно соединенными третьим 4: элементом 2И, входы которого подклюО чены соответственно к выходу второго СО СП формирователя импульсов и инверсному выходу второго триггера, вторым инвертором, элементом ЗИ и. вторым индикатором, элементом 4И-НЕ, каждый вход которого соединен с выходом одного из элементов ЗИ второго блока промежуточной памяти, а выход - с S-входбм второго триггера, вторые входы элементов ЗИ и второго элемента 4И соединены с выходом блока управления , третий вход элемента ЗИ формирователя сигнала связан с инверсным выходом второго триггера.

Изобретение относится к. балансировочной технике и может быть использовано в балансировочных станкахавтоматах с разделенными измерительной и двумя корректирующими позициями.

Известно балансировочное устройство, содержащее последовательно соединенные двухканальные блок измерения дисбаланса, в который входят дат чики, опорный генератор, усилитель, демодулятор и преобразователь, блок промежуточной памяти, каждый канал которого состоит из соединенных последовательно аналогового ключа и запоминающего блока, входы блока соединены с выходами блока измерения через блок памяти, и блок управления предназначенный для формирования системы команд управления блоком измерения и механизмами корректировки, каждый из которых содержит механизм отсчета глубины сверления и мехинизм ориентации ротора по углу. По параметрам дисбаланса, хранящимся в блоках промежуточной памяти, последние управляют работой сверлильных головок.Устройство позволяет произвести замер параметров дисбаланса ротора по двум плоскостям одновременно, запомнить эти параметры и передать их в блок промежуточной памя-ь ти. Цикл работы устройства позволяет производить одновременно замер параметров дисбаланса одного ротора и коррекцию дисбаланса двух других роторов по данным замера в предыдущих циклах результаты которых передаются в блок промежуточной памяти вместе с перемещением ротора с измерительного блока на первый и второй механизмы коррекции .1,

Недостаток данного устройства заключается в том, что оно не обеспечивает требуемой точности балансировки, так как отсутствует контроль за передачей измеренных параметров в блоки промежуточной памяти.

Наиболее близким по технической сущности к изобретению является балансировочное устройство, содержащее последовательно соединенные двухканальные блок измерения дисбаланса, блок памяти и блок промежуточной памяти , каждый канал которого имеет две цепи, выполненные каждая в виде последовательно соединенных аналогового ключа, запоминающего блока, компаратора, второй вход которого связан с сигнальным входом аналогового ключа и соответствующим выходом блока памяти, и логического элемента ЗИ, Длок управления и блок формирования сигнала, включающий формирователь импульсов, вход которого соединен с выходом блока управления и вторыми входами элементов ЗИ, триггер, R-вход которого соединен с выходом формирователя импульсов, а выход - с входом блока управления, инвертор, вход которого соединен с управляющими входами аналоговых ключей, а - с третьими входами элементов ЗИ, и элемент {И, каждый вход которого соединен с выходом одного из элементов ЗИ, а второй выход блока управления связан с управляющим входом блока памяти. Выход элемента И соединен с S-входом триггера, вход инвертора - с выходом формирователя импульсов 21. Устройство позволяет производить одновременно замер параметров дисбаланса одного ротора и коррекцию дисбаланса другого гю данным замера в предыдущем цикле, результаты которого передаются в блок промежуточной памяти вместе с перемещением ротора с изме рительного блока на механизм коррекции. При передаче результатов замера в блок промежуточной памяти устройст во обеспечивает автоматический контроль за передачей измеренных параметров. Недостаток известного устройства заключается в том, что оно не обеспечивает полный контроль за передачей информации блока промежуточной памяти. Высокопроизводительные балан сировочные автоматы, предназначенные для двухплоскостной балансировки, обычно содержат одну измерительную и две корректирующие позиции (одна корректируимцая позиция для левой плоскости коррекции, а вторая - для правой) и на автомате одновременно находятся в обработке три ротора (по одному ротору на каждой из позиций). Для таких автоматов недостаточно одного блока промежуточной памяти, блок формирования сигнала, при мененный в известном устройстве, не обеспечивает ни правильной очередностй перемещения полученной в результате измерения информации по бло кам, ни полного контроля за передачей информации. Это приводит к ошибкам при коррекции дисбаланса ротора и, как следствие, к снижению точности балансировки роторов на автомате Целью изобретения является повышение точности балансировки,; Поставленная цель достигается тем что балансировочное устройство, содержащее последовательно соединенные , двухканальные блок измерения дисбаланса, блок памяти и блок промежуточной памяти, каждый канал которого имеет две цепи, выполненные каждая в виде последовательно соединенных аналогового ключа, запоминающего бло ка , компаратора , второй вход которого связан с сигнальным входом аналогового ключа и соответствующим выходом блока памяти и логического элемента ЗИ, блок управления и блок формирования сигнала, включающий фор мирователь импульсов, вход которого соединен с выходом блока управления и вторыми входами элементов ЗИ, триггер, R-вход которого соединен с выходом формирователя импульсов, а выход - с входом блока управления, инвертор, вход которого соединен с управляющими входами ключей, а вы ход - с третьими входами элементов ЗИ, и элемент И, каждый вход которого соединей с выходом одного из элементов ЗИ, а второй выход блока управления связан с управляющим входом блока памяти, снабжено вторым блоком промежуточной памяти, выполненным аналогично первому, последовательно соединенными элементом 2И, вход которого связан с выходом формирователя импульсов, вторым формирователем импульсов и вторым элементом 2И, выход которого связан с входом инвертора, последовательно соединенными вторым триггером, R-вход которого подключен к R-входу первого триггера, и элементом ZM-HE, выход которого соединен с S-входом первого триггера , последовательно соединенными вторым элементом , вход которого связан с инверсным выходом первого триггера, и индикатором, третьим формирователем импульсов, выход которого связан с вторым входом первого элемента 2И, последовательно соединенными третьим элементом 2И, входы которого подключены-соответственно к выходу второго формирователя импульсов и инверсному выходу второго триггера, вторым инвертором, элементом ЗИ и вторым индикатором, элементом И-НЕ, каждый вход которого соединен с выходом одного из элементов ЗИ второго блока промежуточной памяти, а выход - с S-входом второго триггера, вторые входы элементов ЗИ и второго элемента И соединены -с выходом блока управления, третий вход элемента ЗИ формирователя, сигнала связан с инверсным выходом второго . триггера, выход второго инвертора подключен к третьим входам элементов ЗИ второго блока промежуточной памяти, управляющие входы аналоговых ключей которого связаны с выходом третьего элемента 2И, третий вход второго элемента АИ, второй вход второго элемента 2И и вход третьего формирователя импульсов связаны с первым входом элемента 2И-НЕ, второй вход которого подключен к выходу первого элемента , а четвертый вход второго элемента связан с выходом первого инвертора. На чертеже изображена структурная схема балансировочного устройства. Устройство содержит блок 1 измерения, разделенный на два измерительных канала, ка)кдый из которых выполнен в виде последовательно соединенных датчика 2 дисбаланса, сум51матора 3, усилителя и двух связанных между собой и с выходом усилителя Ц синхронных детекторов 5 причем второй выход датчика 2 дисбаланс одного канала связан с вторым входом сумматора 3 другого канала, блок 6 памяти, состоящий из двух каналов, каждый из которых содержит две цепи, состоящие каждая из последовательно соединенных аналогового ключа 7, свя занного с выходом соответствующего синхронного детектора 5 блока 1 измерения, и запоминающего блока 8, пе вый двухканальный блок 9 промежуточной памяти, каждый канал которого имеет две цепи, каждая из которых- вы полнена в виде последовательно соеди ненных аналбгового ключа 10, запоминающего блока -11, -компаратора 12, вт рой вход которого связан с сигнальны входом аналогового ключа 10 и выходом соответствующего запоминающего блока 8 блока 6 памяти, и элемента 13 ЗИ, второй блок 1k промежуточной памяти, идентичный по конструкции первому блоку 9 промежуточной памяти каждая из цепей которого выполнена в виде последовательно соединенных аналогового ключа 15, запоминающего блока 16, компаратора 17i второй вход которого связан с сигнальным входом аналогового ключа 15 и выходом соответствующего запоминающего блока 11 первого блока 9 промежуточной памяти и элемента 18 ЗИ. Устройство содержит также блок 19 управления и блок 20 формирования сигнала, который выполнен в виде последовательно соединенных формирователя 21 импульсов. вход которого соединен с выходом бло ка 19 управления, элемента 22 2И, второго формирователя 23 импульсов, второго логического элемента 2 2И, выход которого связан с управляющими входам аналоговых ключей 10 блока,9 промежуточной памяти, инвертора 25, выход которого соединен с вторыми входами логических элементов 13 ЗИ блока 9 промежуточной памяти, первого триггера 26, R-вход которого соединен с выходом формирователя 21 импульсов, а выход - с входом блока 19 управления, последовательно соеди ненных второго триггера 27, R-вход которого подключен к R-входу первого триггера 26, и элемента 28 2И-НЕ, выход которого соединен с S-входом первого триггера 26, элемента 29 И, каждый вход которого соединен с вы5ходом одного из элементов 13 ЗИ первого блока 9 промежуточной памяти, последовательно соединенных второго элемента 30 И, вход которого связан с инверсным выходом первйго триггера 26, и индикатора 3, третьего формирователя 32 импульсов, выход которого связан с вторым входом первого элемента 22 2И, последовательно сое-, диненных третьего элемента 33 2И, входы которого подключены соответственно к выходу второго формирователя 23 импульсов и инве рсному выходу второго триггера 27, второго инвертора З, элемента 35 ЗИ и второго индикатора 36, элемента 37 И-НЕ, каждый вход которого соединен с вцходом одного из элементов 18 ЗН второго блока 1 промежуточной памяти, а выход - с S-входом второго триггера 27, вторые входы элементов 13 и 18 и 35 ЗИ и второго элемента 30 4И соединены с выходом блока 19 управления, третий вход элемента 35 ЗИ блока 20 формирования сигнала связан с инверсным выходом второго триггера 27, выход второго инвертора 3 подключен к третьим входам элементов 18 ЗИ второго блока 1 промежуточной памяти, управляющие входы аналоговых ключей 15 которого связаны с выходом третьего элемента 33 2И, третий вход второго ; элемента 30 , второй вход второго элемен-ра 2k 2И и вход третьего формирователя 32 импульсов связан с первым входом элемента 28 2И-НЕ, . второй вход которого подключен к выходу первого элемента 29 , а четвертый вход второго элемента 30 связан с выходом первого инвертора 25. Вторые входы синхронных детекторов 5 связаны с выходами генератора опорных сигналов (на чертеже не показан), а управляющие входы аналоговых клрчей 7 блока 6 памяти - с вторым выходом блока 19 управления. Устройство работает следующим образом. Колебания опор станка(на чертеже не показан), пропорциональные дисба лансу-ротора (на чертеже не показан) , воспринимаются и преобразуются в электрический сигнал датчиками 2 дисбаланса, расположенными в блоке 1 измерения. Так как блок 1 измерения содержит два идентичных канала, то рас ;мотрим работу одного из них, например левого. Сигналы датчика 2 дисбаланса поступают на входы сум71маторов 3 схемы разделения плоскостей коррекции, с помощью которых сигналы датчиков 2 приводятся к заданным плоскостям коррекции. Приве-: денный сигнал с выхода сумматора 3 поступает на вход усилителя сигнала датчика 2 дисбаланса, затем на входы синхронных детекторов 5, управляемых от генератора опорных сигналов. На выходе синхронных детекторов 5 получаем постоянные напряжения пропорциональные проекциям вектора дисбаланса на заданные оси коррекции Эти напряжения через аналоговый ключ поступают на вход запоминающего блока 8, После окончания измерения командой из блока 19 управления закрывается аналоговый ключ 7 и вся информация о дисбалансе ротора хранитс в запоминающих блоках 8. В высокопроизводительных автоматах для балан сировки роторов в двух плоскостях коррекции имеется обычно одна измерительная и две корректирующие позиции (одна для левой плоскости коррекции, а вторая - для правой), и на автомате одновременно находятся три ротора (по одному ротору на каждой из позиций), причем у одного из них дисбаланс измеряется, а у двух других - корректируется. При этом информация о дисбалансе ротора привязывается к положению ротора на автомате: если ротор находится на измерительной позиции, то информация о его дисбалансе находится в запоминающих блоках 8 блока 6 памяти (после окончания цикла измерения). При перемещении ротора с измерительной позиции на первую кор)ектирующую позицию информация о его дисбалансе должна также передвинуться в запоминающие блоки 11 блока 9 промежуточной памяти и храниться там до окончания коррекции дисбаланса в одной из плоскостей коррекции этого ротора. Эта информация используется для отсчета перемещений корректирующих головок в данной плоскости коррекции. Затем ротор перемещается с первой корректирующей позиции на вто рую для коррекции дисбаланса в другой плоскости коррекции (на чертеже не показаны), При этом информация о его дисбалансе должна также передвинуться в запоминающие блоки 16 второго блока 1 промежуточной памят и храниться там до окончания коррекции дисбаланса во второй плоскости. 5 Порядок перемещения информации обычный для устройств с последовательной передачей информации, т.е. сначала должна быть передана информация из первого блока 9 промежуточной памяти во второй блок И промежуточной памяти, а затем из блока 6 памяти - в первый блок 9 промежуточной памяти. Задача передачи информации решается следующим образом. При поступле НИИ команды из блока 19 управления на разрешение передачи информации на вход формирователя 21 импульсов приходит сигнал, и на его выходе формируется отрицательный импульс, длительность которого должна быть больше времени установления триггеров 26 и 27 в нулевое состояние. Импульс с выхода формирователя 21 поступает на R-входы триггеров 26 и 27 и устанавливает их в нулевое состояние. Одновременно этот импульс поступает через логический элемент 222И на вход второго формирователя 23импульсов, который формирует импульс передачи информации, длительность которого выбирается по постоянной времени запоминающих блоков 11 и 16. Второй формирователь 23 импульсов запускается по переднему фронту отрицательного импульса и формирует импульс определенной длительности. Этот импульс поступает на первые входы элементов 2 и 33 2И. На второй вход элемента 33 2И поступает высокий уровень напряжения в инверсного выхода триггера 27, а на второй вход элемента 2ч 2И - низкий уровень напряжения с прямого выхода.триггера 27. Таким образом, импульс положицельной полярности, формируемый вторым формирователем 23 импульсов, проходит через элемент 33 2И на управляющие входы аналоговых ключей 15 блока 1t промежуточной памяти и открывает их, тем самым разрешая передачу информации из запоминающих блоков 11 первого блока 9 промежуточной памяти в запоминающие блоки 16 второго блока 1 4 промежуточной памяти. Время передачи определяется длительностью выходного импульса второго формирователя 23 импульсов. В момент времени, когда значения напряжений на входах аналоговых ключей 15 и на выходах соответствующих запоминающих блоков 1б сравниваются или их разность не превышает значеНИИ уровней компараторов 17, на выходах последних сформируются высокие уровни напряжения. Порог срабаты вания компаратора 17 от нуля (за нуль принимается разность двух сравниваемых и одинаковых по величине напряжений на входе компаратора 17) в обе стороны настраивается одинаковым и выбирается по величине разрешенной-ошибки в передаче информации. Сигналы с выходов компараторов 1 поступают на входы соответствующих элементов 18 ЗИ. Так как второе входы логических элементов 18-ЗИ сое динены с выходом блока 19 управления а третьи - через инвертор 3 и элемент 33 2И с выходом второго формиро вателя 23 иМпульсов, то в момент перезаписи информации из первого блока 9 промежуточной памяти во второй блок 1 промежуточной памяти на выхо дах элементов 18 ЗИ сформируются сиг налы, соответствующие состоянию выхо дов компараторов 17- Эти сигналы поступают на входы элемента 37 И-НЕ. При наличии одновременно на всех вхо дах элемента 37 высоких уровне на его выходе формируется низкий уро вень, который поступает на S-вход триггера 27 и устанавливает его в единичное состояние. С прямого выхода триггера 27 на вход третьего формирователя 32 импульсов поступает команда об окончании передачи информации из первого блока 9 промежуточной памяти во второй блок И промежуточйой памяти. Если хотя бы в одной из цепей за время перезаписи не происходит полной передачи информации , то на выходе элемента 37 не включается низкий уровень и треггер 27 не переключается в единичное состояние. На всех трех входах элемента 35 ЗИ высокие уровни. На его выходе включается высокий уровенъ напряжения, который включает индикатор Зб, сигнализирующий о сбое при передаче информации из первого блока 9 промежуточной памяти во второй блок 1 промежуточной памяти. Если сбоя при передаче информации не произошло, т.е. информация в блок Т промежуточной памяти принята полностью, то триггер 27 переключается в единичное состояние и на входы третьего формирователя 32 импульсов и элемента 2И с прямого выхода триггера 27 поступает высокий уровень. На выходе третьего формироВа-. 1 510 теля 32 импульсов формируется отрицательный импульс, который, пройдя через элемент 22 2И, поступает на вход второго формирователя 23 импульсов, который вновь формирует импульс передачи информации, поступающий через элемент 2 2И на управляющие входы аналоговых ключей 10 первого блока 9 промежуточной па-, мяти. Аналоговые ключи 10 открываются, тем самым разрешая передачу информации из блока б памяти в запоминающие блоки 11 перевого блока 9 промежуточной памяти. В момент времени, когда значения напряжений на входах аналоговых ключей 10 и на выходах соответствующих блоков П сравниваются или их разность не превышает значений уровней срабатывания компараторов 12, на выходах последних сформируются высокие уровни напряжения. Сигналы с выходов компараторов 12 поступают на входы соответствующих логических элементов 13 ЗИ. Так как вторые входы логических элементов 13 ЗИ соединены с выходом блока 19 управления, а третьи - через инвертор 25 и элемент 24 2И с выходом второго формирователя 23 импульсов, то в момент перезаписи информации из блока 6 памяти в первый блок 9 промежуточной памяти на выходах элементов 13 ЗИ сформируются сигналы, соответствующие состоянию выходов компараторов 12. Эти сигналы поступают на входы второго элемента 29 tH. При наличии на всех входах второго элемента 29 4И высоких уровней, на его выходе формируется высокий уровень, который поступает на вход элемента 28 2И-НЕ, низкий уровень с выхода которого поступая на S-вход триггера 26 и устанавливает его в единичное состояние. С прямого выхода триггера 26 в блок 19 управления поступает команда об окончании передачи информации из блока 6 памяти в первый блок 9 промежуточной памяти. Если хотя бы в одной из цепей не происходит полной передачи информации, команда об окончании передачи информации в блок 19 управления не поступает, на выходе элемента 30 появляется высокий уровень, который включает второй триггер 27, сигнализирующий о сбое при передаче информации из блока 6 памяти в первый блок 9 промежуточной памяти. Таким образом, в соответствии с перемещением балансируемого ротора по позициям автомата, устройство обеспечивает автоматический контроль за передачей измеренных параметров дисбаланса из блока памяти в промежуточную память первой корректирующей позиции и из промежуточной памяти первой корректирующей позиций в промежуточную память второй корректирующей позиции. Наличие в каждой из цепей; блоков промежуточls 12 ной памяти элементов, контролирующих полученную информацию, позволяет осуществить диагностику неисправ ностей секций, что повышает точность балансировки. 8 случае неполн ой передачи информации в блоки промежуточной памяти, оператору выдается световой. сигнал о неисправностях каждого из блоков промежуточной памяти, что сократит время поиска неисправное тей в процессе эксплуатации уст ройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Основы балансировочной техники | |||

| Под ред | |||

| В.А | |||

| Щепетильникова | |||

| Т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| М,, Машиностроение, 1975, с | |||

| Электрический прерыватель с воздушным охлаждением | 1923 |

|

SU566A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по зявке К 3318449/25-29, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-11-15—Публикация

1982-07-28—Подача