Изобретение относится к измерительной технике, может быть использо вано в системах контроля и диагности ки неисправностей элементов радиоэлектронной аппаратуры. Известно устройство для обнаружения неисправностей в логических схемах, содержащее счетчик, выходам которого соединены с блоком регистрации, эталонным блоком и контролируемые блоком, соедкня&лал своими выходами с соответствующими входгми блока регистрации и блока сравнения, вторые входы которого подключены к выходам эталонного блока, а выходы .- к блокам индикации и регистрации. Устройство содержит генератор управ.лягацих сигналов, тактовые выхсдаы которого подключены к управляницим входам эталонного и контролируег.юго бло ков, к соответствующим входам блока сравнения, блоков индикации и регист рации и к счетному выходу счетчика; выхсщ установки нуля генератора управляющих сигналов соединен с соответствующими входами счетчика, блока регистрации, эталонного и контроли.руемого блоков, а его входы - с выходами блока;сравнения 1. Это устройство не может быть использовано при диагностике цифровых узлов. Наиболее близко к предлагаемому устройство для контроля интегральных микросхем, содержащее одноконтактный зонд, соединяемый с выводсм контролиру 40й микросхемы, эталонную микросхему, блок сравнения и индикатор исправности 2 .. У этого устройства ограниченные функциональные возможности. Цель изобретения - расширение функциональных возможностей - достигается благодаря тому, что в устройство для контроля интегральных микросхем, содержащее одноконтактный зонд, соединяемый с выводом контролируемой микросхемы, эталонную микросхет у,; . блок сравнения и индикатор исправности, введены блок памяти и коммутатор, причем вход коммутатора соединен с сянеконтактным зондом, а его выходы соединены со входгили блока памяти, выходы которого соединены с соответствующими входами блока среш нения и эталонной микросхемы, выходы которой соединены с соответствующими вхоцами блока сравнения, а выходы последнего

связаны со входом индикатора исправности..

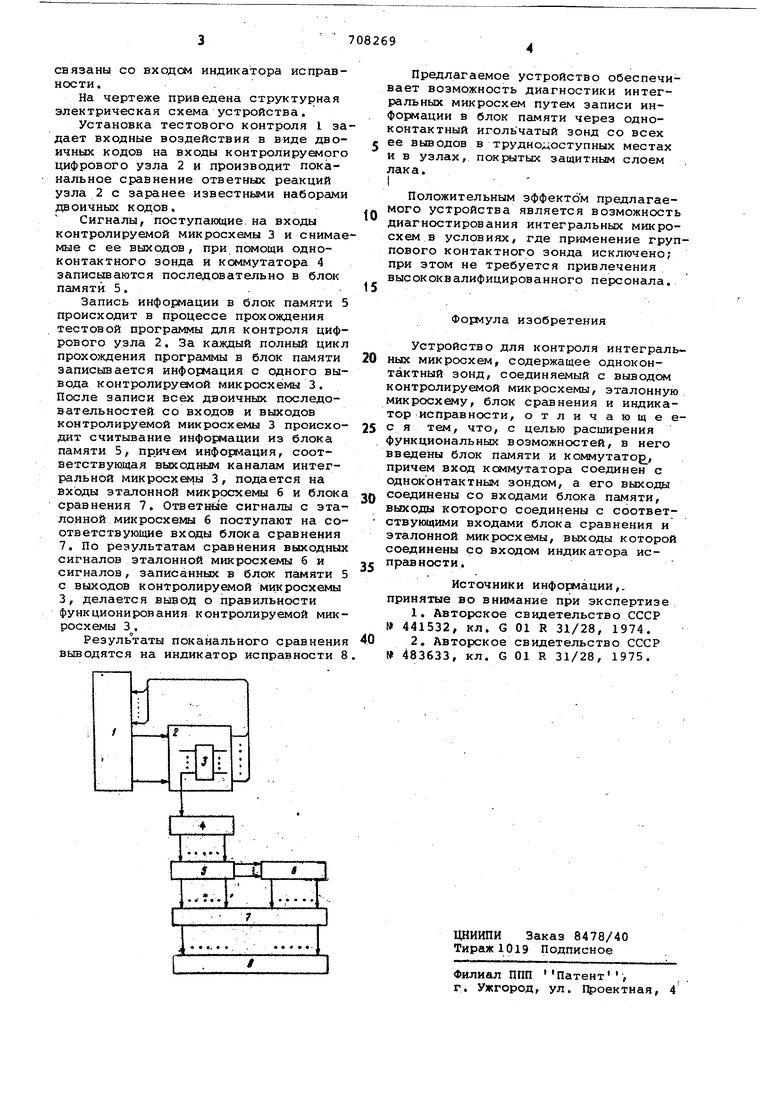

На чертеже приведена структурная электрическая схема устройства.

Установка тестового контроля 1 задает входные воздействия в виде двоИЧН1ЛХ кодов на входы контролируемого цифрового узла 2 и производит поканальное сравнение ответных реакций узла 2 с заранее известными наборами двоичных кодов.

Сигналы, поступающие.на входы контролируемой микросхемы 3 и снимаемые с ее выходов, при помощи одноконтактного зонда и коммутатора 4 записьшаются последовательно в блок памяти 5.

Запись информации в блок памяти 5 происходит в процессе прохождения тестовой программы для контроля цифрового узла 2. За каждый полный цикл прохождения программы в блок памяти записывается информация с одного вывода контролируемой микросхемы 3. После записи всех двоичных последовательностей со входов и выходов контролируемой микросхемы 3 происходит считывание информации из блока памяти 5, причем информация, соответствующая выходным каналам интегральной микросхемы 3, подается на входы эталонной микросхемы б и блока сравнения 7. Ответнйе сигналы с эталонной микросхемы 6 поступают на соответствующие входы блока сравнения 7. По результатам сравнения выходных сигналов эталонной микросхемы б и сигналов, записанных в блок памяти 5 с выходов контролируемой микросхемы 3, делается вывод о правильности функционирования контролируемой микросхемы 3.

Результаты поканального сравнения выводятся на индикатор исправности 8

Предлагаемое устройство обеспечивает возможность диагностики интегральных микросхем путем записи информации в блок памяти через одноконтактный игольчатый зонд со всех 5 ее выводов в трудно;иоступных местах и в узлах, покрытых защитным слоем лака.

Положительным эффектом предлагаемого устройства является возможность диагностирования интегральных микросхем в условиях, где применение группового контактного зонда исключено; при этом не требуется привлечения высококвалифицированного персонала.

Формула изобретения

Устройство для контроля интегральных микросхем, содержащее одноконтактный зонд, соединяемый с выводом контролируемой микросхемы, эталонную микросхему, блок сравнения и индикатор исправности, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены блок памяти и коммутато2, причем вход коммутатора соединен с одноконтактным зондом, а его выходы соединены со входами блока памяти, выходы которого соединены с соответ ствующими входами блока сравнения и эталонной микросхемы, выходы которой соединены со входом индикатора исc ПрёШНОСТИ.

Источники информации,, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 441532, кл. G 01 R 31/28, 1974.

2.Авторское свидетельство СССР №483633, кл. G 01 R 31/28, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных микросхем | 1982 |

|

SU1056089A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Устройство для контроля интегральных микросхем с памятью | 1978 |

|

SU783726A1 |

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| СПОСОБ КОНТРОЛЯ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1986 |

|

SU1417613A1 |

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

Авторы

Даты

1980-01-05—Публикация

1978-06-26—Подача