мы первого peincTjja микрокоманд соединен с первыми входами пятого и шестого элементов И и второго элемента ИЛИ, выход которого соединен с единичным входом триггера управления, выход признака конца микропрограммы второго регистра микрокоманд соединен со вторыми входами второго элемента ИЛИ и пятого элемента И, а так же с первым входом седьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, и через второй элемент задержки с первым входом .восьмого элемента И, единичный выход триггера управления соединен с вторым входом первого эле мента И и через третий элемент за- держки соединен с вторыми входами седьмого и шестого элементов И, выхо которого соединен с вторым входом третьего элемента ИЛИ, через четвертый элемент задержки соединен с первым входом девятого элемента И, выход пятого элемента И соединен с инверсными входами первого, шестого и седьмого элементов И, а также с третьим входом третьего элемента ИЛИ, выход которого соединен с нулевым 2 входом триггера пуска, управляющим входом регистра результата и входом первого элемента задержки, выход первого элемента задержки через пятый элемент задержки соединен с нулевым входом триггера управления и установочными входами первого и второго регистров логических условий, регистра результата и счетчика, выход которого соединен с первым входом схемы сравнения, выходы первого и второго регистров логических условий соединены соответственно с первым и вторым входами блока анализа, выход которого соединен с информационным входом регистра результата, информационный выход, единичный и нулевой выход триггера первого разряда регистра результата соединены соответственно с вторыми входами cxehfti сравнения и вторыми входами восьмого и девятого элементов И, выходы которых соединены соответственно с вторым и третьим входами первого элемента ИЛИ, второй выход генератора импульсов соединен с установочными входами первого и второго регистров микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Динамическое микропрограммное устройство для контроля и управления | 1984 |

|

SU1226454A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

t

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке средств функционального диагностирования мультимикропрограммных систем,

Известно устройство для контроля микропрограмм, содержащее регистры, схему сравнения, элемент задержки и логические элементы И, ИЛИ ГЛ .

Недостатком известного устройств является низкая достоверность контроля, которая обусловлена тем, что устройство обеспечивает обнаружение только одного класса субъектиных ошибок типа тупик V

Известно устройство для контроля микропрограммного автомата, содержащее регистры, триггер, элементы И, ИЛИ и схему сравнения У.

Недостатком известного устройств является также низкая достоверность контроля.

Известен также микропрограммный процессор, в состав которого входит устройство для контроля микропрограми, содержащее счетчик, схему сравнения:

регистр, триггер и элементы (f).

Недостатками известного устройства являются низкая достоверность контроля и узкая область применения. Это обусловлено тем, что оно контролирует ход выполнения микропрограммы путем подсчета числа микрокоманд только в линейной неразветвленной ее части. Кроме того, это устройство не позволяет контролировать микропрограммы.

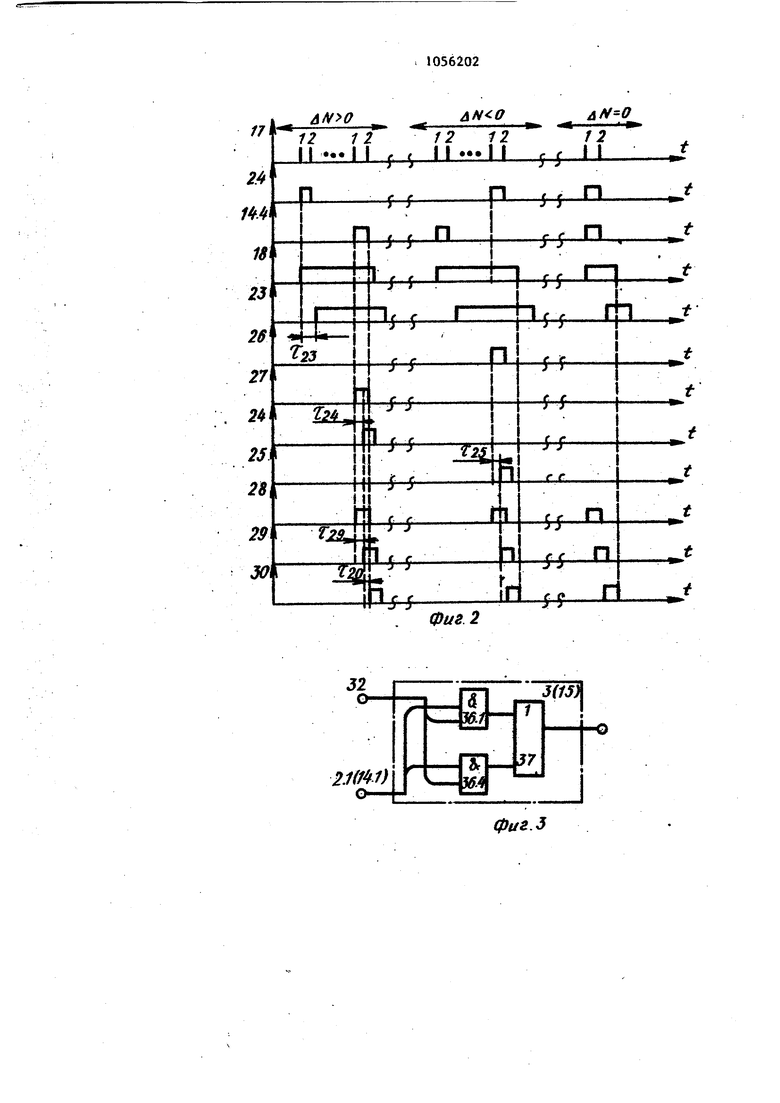

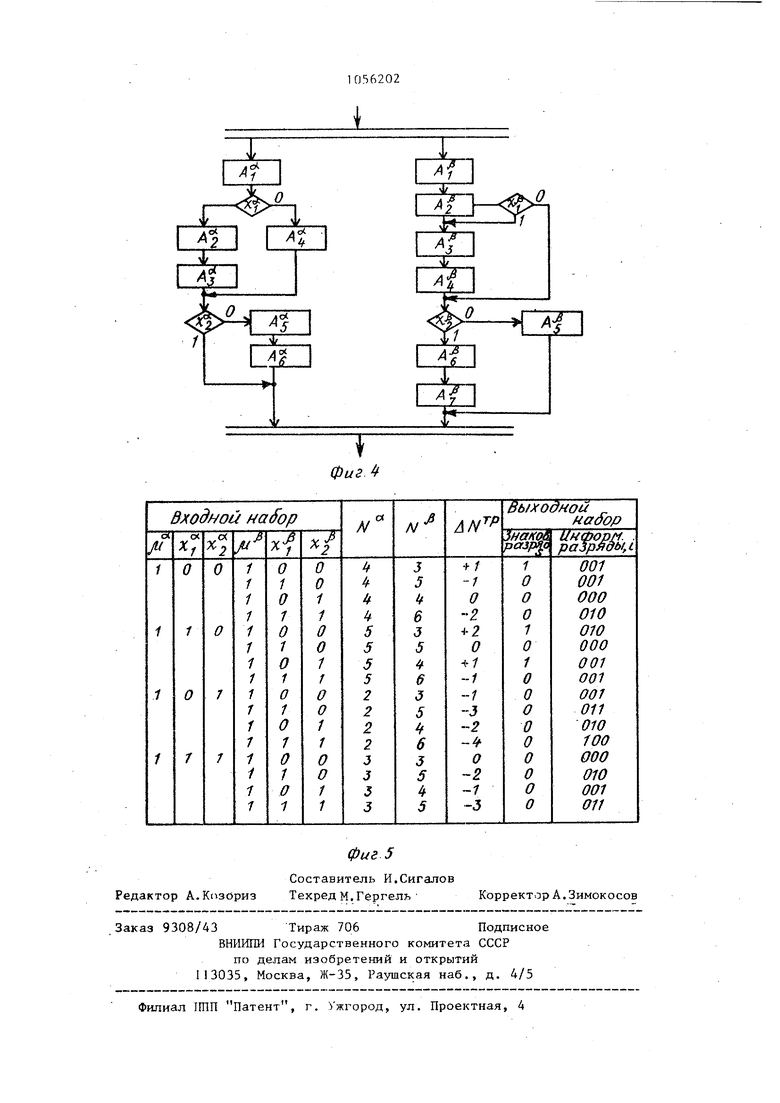

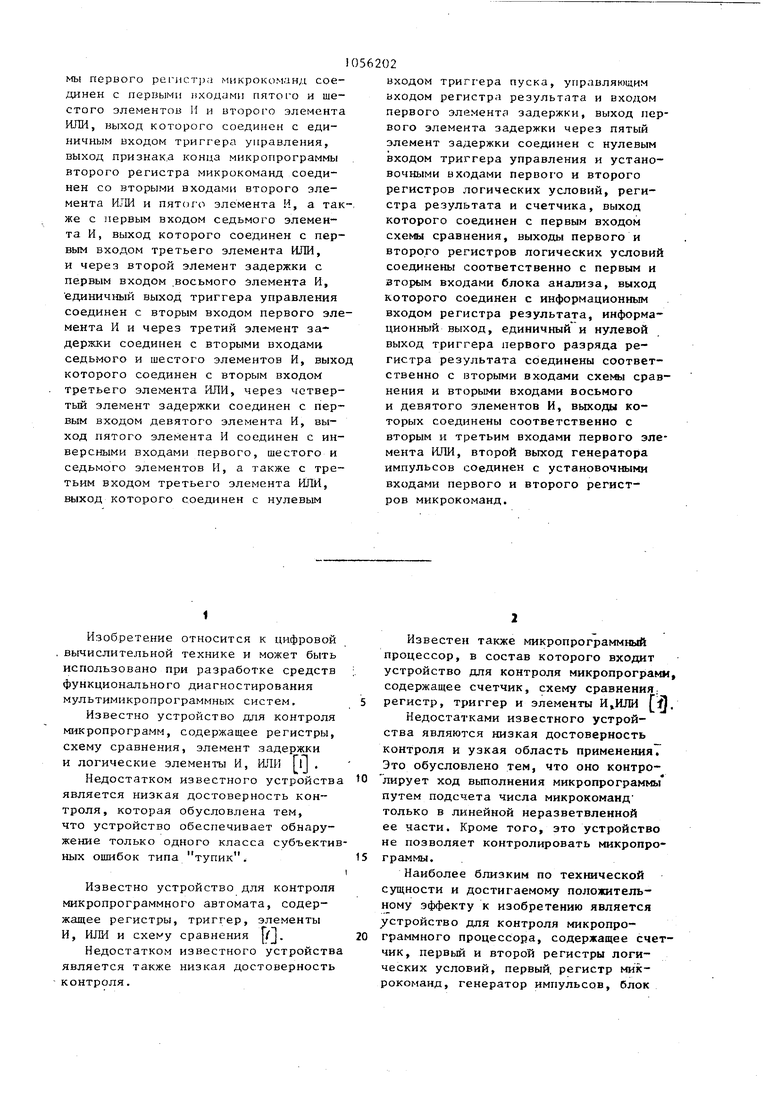

Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является устройство для контроля микропрограммного процессора, содержащее счетчик, первый и второй регистры логических условий, первый, регистр микрокоманд, генератор импульсов, блок анализа, схему сраи {ения, тригтеры пуска и управления, первый коммутатор, первый элемент задержки, первый и второй элементы ИЛИ-, первый - дев тый элементы И, причем вход пуска устройства соединен с еди1 ичным вхо дом триггера пуска, единичный выход которого соединен с управляющим вхо дом генератора импульсов, первый выход генератора импульсов соединен с пер вым входом первого элемента И, выхо которого соединен со счетным входом счетчика, вход логических условий устройства соединен с информационным входом первого коммутатора, выход которого соединен с инфор мационным входом первого регистра логических условий, первый информационный вход устройства соединен с входом первого регистра микрокоманд выходы кода логических условий и метка ветвления которого соединены соответственно с управляющим входом первого коммутатора и первым входом второго элемента И, выход которого соединен с управляющим вхо дом первого регистра логических условий,, выходы схемы сравнения и пер вого элемента задержки соединены с первым и вторым входами третьего элемента И соответственно, выход которого соединен с первым входом первого элемента ИЛИ, выход которого является выходом устройства ( . : Недостатком известного устройства является узкая область применения, которая обусловлена тем, что в нем реализуется контроль последовательных микропрограмм путем под счета числа регшизованных микрокоманд к зависимости от выполняемой ветви (кортежа значений логических условий) и анализа соответствия индексов, изменяющихся в течение микротакта логических условий заданному распределению сдвигов. Это уст ройство ориентировано только на одновременный контроль одной (последовательной) микропрограммы, что су щественно область его применения. Для того, чтобы реализоват контроль параллельных микропрограмм необходимо одновременно использоват два устройства, аналогичных известному, и специальную схему анализа. Такое техническое решение потребует больших затрат оборудования и приводит к снижению надежности устройства. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство для контроля микропрограмм, содержащее счетчик, йервый и второй регистры -логических условий, первый регистр микрокоманд, генератор импульсов, блок анализа, схему сравнения, триггер пуска, триггер управления, первый кйммутатор, первый элемент задержки, первый и второй элементы ИЛИ, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем вход пуска устройства соединен с единичным вход дом триггера пуска, единичный выход которого . соеди.нен с управляющим входом генератора импульсов, первый выход генератора импульсов соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика, вход логических условий устройства соединен с информационным входом первого коммутатора, выход которого соединен с информационным входом первого регистра логических условий, первый информационный вход устройства соединен с входом первого регистра микрокоманд, выходы кода логических условий и метка ветвления которого соединены соответственно с управляющим входом первого коммутатора и первым входом второго элемента И, выход которого соединен с управляющим входом первого регистра логических условий, выходы схемь сравнения и первого элемента задержки соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого является выходом устройства, введены второй регистр микрокоманд, регистр результата, второй коммутатор, третий элемент ИЛИ, второй, третий, четвертый и пятьй элементы задержки, причем второй информационный вход устройства соединен с входом второго регистра микрокоманд, выход кода логических условий которого соединен с управляющим входом второго коммутатора, вход логических условий устройства соединен с информационным входом второго коммутатора, выход которого соединен с- информационным входом второго регистра логических условий, единичный выход триггера пуска соединен с вторым входом вто роге элемента И и первым входом чет вертого элемента И, выход которого соединен с управляющим входом втрро го регистра логических условий, выход метки ветвления второго регистра микрокоманд соединен с вторым входом четвертого элемента И, выход метки конца микропрограмм первого регистра микрокоманд соединен с пер выми входами пятого, шестого элементов И и второго элемента ИЛИ, вы ход которого соединен с единичным входом триггера управления, выход метки конца микропрограммы второго регистра микрокоманд соединен с вто рыми входами второго элемента ИЛИ и пятого элемента И, а также с первым входом седьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, а через второй элемент задержки-с первым , входом восьмого элемента И, единичный выход триггера управления соединен с вторым входом первого элемента И, а через третий элемент задержки соединен с вторыми входами седьмого и шестого элементов И, выход которого соединен с -вторым вх дом/третьего элемента ИЛИ, а через четвертый элемент задержки соединен с первым входом девятого элемента И, выход пятого элемента И соединен с инверсными входами первого, шесто го и седьмого элементов И, а также с третьим входом третьего элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, управляющим , входом регистра результата и входом первого элемента задержки, выход первого элемента задержки через пятый элемент задержки соединен с нулевым входом триггера управления и установочными входами первого и второго регистров логических условий, регистра результата и счетчика, выход которого соединен с первым входом схемы сравнения, выходы первого и второго регистров логических условий соединены соответственно с первым и вторым входами блока анализа, выход которого соединен с информационным входом регистра результата, информационный выход, единичный и нулевой выход триггера первого разряда регистра результата соединены соответственно с вторыми входами схемы сравнения 026 , и вторыми входами восьмого и девятого элементов И, выходы которых соединены соответственно с вторым и третьим входами первого элемента ИЛИ, второй выход генератора импульсов соединен с установочными входами первого и второго регистров микро-, команд. Сущность изобретения состоит в расширении области применения устройства на основе организации одновременного контроля двух параллельно); выполняемых микропрограмм. Контроль параллельных микропрограмм осуществляется путем сравмения действительного и требуемого значений контрольного признака, получаемого путем модификации кода разности числа микрокоманд, содержащихся в ветвях реализуемых параллельных микропрограмм, кодом значений логических условий. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - функциональная схема первого и второго коммутаторов; на фиг. 4 - фрагмент параллельной микропрограммы; на фиг. 5 - фрагмент таблицы соответствия, описывакщей работу блока анаг лиза. Устройство содержит триггер 1 пуска, первый регистр 2 микрокоманд содержащий поля кода логических условий 2.1,метки ветвления 2.2, информационное 2.3 и метки конца первой микропрограммы 2.4, первый коммутатор 3, первый регистр 4 логических условий, блок 5 анализа, регистр 6 результата, восьмой 7 и девятый 8 элементы Н соответстбенно,, первый элемент ИЛИ 9, второй 10 и четвертый 1I элементы И соответственно, схем,1 12 сравнения, третий элемент И 1.3, второй регистр 14 микро- команд с полями кода логических условий 14.1, метки ветвления 14,2, информац {онным 14.3, метки конца второй микропрограммы 14.4, второй коммутатор 15, второй регистр 16 логических условий, генератор 17 импульсов с первым 17,1 и вторым 17,2 выходами,, триггер 18 управления, первый элемент И 19, счетчик 20, пятый элемент И 21, второй элемент ИЛИ 22, третий 23, второй 24 и четвертый 25 элементы задержки соответственно, шестой 26 и седьмой 27 элементы И соответственно, третий элемент ИЛИ 28, первый 29 и пятый 30 элементы задержки соответственно входы пуска 31, логических условий 32, первый 33 и второй 34 информационные входы устройства соответственно, выход 35 устройства. Первый (второй) коммутатор 3 (15 (фиг. З) содержит группу элементов И 36.1-36.И и элемент ИЛИ 37. На .j4 и 5приняты следующие ОООЗНо.Чбп1тЯ А. J I у 4 9 9 7 микрокоманда первой и второй .параллельной микpoпpoгpaй в l, Xj,x,x{,x - - . о логические условия; N ,Nr - количес во микрокоманд в микропрограммах при фиксированных значениях логических условий; ь требуемое зна чение контрольного признака, |U ма разряд. Поясним назначение основных узлов устройства. Регистры 2 и 14 микрокоманд пред назначены для хранения микрокоманд параллельных мшсропрограмм. Эти регистры имеют в соответствии с форма тон микрокоманд чбтыре поля: поле кода логических условий 2.1 (14)j в котором указывается код (номер) проверяемого в данной точке ветвления логического условия; поле метки ветвления 2,2 (14.2), в котором записывается единица только в точках ветвления; информационное поле 2,3 (14.3), в котором записываются операционные и адресные части микрокоманд (адресные части посту. пают на формирователь адреса, а опе рационные на-выход устройства; выходы : этого поля условно не показаны); поле метки конца микропрограмttu 2.4 (14.4), в котором записывается единица только в последней мик рокоманде микропрограммы. Триггер 1 предназначен дпя фиксации сигнала начала параллельного участка, который является пусковым сигналом дпя данного устройства. Элементы И 10 и 11 предназначены для разрешения записи значений логических условий в регистры логичес ких условий по меткам ветвлений в процессе выполнения параллельных микропрограмм. Регистры 4 и 16 логи ческих условий предназначены для записи кода значений логических условий. Запись информации в эти ре. гистры осуществляется через комму28таторы 3 и 15 (фиг. 3). С помощью элементов И 36,I,...,36.П иэ кода значений логических условий, поступающих на входы 32, выделяется один разряд (код на входах 2.1 (14.1) унитарный) и значение проверяемого логического условия через элемент ИЛИ 37 записывается в регистры 4 и 16. Блок 5 анализа предназлачен для формирования кода знакового разряда Sign((iN ) этого числа в зависимости от кодов значений логических условий и является комбинационным кодовым преобразователем. Алгоритм функционирования блока 5 анализа поясняется примером, представлеиным на фиг. 4 и 5. Для данной пар аллельной микропрограммы (фиг. 4) таблица соответствия входных наборов представлена на фиг. 5. Регистр 6 результата предназначен для записи и хранения кода д N, сформированного в блоке 5 анализа, элементы И 7 и 8 - дпя сравнения знаков, схема 12 сравнения - для сравнения абсолютных значений кодов,элемент И 13 - для разрешения выдачи результата сравнения после формирования кода Л в регистре 6. Элемент ИЛИ 9 предназначен ,,ля выдачи сигнала ошибки в случае несовпадения Sign(N ) и-51дп(4МЙ) или кодов/iN / и/i,. Элемент ИЛИ 22 предназначен для форМирования сигнала об окончании лю-бой нли обеих параллельных микропрограмм. Генератор 17 тактовых импульсов обеспечивает синхронизац ло работы. По импульсам с выхода 17.1 производится считывание микрокоманд в регистры 2 и .14, а с выхода 17.2 - их обнуление. Триггер 18 предназначен для фиксации сигнала окончания одной из параллельных микропрограмм. Элемент И 19 предназначен для разрешения подсчета счетчиком 20 кода разности микрокоманд д Мь в случае, если вьшолнение одной микропрограммы уже закончено, а второй еще нет. Элемент 23 задержки предназначен дпя исключения формирования результата контроля по сигналу об окончании выполнения первой микропрограммы. Элемент И 21 предназначен дпя обеспечения сравнения кодов/ i N / , блокировки сравнения знаков Sign() н SignCiNb) и запрещения записи информации в счетчик 20 в случае одновременного окончания выполнения параллельных микропрограмм. Элементы Е 26 н 27 предназначены для формирования сигнала знака Sign() после окончания обеих параллельнь х микропрограмм. Элемент ИЛИ 28 предназначен для формирова,ния сигнала об окончании параллельного участка и записи кодаАМРв ре гистр 65 элементы задержки 24 и 25 для задержки поступления сигнала зн ка Sign(&N) на сравнение его со зн ком Sign(&N) на время записи информации о нем в регистр 6. Элемент 29.задержки предназначен для задерж ки сигнала на вьщачу результата сра нения кодов/Л и/АМ Р/до его за писи 3 регистр 6. Элемент 30 задерж ки предназначен для задержки сигнал на автоматическую установку схемы в исходное состояние до тех пор пока не будет произведено сравнение вели чин / и М Р/и/А , и S i gn (А ) и Sign( Контроль параллелыл 1Х микропрограмм заключается в следующем. В регистрах 4 и 16 логических условий в процессе реализации пара.л лельных микропрограмм записываются коды значений логических условий. По результирующему коду в блоке 5 анализа вычисляется код. После выполнения одной из микропрограмм, на пример - () счетчиком 20 начинается подсчет числа реализуемых да лее микрокоманд в ьадкропрограмме p(U. По окончании выполнения второй микропрограммы Фп(т) вычисляется знак разности Sign{uN). Sign(AN) если последней заканчивается микропрограмма gt SignUN) i 0 если последней заканчивается микропрогра ма Фа . На элементах И 7 и 8 (й сравнивается со знаком разности, . записанным в знаковом разряде регистра 6, В случае несовпадения формируется сигнал ошибки на выходе 35устройства. Сигнал ошибки формируется также при несовпадении кодов (uN) и (flN ) на схеме 12 сравнения. Если обе микропрограммы Р и закончатся одновременно, то знаки .Sign(&N и Sign(aM) не сравниваются, а сравниваются только коды . При автоматической установке схемы в исходное состояние в регистры 4 и 16 логических условий записывается единица в первый разряд. Эта единица служит маркером формируемого кода логических условий. Тогда для формирования кода Л N используется информация, снимаемая с разрядов регистров 4 и 16, расположенных выше первого единичного. Устройство контроля параллельных микропрограмм работает следующим образом. В исходном состоянии все элементы памяти, за исключением регистров 4 и 16 логических условий, находятся в нулевом состоянии, Врегистрах 12 и 13 логических-условий записаны единицы в первых разрядах, По приходу на вход 31 устройства сигнала Начало параллельного участка первый триггер 1 устанавливается в единичное состояние. Сигнал высокого уровня, снимаемый с его выхода, поступает на входы элементов И 10 и II, разрешает запись логических условий в регистры 4 и 16 логических условий и подачу импульсов от генератора 17. Значения логических условий, поступающие на входы 32 устройства записываются в регистры 4 и 6 логических условий по меткам ветвления в микропрограммах, поступающим с полей 2,2 и 14.2 регистров микроманд, через элементы И 10 и П на синхровходы регистров 4 и 16. Сигнал об окончании выполнения микропрограммы, например, Ф () поступает с поля 2.4 (14.4) через элемент ИЛИ 22 на вход (фиг, 2) триггера 18 и устанавливает его в единичное состояние. Тогда при поступлении каждого синхроимпульса считывания очередной микрокоманды (первого выхода генератора )7) на вход элемента И 19 в счетчике 20 формируется код ii.11. Сигнал окончания мшcpoпpoгpaм я I Pj,(P|j} через элемент И 26 (27 не Проходит, так как он 6nokHpoBaH нулевым сигналом, поступающим с выхоа элемента 23 задержки. По приходу сигнала окончания выполнения микропрограммы Тп (Ф) на выходе элемента И 27 (26) появляется сигнал высокого уровня, которьш поступает через элемент ИЛИ 28 на R-вход триггера 1 и С-вход регистра i6. При этом первый триггер I устанавливается в нулевое состояние

и запрещает aiHinci. логических условий н регистры 4 и 16 логических условий. Код U N записывается в регистр 6 результата. С задержкой, равной времени записи регистр 6, осуп(ествляемой элементом 24 (25) задержки, сигнал поступает на вход элемента И 7 (8) и свидетельствует о том что знак разности ЛМ отрицательный (положительный). На другой вход этого элемента поступает сигнал со знакового разряда регистра 6. Этот сигнал равен единице, если 3HaK./gN noложительный, и нулю, если знак М отрицательный.

Таким образом, при несовпадении Sign( и Sign UN) на выходе элемента И 7 (8) появится единичгелй сигнал, который через первый элемент ИЛИ 9 пройдет на выход 33 устройства

Одновремеино со сравнением знака, единичный сигнал с выхода элемента ИЛИ 28 с задержкой на элементе 29 задержки поступает на вход элемента И 13 и разрешает прохождение на выход устройства i4 сигнала результата сравнения кодов / л и j ft Нб |. Эти коды снимаются соответственно с выходов регистра 6 и счетчика 20 и посту,пают на входы 12 сравнения. Если коды не совпадают, то единичный сигнал ошибки с выхода схемы 12 сравнения через элементы И 13 иИЛИ 9 поступает на выход устройства 35.

С задержкой на элементе 30 задержи, равной времени сравнения кодов

М ийКб, сигнал поступит затем на R-входы триггеров 1 и 15, регистра 6, 01-входы регистров 4 и 16 огических условий. При этом триггеры I и 15 и регистр 6 обнуляются, а

в первые разряды регистров 4 и 16 логических условий записываются единицы.

Если выполнение обеих микропрограмм, закончится одновременно, то с выходов полей 2.4 и 14.4 одновременно поступят сигналы, триггер 18 , установится в единичное состояние, но подсчет кода &N6 в счетчике 20 не произведется, так как инверсный вход элемента И 19 запирается сигналом высокого уровня, поступающим с выхода элемента И 21, этим же сигналом запираются элементы И 26 и 27. Единичный сигнал, снимаемый с выхода шестого элемента И 21, поступает на вход элемента ИЛИ 28, что влечет за собой окончание формирования кода а N и запись его в регистр 6 результата, сравнение кода|дМ Ч с |bN&|, автоматическую установку схемы висходное положение аналогично вышеописанному.

Таким образом, предлагаемое устройство позволяет осуществлять в отличи от известных контроль как последовательных, так и параллельных микропрограмм.

Фиг 2

Авторы

Даты

1983-11-23—Публикация

1982-08-24—Подача