ва,выход конца команды выхода микроопераций регистра микроопераций соединен с управляющим входом коммутатора адреса, выход конца работы выхода микроопераций регистра микроопераций соединен с первым входом второго элемента ИЛИ, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, выход которого соединен с вторым входом второго элемента И, выход метки регистра микроопераций соединен с первыми входами третьего и четвертого элемента И, второй выход генератора тактовых импульсов соединен с входами J и С триггера управления, вторьтм входом третьего элемента И, синхровходами триггера значений проверяемых логических условий и триггера отказа, выход блока сравнения соединен с третьим входом треть8.

11

его элемента И, выход которого соединен с первым входом третьего нулевого потенциала, выход которого соединен с К-входом триггера управления, выход которого соединен с четвертым входом третьего элемента И, выход младшего разряда регистра адреса соединен с первым входом схемы сравнения, единичный выход триггера управления соединен с вторым входом схемы сравнения, выход которой соединен с вторым входом четвертого элемента И, выход четвертого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с информагщонным входом триггера отказа, единичный выход триггера отказа соединен с выходом отказа устройства и с вторым входом второго элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, блок сравнения, блок свертки, триггер отказа, первый и второй элементы И, первый, второй и третий элементы РШИ, причем выход регистра адреса соединен с адресным входом блока памяти микрокоманд, р.егистр микроопераций которого соединен с информационным входом регистра микроопераций, отличающееся тем, что, с целью повьппения достоверности функционирования, в него введены регистр тактовых импульсов, триггер пуска, триггер управления, триггер значений проверяемых логических условий, схема сравнения, мультиплексор логических условий, третий и четвертый элементы И, причем вход запуска устройства соединен с единичным входЛм триггера пуска, единичный выход которого соединен с входом генератора тактовых импульсов, второй и первый выходы генератора тактовых импульсов соединены соответственно с входом синхронизации регистра адреса, с входом синхронизации регистра микроопераций, выход поля метки блока памяти микрокоманд соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом синхронизации регистра контрольного признака, выход второго элемента И соединен с первым входом первого элемента ИЛИ и информационным входом триггера значений проверяемых логических условий, йыход микроопераций блока памяти микрокоманд соединен с первым входом блока свертки, выход которого соединен с первым входом блока сравнения, выход контрольного (Л признака блока памяти микрокоманд соединен с управлянщим входом мультис плексора логических условий, с вторым входом блока свертки, с информационным входом регистра контрольного признака, выход которого соединен с вторым входом блока сравнения, выход эо адреса очередной микрокоманды блока О 00 00 00 микрокоманд соединен с третьим входом блока свертки и с первым информационным входом коммутатора адреса, выход мпадшего разряда выхода адреса очередной микрокоманды блока памяти микрокоманд соединен с вторым входом первого элемента ИЛИ, выход которого :оединен с входом младшего разряда lepBoro информационного входа коммутатора адреса, вход кода операций устройства соединен с вторым информационным входом коммутатора адреса,выход которого соединен с информационным входом регистра гщреса, информационный выход регистра микроопераций является выходом микрооперагдий устрочст

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании и построении управляющих устройств и устройств контроля ЦВМ.

Целью -изобретения является повышение достоверности функционирования устройства.f

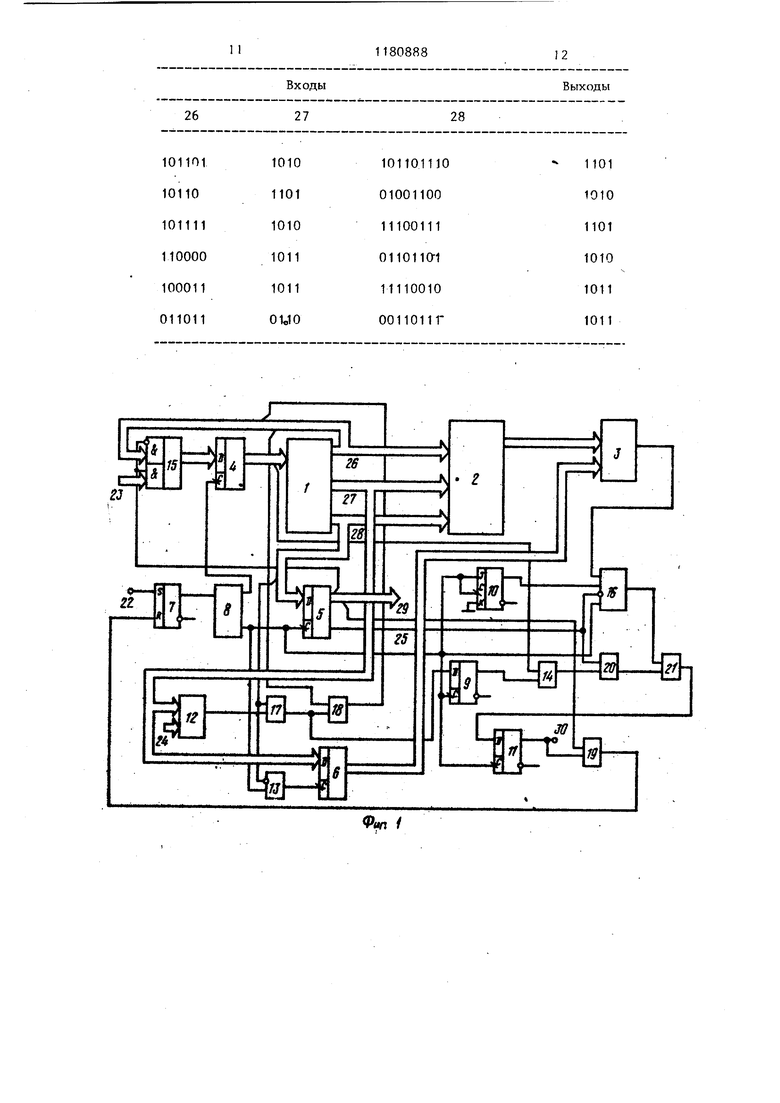

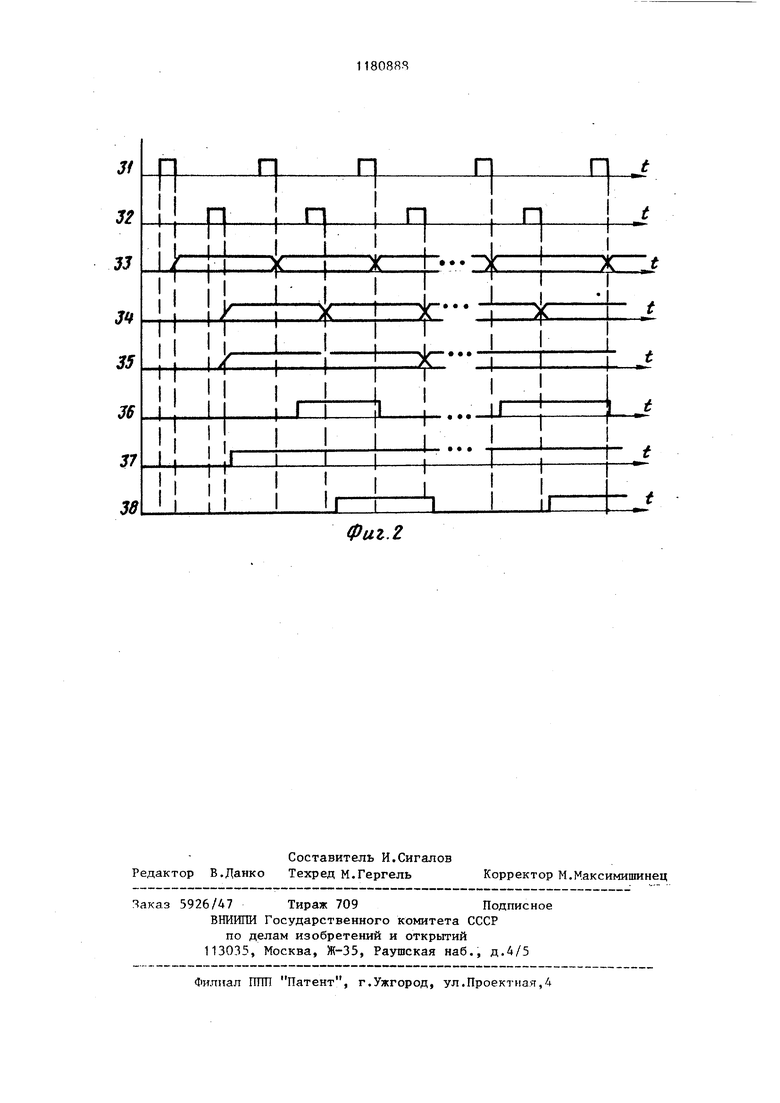

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 времег;ные диаграммы его работы.

Микропрограммное устройство управления содержит блок 1 памяти микрокоманд, блок 2 свертки, блок 3 сравнения, регистр 4 адреса, регистр 5 микроопераций, регистр 6 контрольного признака, триггер 7 пуска, генератор 8 тактовых импульсов, триггер 9 значений проверяемых логических условий, триггер 10 управления, триггер 11 отказа, мультиплексор 12 логических условий, первый элемент И 13, схема 14 сравнения, коммутатор 15 адреса, третий элемент И 16, второй элемент И 17, первый элемент ИЛИ 18,второй элемент ИЛИ 19, четвертый элемент И 20, третий элемент ИЛИ 21, вход 22 пуска устройства, вход 23 кода операций устройства, вход 24 логических условий устройства, выход 25 поля метки регистра 5 микроопераций, выхо 26 адреса очередной микрокоманды выход 27 блока контрольного признака блока 1, вькод 28 микроопераций блока 1 памяти микрокоманд, выход 29 микроопераций устройства, выход 30 отказа устройства.

На фиг. 2 обозначены: первьй и второй выходы 31 и 32 генератора 8 тактовых импульсов соответственно, выход 33 регистра 4 адреса, выход 34 регистра 5 мик;роопераций, выход 35 регистра 6 контрольного признака, значение 36 метки на первом выходе 28 блока 1 памяти микрокоманд, единичный выход 37 триггера 10 управления, единичный выход 38 триггера 9 значений проверяемых логических условий.

В блоке 1 памяти микрокоманд хранятся реализуемые устройством микропрограммы. Формат микрокоманд, считываемых из блока 1 памяти микрокоманд, разбит на три поля: адресное поле, микрооперационное поле и поле логических условий.

Блок 2 свертки осуществляет определение числа единичных разрядов в

микрокоманде, считанной из блока 1 памяти, и формирует фактическое значение контрольного признака.

В регистре 5 микроопераций хранится операционная часть микрокоманды и метка-идентификатор.

В регистре 6 контрольного признака хранится контрольный признак, записанный в поле логических условий микрокоманд, не являющихся микрокомандами ветвления.

Мультиплексор 12 логических условий осуществляет по коду логических условий выделение значения проверяемого логического условия.

Блок 3 сравнения осуществляет сранение фактического значения контрольного признака с требуемым значением.

Триггер 10 управления управляет работой третьего элемента И 16, разрешая формирование сигнала результата сравнения только после реализации первой микрокоманды микропрограммы.

Триггер 9 значений проверяемых логических условий предназначен для хранения значения условия переходав узле ветвления микропрограммы.

Триггер 11 отказа формирует сигнал отказа (сбоя) и блокирует работу устройства. .

В формате каждой микрокоманды,считываемой из блока 1 памяти микрокоманд, записывается адрес очередной микрокоманды, код проверяемых логических условий или контрольный признак в зависимости от типа считываемых микрокоманд, микрооперационная часть.

В микрооперационной части каждой микрокоманды, кроме того, записьгоают ся признак окончания команды и признак окончания работы устройства.

Значение метки равно 1 для всех микрокоманд ветвления, а во всех остальных микрокомандах микропрограммы равно О.

Значение контрольного признака, записанного в поле логических условий j-й микрокоманды, определяет количество единичных разрядов в формат очередной (j+1)-й микрокоманды.

Реализация микропрограммы и контроль правильности считывания микрокоманд из блока 1 памяти микрокоманд в предлагаемом устройстве осуществляется следующим образом.

После считьгоания д-й микрокоманды из блока 1 памяти микрокоманд на его

выходах появляется следуюп1ая информация: адрес очередном микрокоманды который поступает на вход коммутатора 15 адреса, а также блок свертки, контрольньй признак Rj который поступает на входы блока 2 свертки, регистра 6 контрольных признако и мультиплексора 12 логических условий, микрооперационная часть j-oii микрокоманды, которая поступает на вход блока.2 свертки и на вход регистра 5 микроопераций. Если считываемая j-я микрокоманда не является микрокомандой ветвления, то знечение в поле метки равно О. В этом случае информация с выхода поля логических условий запишется в регистр 6 контрольного признака. После записи микрооперационной части i-й микрокоманды в регистр 5 микроопераций произойдет запись адреса очередной (.1+1)-и микрокоманды в регистр 4 адреса. Кроме того, блок 3 свертки, проанализировав информацию на своих входах, вьщает на своем выходе код фактического значения контрольного признака (фактического значения числа единичных разрядов считанной j-й микрокоманде).

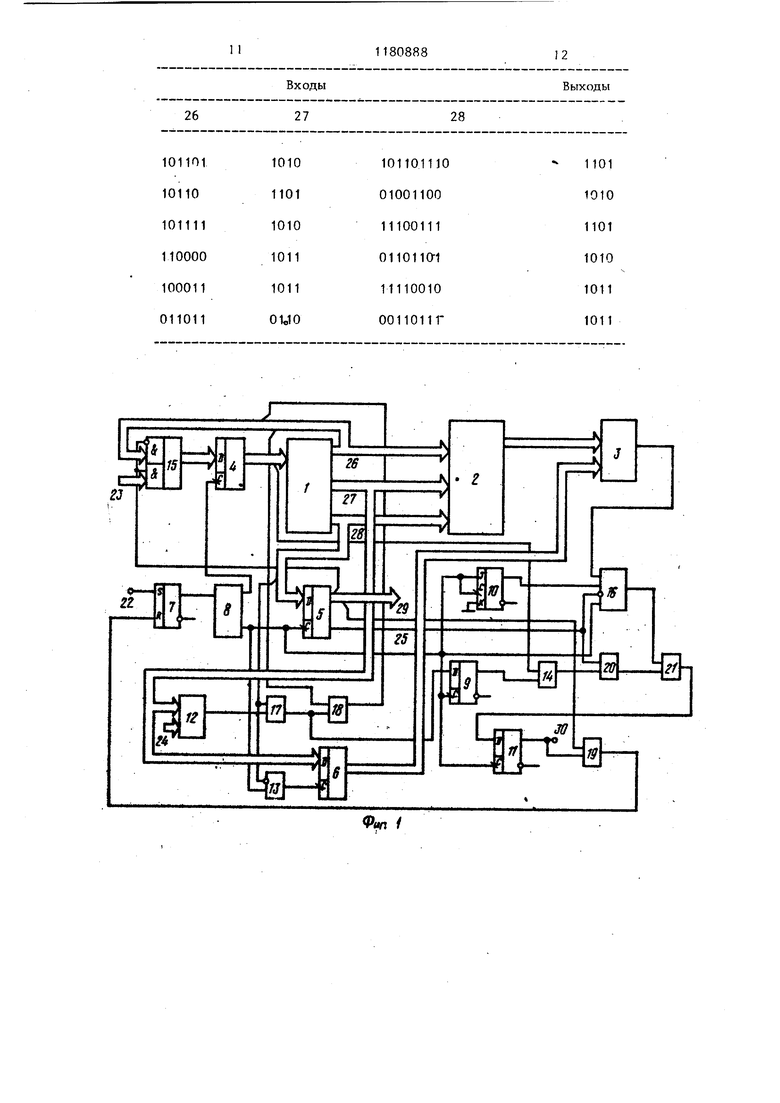

В таблице поясняется-работа блока 2 свертки, на входы которого поступает код микрокоманды с выходов блока

1памяти (адресная часть - с выхода 26, код логических условий (контрольного признака) - с выхода. 27, микрооперационная часть - с вьпсода 28),

а на выходе формируется код числа единиц в коде микрокоманды.

Так, например, если на входы блока 2 поступает код микрокоманды 1011111100111100111, содержащий 13 единиц, то на выходе формируется двоичный код этого числа 1101. Нпок

2может быть легко реализован на программируемой логической матрице.

В блок 3 сравнения с выхода регистра 6 контрольного признака поступит требуемое значение контрольного признака, записанное в него при считывании (j-l)-u микрокоманды. В зависимости от требуемого и фактического значения контрольного признака на выходе блока 3 сравнения будет сформирован единичный сигнал в случае несовпадения требуемого и фактического значе1|ий контрольного признака и нулевой - в случае их

равенства. Таким образом, произойдет сравнение фактического значения контрольного признака, полученного в блоке 2 свертки после считывания j-й микрокоманды требуемого его значения, записанного в регистр 6 контI рольного признака при считывании (j-1)-ft микрокоманды. При неправильном функционировании устройства (сбое или отказе в адресных или операционных цепях устройства) сигнал с выхода блока 3 сравнения поступит на вход триггера 11 отказа, и в устройстве будет блокирована работа генератора 8 тактовых импульсов. В случае правильной реализации 1-й микрокоманды работа устройства будет продолжена. В этом случае в регистр. 6 запишется требуемое значение контрольного признака (л+1)-й микрокоманды. После ее считывания из блока

1памяти микрокоманд на выходе блока

2свертки будет сформировано фактическое значение контрольного призна.ка микрокоманды.

В зтом случае, если считываемая микрокоманда является микрокомандой ветвления, то работа устройства будет осуществляться следующим образом

После считьшания микрокоманды ветвления из блока 1 памяти микрокоманд как и в случае реализации обычных микрокоманд, произойдет проверка Требуемого значения контрольного признака, записанного в регистр 6, и фактического значения контрольного признака, сформированного на выходе блока 2 свертки. В случае их совпадения работа устройства будет осуществляться следующим образом. Поскольку значение метки в микрокомандах ветвления равно 1, то информация в регистр 6 записана не будет. На выходе мультиплексора 12 логическйх условий по значениям логических условий, поступившим от объекта управления, будет сформирован сигнал значений логических условий.

При положительном исходе проверки значений логических условий значение этого сигнала равно 1, в противном случае О. При положительном исходе проверки логических условий будет осуществлена модификация адреса очередной микрокоманды, следующей за микрокомандой ветвления. Значение младшего разряда адреса очередной микрокоманды, к которой осуществляется переход, будет равно 1. При отрицательном исходе проверки значений логических условий значение этого разряда равно О. Признак результата исхода проверки значения логических условий записывается в триггер 9 логических условий. После записи адреса очередной микрокоманды, к которой осуществляется переход в микропрограмме в регистр 4 адреса, значение младшего разряда этого адреса с выхода регистра 4 адреса поступает на вход схемы 14сравнения. В этом случае, если значение младщего разряда адреса микрокоманды перехода соответствует значению проверяемых логических условий, то работа устройства будет продолжена, в противном случае происходит блокировка.

Таким образом, микропрограммное устройство управления осуществляет проверку правильности, реализации микропрограмм путем организации потактного контроля правильности вьтолнения функций переходов и функций выходов, а также правильности организа1ЩИ перехода в узлах ветвления микропрограмм.

Микропрограммное устройство управления работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии Значение сигнала на выходе 29 регистра 5 микроопераций равно 1 (цепи установки исходного состояния условно не показаны). Код операции поступает на второй информационный вход коммутатора 15 адреса и далее на информационньй вход регистра 4 адреса. На единичный вход триггера 7 пуска поступает сигнал пуска,и на его единичном выходе появляется сигнал, который включает генератор 8 тактовых импульсов. По заднему фронту первого импульса, поступившего с его выхода на синхровход регистра 4 адреса, произойдет запись кода операций в регистр 4 адреса. lio этому коду из блока 1 памяти микрокоманд будет считана первая микрокоманда микропрограммы. На адресном выходе 26 блока 1 памяти микрокоманд появится адрес очередной микрокоманды. На выходе 27 логических условий появится контрольньй признак, записанньй в поле логических условий считанной микрокоманды. На выходе 27 микроопераций - мик рооперационная часть первой микрокоманды. Информация с. этих выходов блока 1 памяти микрокоманд поступит также на соответствующие входы блока 2 свертки, на выходе которого будет « сформировано фактическое значение контрольного признака. Поскольку в исходном состоянии все элементы памяти находятся в нуле ном состоянии, то на выходе поля мет ки регистра 5 микроопераци и на еди ничных выходах триггеров 9-11 будет присутствовать нулевой сигнал. Нулевой сигнал, поступающий с единичного выхода триггера 10 управления на чет вертый вход третьего элемента И 16, блокирует его. Нулевой сигнал, посту пающий с поля метки регистра 5 на пе вьй входчетвертого элемента И 20, блокирует работу этого элемента. По синхроимпульсу, поступающему с второ го выхода генератора 8 тактовых им;пульсов, на выходах третьего 16 и , четвертого 20 элементов И будет сфер мирован нулевой сигнал, который,прой дя через третий элемент ИЛИ 21 посту пит на- информационный вход триггера 11 отказа. По этому же импульсу на выходе первого элемента И 13 будет Сформирован единичный сигнал, который поступит на синхровход регистра 6 контрольного признака и разрешит тем самым запись в него контрольного признака, поступающего с второго вых да 27 блока 1 памяти микрокоманд и записанного в поле логических условий первой шкpoкoмaнды. По заднему фронту этого импульса микрооперационная часть первой микрокоманды и метка запишутся в регистр 5 микроопераций, триггер 10 управления перейдет в единичное состояние, а в триггере 9 и триггере 11 по заднему фронту этого импульса будет подтверждено их нулевое состояние. Значения сигналов микроопераций поступят с выхода 29 регистра 5 микроопераций на выход устройства. Нулевой сигнал с выхода конца команды выхода 29 регистра 5 микроопераций поступит на первый управляющий вход коммутатора 15 адреса, и адрес очередной микрокоманды поступит на информационный вход регистра 4 адреса. По заднему фронту очередного тактово го импульса, поступившего с первого выхода генератора 8 тактовых импульсов на синхровход регистра 4 адреса, произойдет запись адреса второй микрокоманды в этот регистр и ее считывание из блока 1 памяти микрокоманд. При этом значение младшего разряда кода адреса микрокоманды поступает на первьй вход схемы 14 сравнения, на второй вход которой поступает нулевой сигнал с единичнлго выхода триггера 9 логических условий. Сигнал результата сравнения поступает с выхода схемы 14 сравнения- на. второй вход четвертого элемента И 20, который по-прежнему закрыт нулевым сигналом с выхода поля метки регистра 5 микроопераций. На выходе четвертого элемента И 20 будет сформирован нулевой сигнал. С выходов 26-28 блоков 1 памяти микрокоманд информация поступит на соответствующие входы блока 2 свертки, а также на входы коммутатора 15 адреса, регистра 5 микроопераций и регистра 6 контрольного признака, соответственно. На выходе блока 2 свертки будет сформировано фактическое значение KOHTpojibHoro признака, которое поступит на первьм информационный вход блока 3 сравнения. На второй вход этого блока поступит требуемое значение R контрольного признака. При правильном функционировании устройства на третий вход открытого третьего элемента И 16 поступит нулевой сигнал, который закрьшает его. В том случае, если на выходе блока 3 сравнения будет единичньй сигнал, что говорит о неравенстве R и R , после поступления импульса опроса на второй вход третьего элемента И 16 единичный сигнал через третий элемент ИЛИ 21 поступит на вход триггера 11 отказа. По заднему фронту этого же импульса триггер 11 отказа перейдет в единичное состояние и через второй элемент ИПИ 19 установит в О триг-, гер 7 пуска. В результате работа устройства будет блокирована. В этом случае, если микрокоманда считана правильно, устройство будет функционировать до тех пор, пока не будет считана из блока 1 памяти микрокоманд микрокоманда ветвления. При этом произойдет контроль правильности ее считывания из блока памяти икрокоманд по рассмотренному алгоитму. Сигнал метки с выхода 28 бло9 .1 ка 1 памяти микрокоманд закрывает первый элемент И 13 и открывает второй элемейт И 17. Код проверяемых логических условий с выхода 27 блока 1 памяти микрокоманд поступает на вход мультиплексора 12 логических условий. Значение проверяемого логического условия фop шpyeтcя на выходе мульти плексора 12. При положительном исходе проверки значений логических условий единичный сигнал поступит на второй вход второго элемента И 17-и далее на вход первого элемента ИЛИ 18, на второй вход которого поступает нулевое значение модифицируемого младшего разряда адреса. Модифицированный таким образом адрес первой микрокоманды, следующей за микрокомандой ветвления, поступает на первый инфор мационный вход коммутатора 15 адреса и далее в регистр 4 адреса. Единичньй сигнал с выхода второго элемента И 17 поступает также на инфор;мадионный вход триггера 3 логических условий. По тактовому импульсу, поступающе1-1у с второго выхода генератора 8 на второй вход третьего элемента И 16, произойдет опрос результата контроля правильности считьгоания мик рокоманды ветвления из блока 1 памят микрокоманд. Если микрокоманда ветвления счита на правильно, то по заднему фронту этого импульса будет подтверждено ну левое состояние триггера 11 отказа, триггер 9 логических условий перейде в единичное состояние, в регистр 5 микроопераций будет записана микрооперационная часть микрокоманды ветвления . На выходе поля метки этого регистра будет сформирован единичный сигнал, который закроет третий элемент И 1 б и откроет четвертьй элемен И 20. По очередному тактовому импуль су, поступившему с первого выхода 8, произойдет запись кода адреса микрокоманды, следующей за микрокомандой ветвления, в регистр 4 адреса и считывания этой микрокоманды из блока 1 памяти микрокоманд. Значение младшего разряда кода адреса этой микрокоманды поступает на первый вход схемы 14 сравнения. Условием правильного перехода в микропрограмме по положительному исходу проверки логических условий является единичное значение младшего рязряда кода адреса. Таким образом, в случае правильного/перехода в микропрограмме на первый вход схемы 14 сравнения поступает единичный сигнал и на его выходе будет сформирован нулевой сигнал. В случае неправильного вьтолнения перехода значение сигнала на выходе четвертого 20 элемента И будет равно 1, сигнал с выхода четвертого элемента И 20 поступит через третий элемент ИЛИ 21 на информационньй вход триггера 11 отказа и по заднему фронту импульса с второго выхода генератора 8 установит его в 1,и работа устройства будет блокирована. В том случае, если значение проверяемых логических условий будет равно О, модификация адреса микрокоманды перехода производиться не будет, и триггер 9 логических условий останется в нулевом состоянии. После записи кода адреса микрокоманды перехода в регистр 3 адреса произойдет сравнение значения младшего разряда кода адреса этой микрокоманды и нулевого сигнала с единичного выхода триггера 9 логических условий. Результатом ошибочного перехода в микропрограмме будет единичное значение младшего разряда кода адреса микрокоманды перехода. Тогда на выходе схемы 14 сравнения будет сЛормирован единичньй сигнал, которьй установит триггер 11 в 1 и блокирует работу устройства.

Фиг. 2

| Микропрограммное устройство с контролем | 1982 |

|

SU1020827A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015384A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-03-11—Подача