(54) ПРОЦЕССОРНЫЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный процессорный элемент | 1982 |

|

SU1057938A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| Процессорный элемент | 1980 |

|

SU881757A1 |

| Ассоциативный процессорный элемент | 1980 |

|

SU879593A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Запоминающее устройство | 1989 |

|

SU1711229A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Устройство для контроля перемещения подвижных объектов | 1989 |

|

SU1652965A1 |

| Процессор | 1981 |

|

SU962964A1 |

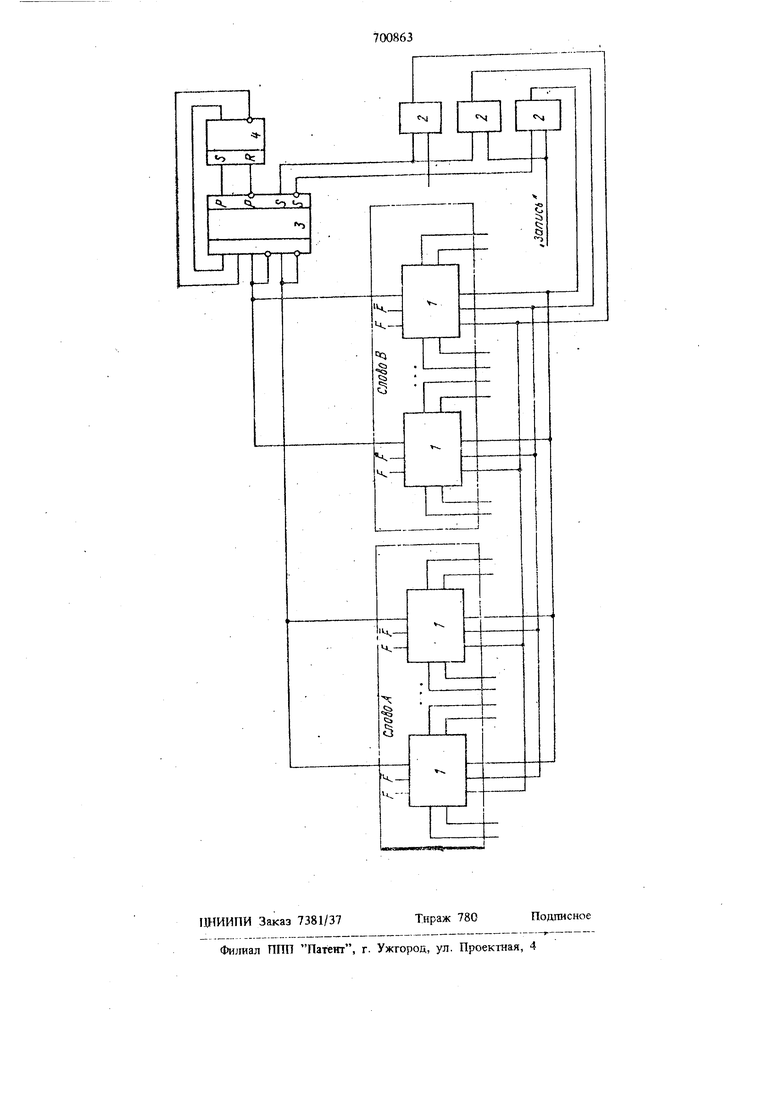

Изобретение относится к вычислительной те нике и может быть использовано при построени ассоциативных процессоров. Известен процессорный модуль, содержащий триггеры, элементы И, ИЛИ 1. Недостатком его является низкое быстродействие. Наиболее близкое к изобретению техническое решение - процессорный модуль, содержащий две группы ячеек памяти, входы разрешения записи которых соединены с выходом первого злемента И, входы разрешения считывания ячеек памяти соединены с выходом второго элемента И, первые входы первого и второго элементов И являются первым и вторым входами модуля, а вторые входы соединены с первым прямым выходом сумматора, второй прямой и инверсный выходы которого соединены с входами триггера, выходы которого подключены к первому и второму входам сумматора, третий и четвертый входы которого подключены к выходам ячеек памяти соответственно пер вой и второй групп. Модунь содержит кроме того ячейки памяти записи результата {2, Недостаток модуля состоит в низком быстродействии. Цель изобретения - повышение быстродействия модуля. Цель достигается тем, что предлагаемый модуль содержит третий элемент И, первый вход которого является третьим входом модуля, второй вход соединен с первым инверсным выходом сумматора, а выход подключен к входу разрешения записи инверсного кода каждой ячейки памяти. На чертеже показан предлагаемый модуль. Модуль содержит ячейки 1 памяти, элементы И 2, сумматор 3, триггер 4. Модуль работает следующим образом. В первую и вторую группы ячеек памяти записываются соответственно первый и второй операнды. При выполнении команды опрос запись и подаче на входы опроса разрядов операндов, а на входы записи сигнала S 1, на прямом выходе сумматора формируется сигнал, равный результату суммирования разрядов и содержимого триггера, а на выходе третьего элемента И появляется его инверсия. 370 Единичный сигнал на прямом выходе сумматора позволяет записать единичный результат суммирования, а сигнал на инверсном выходе нулевой результат- суммирования. Таким образом, результат одноразрядной операции может быть записан без предварительной обработки, а следовательно, быстродействие предлагаемого модуля выше известных. Формула изобретения Процессорный модуль, содержащий две группы ячеек памяти, входы разрешения записи . которых соединены с выходом первого элемента И, входы разрешения считывания ячеек памяти первой и второй групп соединены с выходом второго элемента И, первые входы первого к второго элементов И являются соответственно первым и вторым входами модуля, а вторые входы соединены с первым прямым выходом сумматора, второй прямой и инверсный выходы которого соединены с входами триггера, выходы которого подключены к первому и второму входам сумматора, третий и четвертый входы которого подключены к выходам ячеек памяти соответственно первой и второй групп, отличающийся тем, что, с целью- повышения быстродействия, он содержит третий элемент И, первый вход которого является третьим входом модуля, второй вход соединен с первым инверсным выходом сумматора, а выход подключен к входу разрешения записи инверсного кода каждой ячейки памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 479114, кл. G 06 F 7/38, 1972. 2.Медведев И. Л., Прангишвили И. В,, Цудин А. А. Многопроцессорные вычислительные системы с перестраиваемой структурой, М.ИПУ, 1975, с. 42, 43 (прототип).

Авторы

Даты

1979-11-30—Публикация

1978-05-04—Подача