Изобретение относится к технике связи и может использоваться в вычислительных системах с перестраиваемой структурой, а также в электронных автоматизированных телефонных станциях. .

Известно устройство для временной коммутации каналов, содержащее первый- распределитель, выходы которого подключены к блоку памяти и блоку стробирования, состоящего из П ключей, соединенных с информационными входами устрбйства, и об1чего ключа, выход которого подключен к блоку логических элементов, соединенных с выходами устройства, а другими входами - с выходами второго распределителя , подключенного первым входом к выходу счетчика и входу общего ключа, вторым входом - к выходу блока управления, подключенного выходами к входам первого распределителя и счетчика, входы которого соединены с выходами блока памяти l .

Нед(.1статком устройства является сложность, вызванная матричной организацией устройства временной коммутации .

Известно также устройство для временной коммутации каналов, содержащее блок уплотнения, информационные входы которого подключены к информационным входам устройства, адресные входы - к выходам дешифратора адреса входа, а информационный выход блока уплотнения соединен с информационным входом расширителя, информационные выходы которого подключены к информационным выходам устройства, блок памяти, адресные входы которого соединены с выходами дешифратора адреса, а информационные входы и выходы - с первыми информационными входами и выходами регистра адреса, вторые информационные входы регистра адреса подключены к информационным входам памяти, блок управления, входы и выходы которого соединены соответственно с управляющими входами и выходами устройства, а управляющие выходы - с управляющими входами регистра адреса и счетчика адреса, подключенного входами к адресным входам устройства, а выходом к дешифратору . адреса 2 .

Недостаток известного устройства - сложность, связанная с наличием дополнительных регистра адреса,счетчика адреса, дешифратора адреса.и большого объема памяти.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что ri синхронном адресно-временном устройстве коммутации, содержащем блок уплотнения, информационные входы которого подключены к информационным входам устройства, адресные входы - к выходам дешифратора адреса входа, а информационный выход блока уплотнения соединен с информационным входом расширителя, информационные выходы которого подключены к информационным выходам устройства, блок памяти, адресные входы которого соединены с выходами дешифратора адреса, а информационные входы и выходы - с первыми информационными входами и выходами регистра адреса,, вторые информационные входы регистра адреса подключены к информационным входам памяти, блок управления, входы и выходы которого соединены соответственно с управляющими входами и выходами устройства, а управляющие выходы - с управляющими входами регистра адреса и счетчика адреса, подключенного входами к сицресным входам устройства, а выходом - к дешифратору адреса, выходы дешифратора адреса соединены с (адресными входами расширителя, а вторые информационные выхода регистра адреса подключены к входам дешифратора адреса входа.

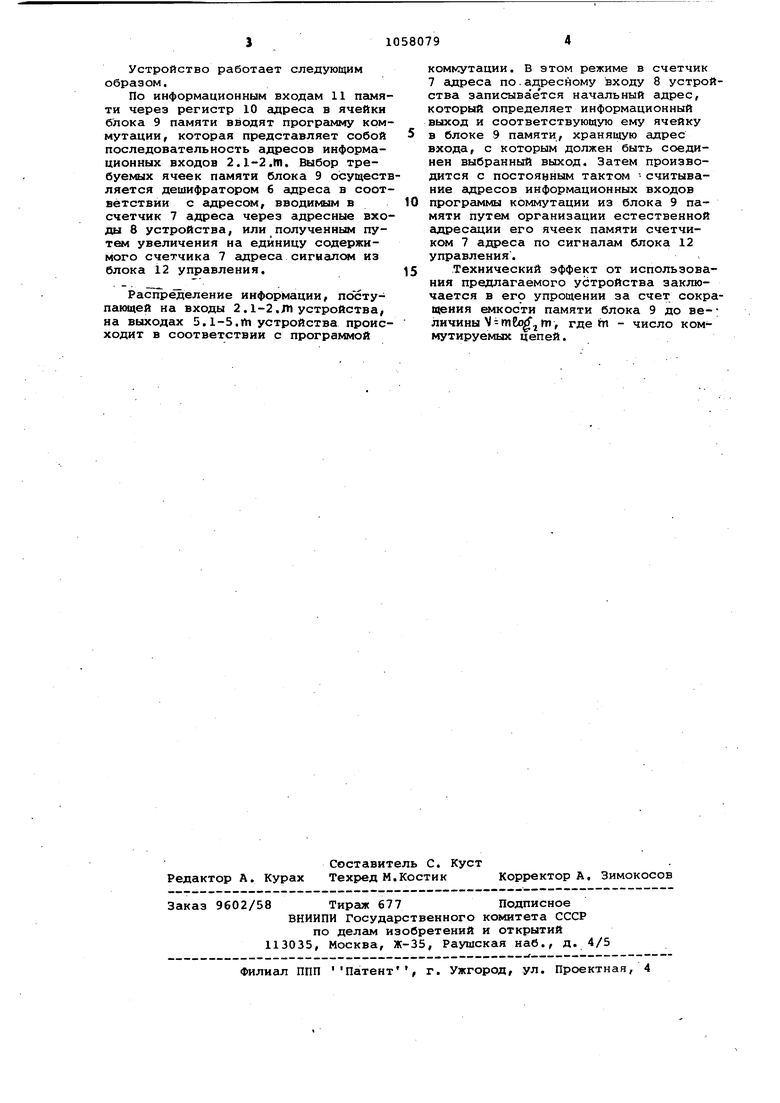

На чертеже представлена структурная схема синхронного адресно-временного устройства коммутации.

Устройство содержит блок 1 уплотнения, информационные входы которого подключены к информационным входам 2,1-2.т устройства, адресные входы - к выходам дешифратора 3 адреса входа, а информационный выход блока 1 уплотнения соединен с информационными входами расширителя 4, информационные выходы которого подключены к информационным выходам 5.1-5,m устройства, а адресные входы расширителя 4 - к выходам дешифратора ь адреса, входы которого соединены с выходами счетчика 7 адреса, подключённого входами к адресным входам 8 устройства, блок 9 памяти, адресные входы которого подключены к выходам дешифратора б адреса, а информационные входы и выходы - к первым информационным входаии и выходам регистра 10 сщреса, подключенного вторыми информационными входами к информационным входам 11 памяти, а . вторыми информационными выходами к входам дешифратора 3 адреса входа, блок 12 управления, вход и вькод которого соединены соответственно с управляюш,ими входом 13 и выходом 14 устройства, а управляющие выходы - с управляющими входами регистра 10 адреса и счетчика 7 адреса. Блок 1 уплотнения содержит логические элементы 15.1-15.m и элемент ИЛИ 16, а расширитель 4 - логические элементы 17.1-17.т. Счетчик 7 адреса и дешифратор 6 адреса образуют адресный блок 18.

Устройство работает следующим образом.

По информационным входам 11 памяти через регистр 10 адреса в ячейки блока 9 памяти вводят программу коммутации, которая представляет собой последовательность адресов информационных входов 2.1-2.1Л. Выбор требуемых ячеек памяти блока 9 осуществляется дешифратором 6 адреса в соответствии с адресом, вводимым в счетчик 7 адреса через адресные входы 8 устройства, или полученным путем увеличения на единицу содержимого счетчика 7 адреса сигнале из блока 12 управления.

Распределение информации, псйгтупакицей на входы 2 .1-2.m устройства, на выходах 5.1-5.rti устройства происходит в соответствии с программой

ком1 тации. В этом режиме в счетчик 7 адреса по.адресному входу 8 устройства записывается начальный адрес, который определяет информационный выход и соответствующую ему ячейку

в блоке 9 памяти, хранящую адрес входа, с которым должен быть соединен выбранный выход. Затем производится с постоянным тактом считывание адресов информационных входов

0 программы коммутации из блока 9 памяти путем организации естественной гщресации его ячеек памяти счетчиком 7 адреса по сигналам блока 12 управления.

5 Технический эффект от использования предлагаемого устройства заключается в его упрощении за счет сокращения емкости памяти блока 9 до ве- личины VimCtJ jт, где m - число коммутируемых цепей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU982085A1 |

| Коммутатор уплотненных каналов связи | 1982 |

|

SU1072263A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1108460A1 |

| Устройство коммутации | 1980 |

|

SU894866A1 |

| Устройство пространственно-временнойКОММуТАции | 1979 |

|

SU841114A1 |

| Адресно-временное устройство коммутации | 1980 |

|

SU926782A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Устройство для моделирования поглощающих цепей Маркова | 1989 |

|

SU1810888A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

CJJHXPOHHOE АДРЕСНО-ВРЕМЕННОЕ УСТРОЙСТВО КОММУТАЦИИ, содержащее блок уплотнения информационные входы которого подключены к информационным входам устройства, адресные входы - к выходам дешифратора адреса входа, а информационный выход блока уплотнения соединен с информационным входом расширителя, информационные выходы которого подклрочены к информационным выходам устройства, блок памяти, адресные входы которого соединены,с выходами дешифратора адреса, а информационные входы и выходы - с первыми информа- . ционными входами и выходами регистра адреса, вторые информационные; входы регистра адреса подключены к информационным входам /памяти, блок управления, входы и выходы которого соединены соответственно с управляющими входами и выходами устройства, а управляющие выходы - с управляющими входами регистра адреса и счетчика адреса, подключенного входами к |адресным входам устройства, а выходом - к дешифратору адреса, о т л иi чаю.щееся тем, что, с целью упрощения устройства, выходы дешиф(Л С ратора адреса соединены с с1дресными входами расширителя, а вторые информационные выходы регистра адреса подключены к входам дешифратора адреса входа. Сл 00 о ч1 со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство временной коммутации | 1975 |

|

SU563732A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для временнойКОММуТАции КАНАлОВ | 1979 |

|

SU794750A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-30—Публикация

1982-09-28—Подача