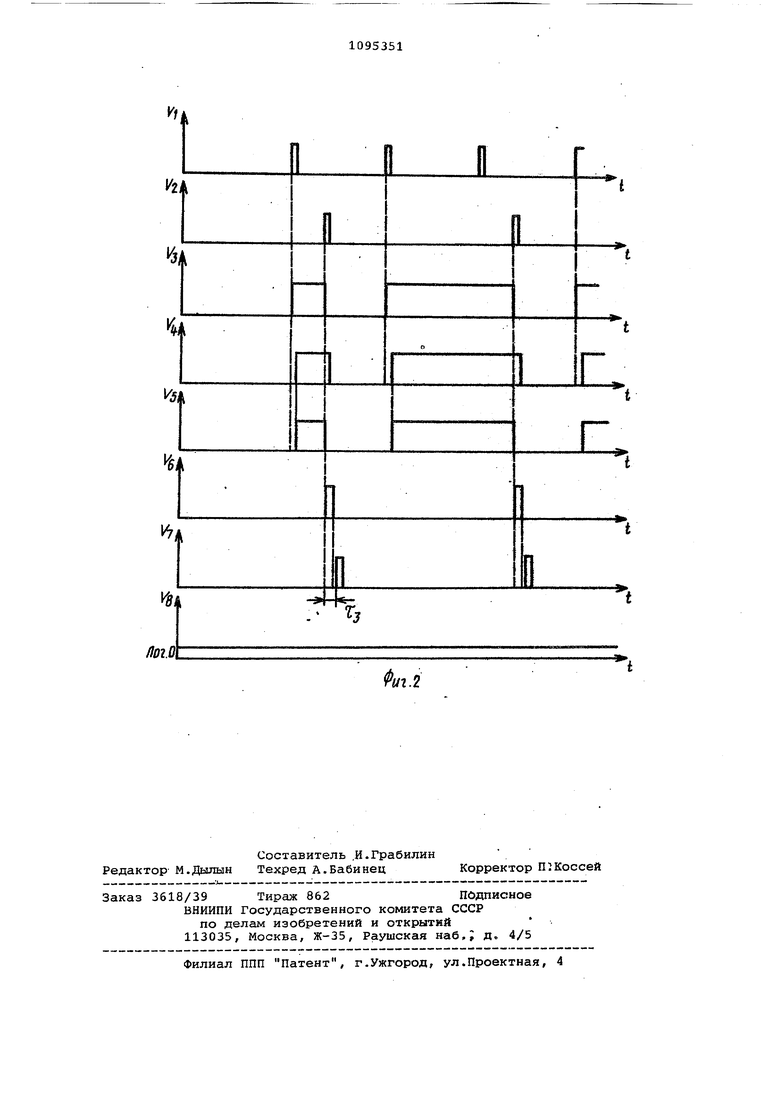

Изобретение относится к радиотехнике и может использоваться в радиопередающей , радиоприемной технике и синтезаторах частот. Известен частотно-фазовый детекто содержащий два триггера, предназначенных для каждого из двух сравнивае мых сигналов, имеются также цепи для установки триггеров в состояние логической единицы на время, пропорциональное разности частот и фаз сиг налов. Это напряжение логической еди ницы усиливается и фильтруется . Однако данный частотно-фазовый де тектор имеет недостаточное подавление помех на своем выходе, вызванных импульсными помехами на выходе первого и второго триггеров в зависимос ти от соотношения частот и фаз вхоя ных сигналов. Наиболее близким техническим реше нием к предложенному является частот но-фазовый детектор, содержащий дифференциальный усилитель, два D-триггера и элемент И-НЕ, входы которого соединены с прямыми выходами D -триг геров, в выход - с входами RD -триг геров, при этом D входы D -триггеров соединены с источником логической 1, входы синхронизации) -триг геров являются входами частотно-фазового детектора, а выход дифференциального усилителя является выходом частотно-фазового детектора 2 Однако известный частотно-фазовый детектор имеет также недостаточное подавление помех на выходе. Цель изобретения - уменьшение уровня помех в выходном сигнале во всех режимах работы. Цель достигается тем, что в .частотно-фазовый детектор, содержащий дифференциальный усилитель, два Dтриггера и элемент И-НЕ, входы которого соединены с прямыми выходами D триггеров, а выход - с входами RDтриггеров, при этом fl входы 1)-триггеров соединены с источником логической 1, входы синхронизации Dтриггеров являются входами частотнофазового детектора, а выход дифферен циального усилителя является выходом частотно-фазового детектора, введены два Элемента И и два блока задержки, причем прямые выходы каждого D -триг гера через соответствующий элемент И соединены с входами дифференциального усилителя, а второй вход каждого элемента И через соответствующий блок задержки соединен с инверсным выходом соответствующегоD -триггера. На фиг. 1 приведена структурная электрическая схема предложенного частотно-фазового детектора; на фиг. 2 - временные диаграммы его работы. Частотно-фазовый детектор содержит два) -триггера 1 и 2, элемент И-НЕ 3, дифференциальный усилитель 4, два элемента И 5 и 6, блоки 7 и 8 задержки, источник § логической 1. Частотно-фазовый детектор работает следующим образом. На входы синхронизацииО-триггеров 1 и 2 поступают соответственно первая и вторая импульсные последовательности, причем если частота ij следования первой импульсной последовательности больше частоты fj второй импульсной последовательности, тогда первый импульс частоты f перебросит Р-триггер 1 в единичное состояние, при этомD-триггер 1 становится нечувствительным к последующим импульсам частоты до прихода первого импульса частоты iv нар -триггер 2, который под воздействием этого импульса перебросится в единичное состояние. Далее в элементе И 6 осуществляется операция логичес1 ого умножения напряжения на выходе D -триггера 1 и выходе блока 8 задержки. После прихода первого импульса частоты i, на выходе D -триггера 2 появляется напряжение на время, определяемое временем задержки в D-триггере 2 и элементе И-НЕ 3, которое также поступает на схему логического умножения, состоящую из блока 7 задержки и элемента И 5 , но не проходит на ее выход, так как коэффициент передачи рхемы логического умножения равен нулю для задержек, меньших или равных сумме задержек в D -триггере 2 и , менте И-НЕ 3. Появление напряжения на прямом выходе D триггера 2 открывает схему сброса, принудительно устанавливающую D -триггеры 1 и 2 в исходное нулевое состояние. Таким образом, на выходе элемента И 6 образуется напряжение, пропорциональное разности частот и фаз сравниваемых сигналов, а на выходе элемента Л5 образуется напряжение логического нуля. Далее эти напряжения усили-j, ваются и фильтруются.в дифференциальном усилителе 4. Работа частотно-фазового детектора в случае f б 2аналогична случаю ii i-i с той лишь разницей, что напряжение, пропорциональное разнице частот и фаз, появляется на выходе элемента И5, а напряжение логического нуля на выходе элемента Иб, Таким образом, при, f 2 и,6 ig длительность импульса на.выходах соответственно элементов Иб и ИЗ равна(т+и1/, где п - целое число периодов частоты , укладывающихся в случае г12 на периоде частотьГ i , или число периодов частоты i укладывающихся на периоде частоты 1 в случае i fg и характеризует разность фаз сигналов. В случаеi.i-, . На фиг 4 2 приведены временные диа грамкш, поясняющие работу частотнофазового детектора при i, 1,. Здесь V и Vj - напряжения на входе первого и второго D -триггеров 1 и 2 соответственно; V- ,V и Vj - напряжения соответственно на прямом выходе Dтриггера 1, выходе блока 8 задержки и элементе H6;Yg,V7 Vg - напряжеНИН соответственно на прямом выходе В-триггера 2, выходе блока 7 задержки и элементе И 5. Напряжение помех на JBentofle частот но-фазового детектора относительно выхода D -триггера 2 при i г tg определяется соотношением для прототипа V rVn -К Vn.,(,,.B где УП, - амплитуда импульсной помехи на выходеР -триггера 2; Ко - коэффициент усиления дифференциального усилителя 4 на частоте СО 0; Е - выходное сопротивление дифференциального усилителя 4; RJ - сопротивление фильтра дифференциального усилителя 4; С - емкость фильтра дифференциального усилителя 4. При f 1 6 i2 напряжение помехи на выходе частотно-фазового делителя от D-триггера 1 определяется аналогично Для частотно-фазового детектора со схемой логической защиты напряжение помехи на выходе частотно-фазового детектора определяется соотношениемUp,C-5 RexCn-S V -V к . c.RgJ (где К, - коэффициент передачи схемы логической защиты, состоящей из блока задержки и элемента, И на выходе Dтриггеров 1 и 2; R - входное сопротивление дифференциального усилителя 4; Сц- паразитная емкость с выхода D -триггера на вход дифференциального усилителя 4. Поскольку длительность помехиVD равна 1 (ил где2г - задержка в Dтриггере ид - задержка в схеме сброса) , то К 0 при 111, L, 4(2 гдеtj задержка импульсов в блоке задерянси, тогда Vn 1 R Ом -уГ- 1+ё--ГТ С,2. п «ах-п МГц. Таким образом, использование предложенного устройства позволяет существенно уменьшить уровень помех на выходе частотно-фазового детектора. По сравнению с базовымобъектом в изобретении осуществляется дополнительная логическая обработка помех до выходного фильтра усилителя, что позволило снизить уровень помех на выходе частотно-фазового детектора примерно в 79 раз, не уменьшая полосы пропускания частотно-фазового де ктора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Устройство сравнения частот и фаз | 1983 |

|

SU1171971A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1285558A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР, содержаиций дифференциальный усилитель, дваD -триггера и элемент И-НЕ, входы которого соединены с прямыми выходами D -триггеров, а выход - с входами:RD -триггеров, при этом D входы D -триггеров соединены с источником логической 1, входы синхронизации D -триггеров являются входами частотно-фазового детектора, а выход дифференциального усилителя является выходом частотно-фазового детектора, отличающийся тем, что, с целью уменьшения уровня импульсных помех в выходном сигнале во всех режимах работы, введены два элемента И и два блока задержка, причем прямые выходы каждого 13 -триггера через соответствующий элемент И соединены с входами дифференциального усилителя, а второй вход каждого элемента И через соответствующий блок задержки соединены с инверсным выходом соответствующего Б -триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4277754, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3710140, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-30—Публикация

1982-07-05—Подача