Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты.

Цель изобретения - повьшение быстродействия в частотном режиме при одновременном упрощении.

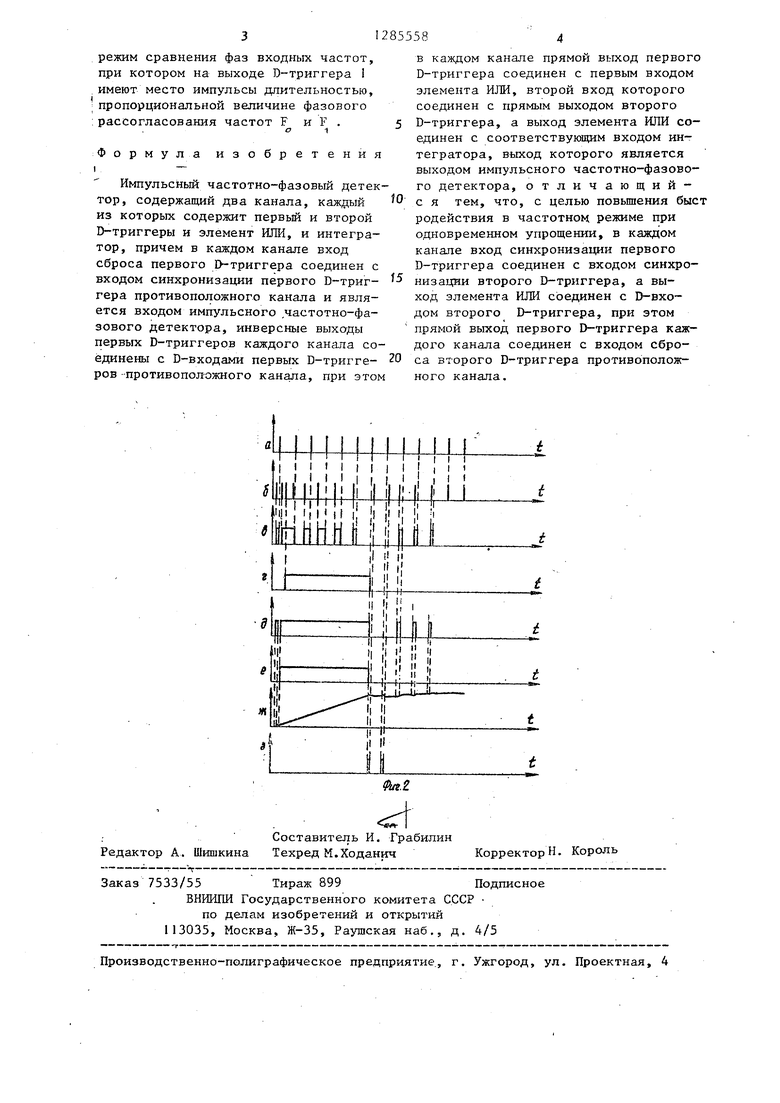

На фиг. I прив.едена структурная электрическая схема импульсного час- тотнотФазового детектора; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Импульсный частотно-фазовый детектор (ИЧФД) содержит два канала, каждый из которых состоит из первого и второго D-триггеров 1 (2) и 3 (4) и элемента ИЛИ 5 (6), интегратор 7.

Устройство работает следующим образом.

В исходном состоянии на прямых вы- ходах D-триггеров 1-4 уровни напряжений соответствуют логическому О. На шину 8 поступают короткие импульсы, например, опорной частоты F

(фиг. 2а), длительность которых опре- напряжением с выхода D-триггера 1 деляется быстродействием используе- 25 (фиг. 2 з). Таким образом D-трйггер4

мой элементной базы. На шину 9 поступают импульсы контролируемой F, (фиг. 26) частоты той же длительности. Поскольку в ИЧФД возможны режимы сравнения частот, когда F - F, , либо режим сравнения

F , но д М О или , где Alp- разность фаз между опорной и контролируемой частотами, то рассмотрим сначала режим частотного сравнения, когда, например,

или F

о 1

фаз, когда F

F F . В этом режиме на выходе В-триггера 2 появляются широтно-мо- дулированные импульсы (фиг. 2в), длительность которых пропорциональна разности фаз между частотами F и F поэтому через некоторое время, в худшем случае равное 1 / F - F , когда uf становится больше 2f, между импульсами частоты FJ появляются два импульса более высокой частоты. Первый импульс частоты F, в указанной ситуации переключает D-триггер 2 в

состояние логической 1, а второй импульс частоты F записывает логическую 1 из D-триггера 2 в D-триггер 4 (фиг. 2г). Каждым последующим импульсом частоты F состояние D, триггера 4 подтверждается, поскольку логическая 1 с прямого выхода D-триггера 4 через элемент ИЛИ 6 (фиг. 2д) поступает на ГНвход того же D-триггера. Таким образом, на выходе D-триггера 4 фиксируется посто

янный уровень логической 1, означающий .отрицательный знак частотной расстройки Fp- F 0, напряжение которой поступает на выходную шину 10

(фиг. 2 е) .,

Одновременно напряжение логической 1 с выхода элемента ИЖ 6 в виде постоянного уровня поступает на вход интегратора 7, при этом напряйкение на выходе интегратора 7

(фиг. 2 ж.), увеличивается с максимальной скоростью, уменьшая тем самым частотную расстройку на входах ИЧФД до момента изменения знака разности фаз частот F и F . После изменения знака разности фаз частот Fg и F импульсы частоты F. начинают опережать по фазе импульсы частоты F , в результате первый же опережаюЩий импульс частоты F переключает

О

ГЬ-триггер 1 в единичное состояние (фиг. 2 з), а D-триггер 4 по входу сброса сбрасывается в О (фиг. 2 г)

0

0

при А ч г 2,7 отключается и на выход- ных щинах 10 и 11 фиксируются уровни логич-еского О, означающие режим фазового сравнения входных частот. В этом режиме на выходе элемента ШШ 6 наблюдаются импульсы длительностью, пропорциональной фазовому рассогласованию входных частот F и F (фиг. 2 д). На выходе интегратора 7 5 происходит увеличение напряжения, пропорциональное длительности им-- . пульсов, поступающих на вход интегратора 7, уменьшающее рассогласование фаз входных частот. При нулевом сдвиге фаз между напряжениями входных сигналов на выходах элементов ИЛИ 5 и 6 импульсы отсутствуют, удерживая интегратор 7 в закрытом состоянии.

В силу симметричности схемы ИЧФД его работа в случае F F аналогична работе при F F , с той лишь разницей, что в состояние логической 1 переключается D-триггер 3, напряжение с которого через элемент ИЛИ 5 воздействует на интегратор 7, уменьшая напряжение на его выходе с максимальной скоростью до момента изменения знака фазового рассогласова 1ия,, при этом D-триггер 3 сбрасывается в нулевое, после переключения D-триггера 2 - в единичное состояние первым же импульсом частоты F после указанной ситуации. Далее наступает

режим сравнения фаз входных частот, при котором на выходе D-триггера 1 имеют место импульсы длительностью, пропорциональной величине фазового :рассогласования частот F и F .

Формула изобретения I

Импульсный частотно-фазовый детектор, содержапщй два канала, каждый из которых содержит первьй и второй D-триггеры и элемент ШШ, и интегратор, причем в каждом канале вход сброса первого D-триггера соединен с входом синхронизации первого D-триггера противоположного канала и является входом импульсного .частотно-фазового детектора, инверсные выходы первых D-триггеров каждого канала сов каждом канале прямой выход первого D-триггера соединен с первым входом элемента ИЛИ, второй вход которого соединен с прямым выходом второго D-триггера, а выход элемента ИЛИ соединен с соответствующим входом интегратора, выход которого является выходом импульсного частотно-фазового детектора, отличающийШ с я тем, что, с целью повьппения быс родействия в частотном режиме при одновременном упрощении, в каждом канапе вход синхронизации первого В-триггера соединен с входом синхро низацни второго D-триггера, а выход элемента ИЛИ соединен с D-BXO дом второго D-триггера, при этом прямой выход первого D-триггера каждого канала соединен с входом сброёдинены с D-входами первых D-тригге- 0 са второго D-триггера противоположров -противоположного канала, при этом

Заказ 7533/55 Тираж 899Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-33, Раушская наб,, д. 4/3

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

в каждом канале прямой выход первого D-триггера соединен с первым входом элемента ИЛИ, второй вход которого соединен с прямым выходом второго D-триггера, а выход элемента ИЛИ соединен с соответствующим входом интегратора, выход которого является выходом импульсного частотно-фазового детектора, отличающийс я тем, что, с целью повьппения быст родействия в частотном режиме при одновременном упрощении, в каждом канапе вход синхронизации первого В-триггера соединен с входом синхронизацни второго D-триггера, а выход элемента ИЛИ соединен с D-BXO дом второго D-триггера, при этом прямой выход первого D-триггера каждого канала соединен с входом сброного канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Устройство сравнения частот и фаз | 1983 |

|

SU1171971A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

Изобретение относится к радиотехнике и может использоваться в системах фазовой автоподстройки частоты. Цель изобретения - повышение быстродействия в частотном режиме при одновременном упрощении. 1Ь1пульс- ный частотно-фазовьй детектор содержит два канала, каждый из которых состоит из D-триггеров 1 (2), 3 (4) и элемента ИЛИ 5 (6), и интегратор 7. Импульсы опорной частоты (04) Т по- ступают по шине 8, а импульсы контролируемой частоты (КЧ) F - по шине 9. В случае, когда F F , на выходе D-триггера 2 появляются широтно-моду- лированные импульсы. Если разность фаз мелсду 04 и КЧ превысит 23г, между импульсами КЧ появятся два импульса более высокой частоты. Первым из них D-триггер 2 установится в состояние 1, а вторым из D-триггера 2 1 запишется в D-триггер 4. Каждый-последующий импульс КЧ подтверждает состояние 1 D-триггера 4, что означает отриц. знак частотной расстройки. Напряжение на выходе интегратора 7.растет, уменьшая тем самым частотную расстройку до момента изменения зна- . ка разности фаз. 2 ил. J ю 00 О1 ел ел 00

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Частотный дискриминатор | 1983 |

|

SU1124423A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1983-12-23—Подача