1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Целью изобретения является повышение надежности устройства.

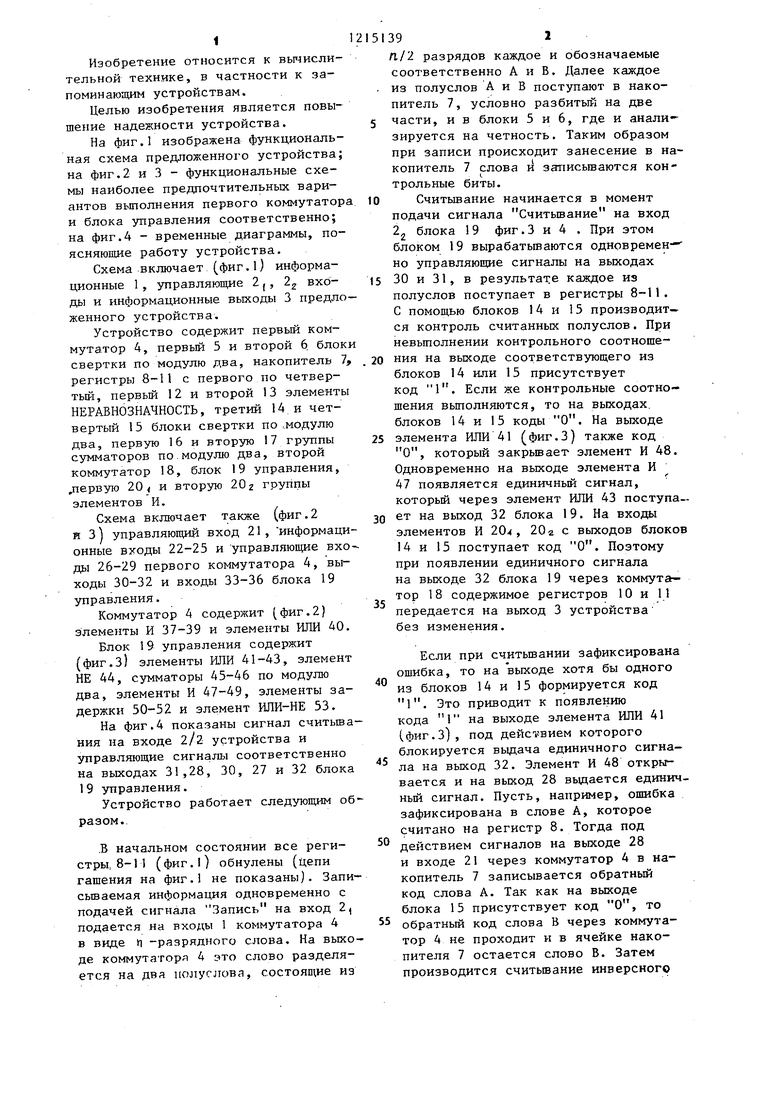

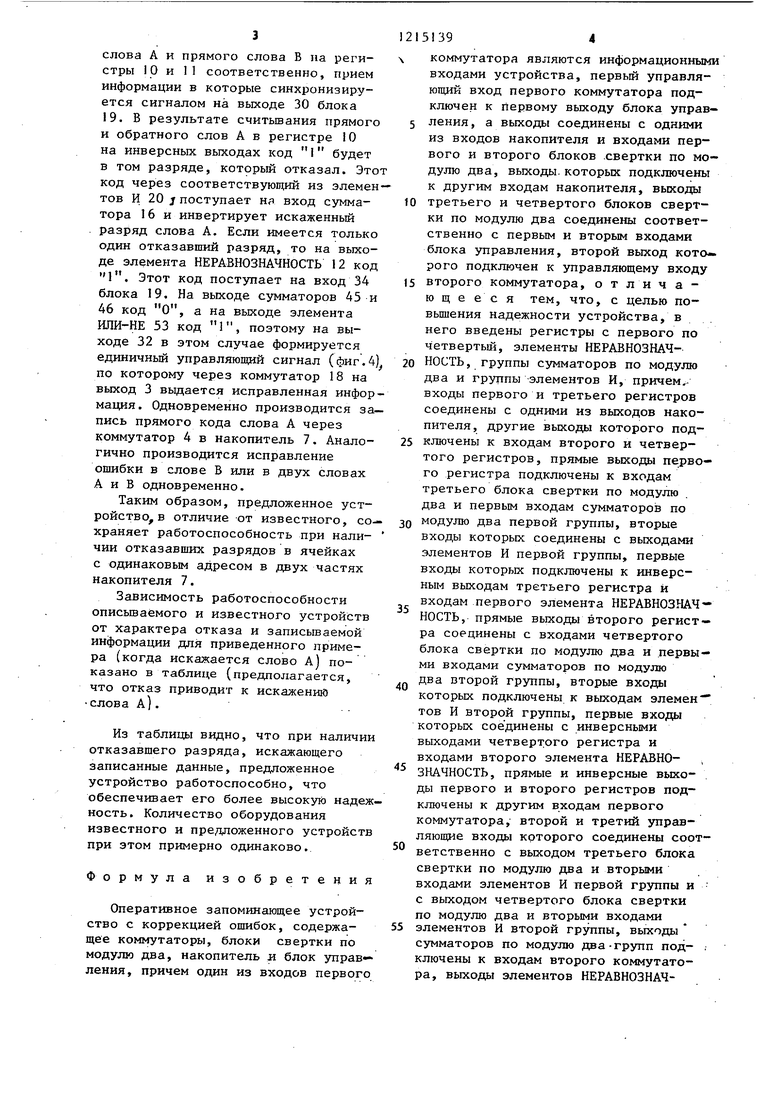

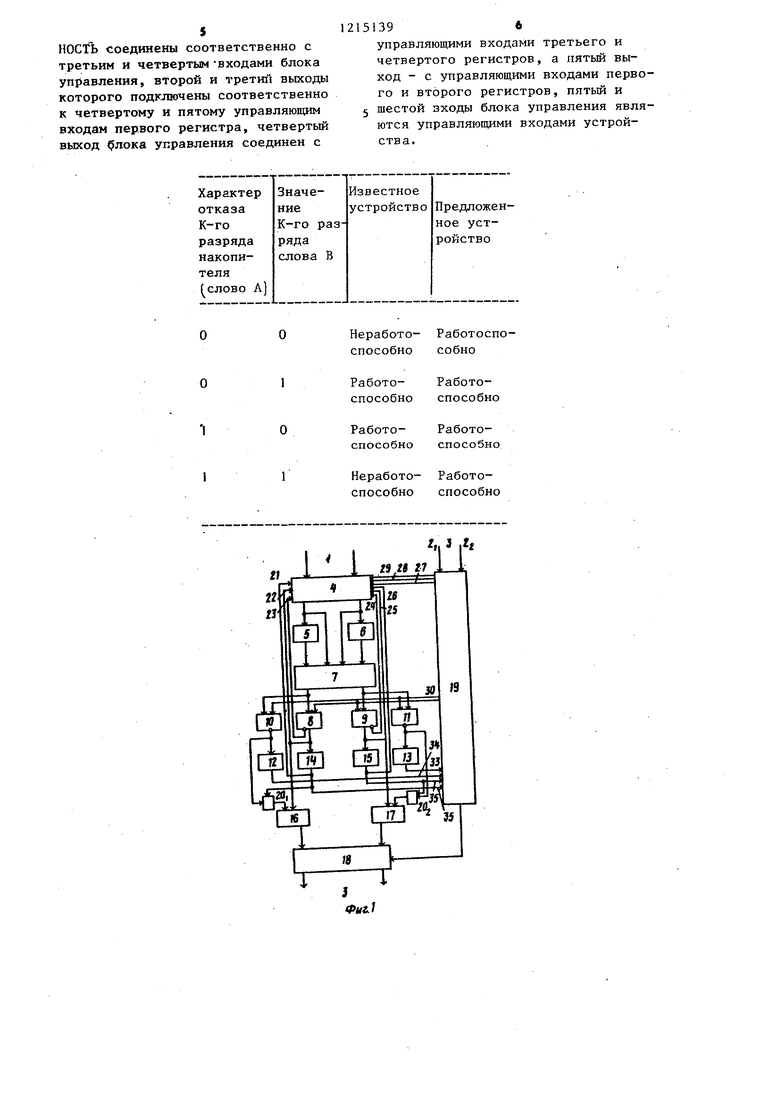

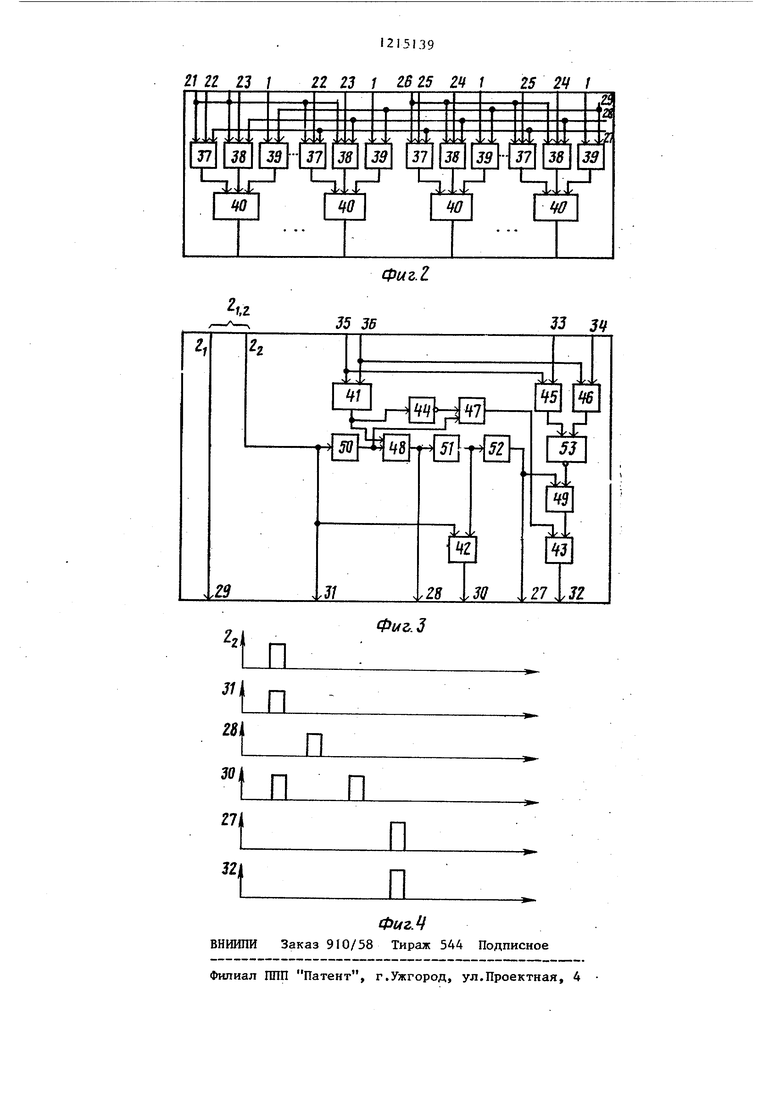

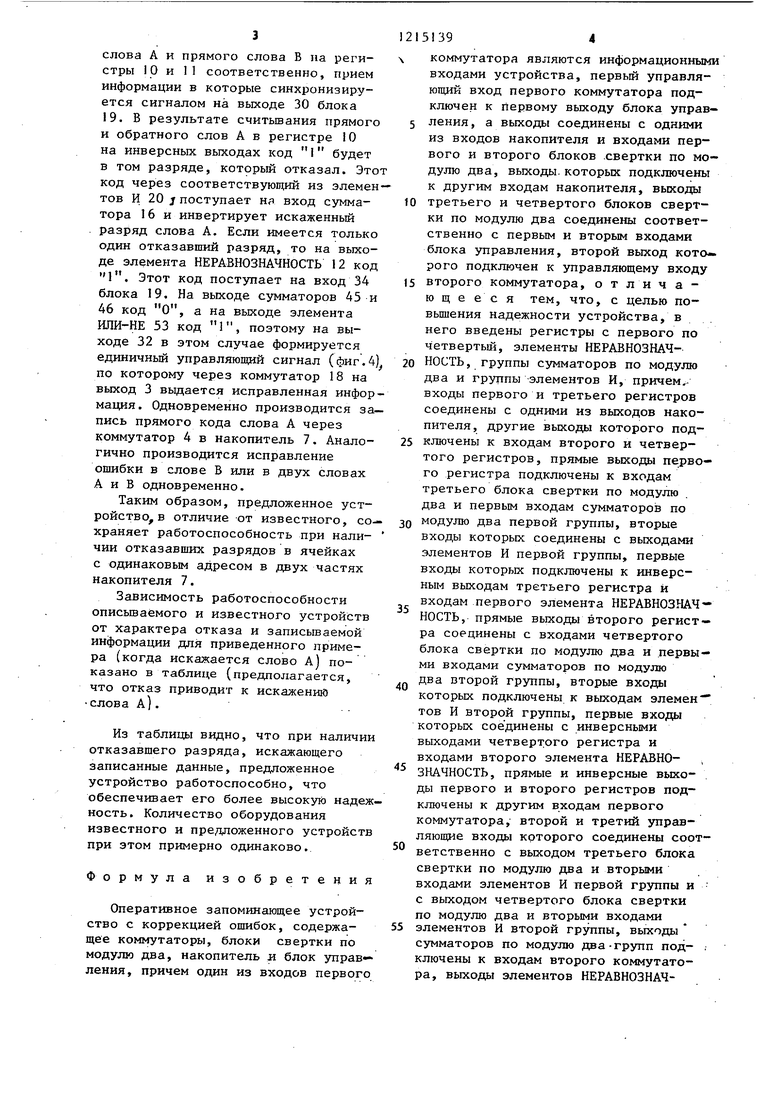

На фиг.1 изображена функциональная схема предложенного устройства; на фиг.2 и 3 - функциональные схемы наиболее предпочтительных вариантов выполнения первого коммутатора и блока управления соответственно; на фиг.4 - временные диаграммы, поясняющие работу устройства.

Схема включает (фиг.1) информационные 1, управляюпще 2 , 2 входы и информационные выходы 3 предложенного устройства.

Устройство содержит первый коммутатор 4, первый 5 и второй 6 блоки свертки по модулю два, накопитель 7 регистры 8-11 с первого по четвер- тьй, первьш 12 и второй 13 элементы НЕРАВНОЗНАЧНОСТЬ, третий 14 и четвертый 15 блоки свертки по ..модулю два, первую 16 и вторую 17 группы сумматоров по.модулю два, второй коммутатор 18, блок 19 управления, дтервую 204 и вторую 20 z группы элементов И.

Схема включает также (фиг.2 н 3 управляющий вход 21, информационные входы 22-25 и управляющие входы 26-29 первого коммутатора 4, выходы 30-32 и входы 33-36 блока 19 управления.

Коммутатор 4 содержит (фиг.2) элементы И 37-39 и элементы ИЛИ 40.

Блок 19 управления содержит (фиг.З) элементы ИЛИ , элемент НЕ 44, сумматоры 45-46 по модулю два, элементы И 47-49, элементы задержки 50-52 и элемент ИЛИ-НЕ 53.

На фиг.4 показаны сигнал считьша- ния на входе 2/2 ус-тройства и управляющие сигналы соответственно на выходах 31,28, 30, 27 и 32 блока 19 управления.

Устройство работает следующим об разом.

.В начальном состоянии все регистры, 8-1 1 (фиг.1) обнулены (цепи гашения на фиг.1 не показаны). Запи- сьтаемая информация одновременно с подачей сигнала Запись на вход 2, подается на входы 1 коммутатора 4 в виде II -разрядного слова. На выходе коммутаторя 4 это слово разделяется на два полуслова, состоящие из

2I5I392

А1/2 разрядов каждое и обозначаемые соответственно А и В. Далее каждое . из полуслов А и В поступают в накопитель 7, условно разбитый на две

5 части, и в блоки 5 и 6, где и анализируется на четность. Таким образом при записи происходит занесение в накопитель 7 слова и затшсьгоаются контрольные биты.

10 Считывание начинается в момент подачи сигнала Считьшание на вход 2 блока 19 фиг.3 и 4 . При этом блоком 19 вырабатьгоаются одновремен- но управляющие сигналы на выходах

15 30 и 31, в результате каждое из полуслов поступает в регистры 8-11. С помощью блоков 14 и 15 производит- ся контроль считанных полуслов. При невьтолнении контрольного соотноще20 ния на выходе соответствующего из блоков 14 или 15 присутствует код 1. Если же контрольные соотношения вьтолняются, то на выходах, блоков 14 и 15 коды О. На выходе

25 элемента ИЛИ 41 (фиг.З) также код О, который закрьшает элемент И 48. Одновременно на выходе элемента И 47 появляется единичный сигнал, который через элемент ИЛИ 43 поступа-

30 ет на выход 32 блока 19. На входы элементов И 20 , 20г с выходов блоков 14 и 15 поступает код О. Поэтому при появлении единичного сигнала на выходе 32 блока 19 через коммутатор 18 содержимое регистров 10 и 11 передается на выход 3 устройства без изменения.

35

Если при считьшании зафиксирована ошибка, то на выходе хотя бы одного из блоков 14 и 15 формируется код 1. Это приводит к появлению кода 1 на выходе элемента ИЛИ 41 (фиг.З), под действием которого блокируется выдача единичного сигнала на выход 32. Элемент И 48 открывается и на выход 28 выдается единичный сигнал. Пусть, например, ошибка зафиксирована в слове А, которое считано на регистр 8. Тогда под

действием сигналов на выходе 28

и входе 21 через коммутатор 4 в накопитель 7 записывается обратньш код слова А. Так как на выходе блока 15 присутствует код О, то

обратный код слова Б через коммутатор 4 не проходит и в ячейке накопителя 7 остается слово В. Затем производится считьшание инверсного

слова А и прямого слова В на регистры 10 и 11 соответственно, прием информации в которые синхронизируется сигналом на выходе 30 блока 19. В результате считьшания прямого и обратного слов А в регистре 10 на инверсных выходах код I будет в том разряде, который отказал. Это код через соответствующий из элементов И 20 J поступает на вход сумматора 16 и инвертирует искаженньй разряд слова А. Если имеется только один отказавший разряд, то на выходе элемента НЕРАВНОЗНАЧНОСТЬ 12 код 1. Этот код поступает на вход 34 блока 19. На выходе сумматоров 45 и 46 код О, а на выходе элемента ИЛИ-НЕ 53 код 1, поэтому на выходе 32 в этом случае формируется единичный управляющий сигнал (фиг.4) по которому через коммутатор 18 на выход 3 вьщается исправленная информация. Одновременно производится запись прямого кода слова А через коммутатор 4 в накопитель 7. Аналогично производится исправление ошибки в слове В или в двух словах А и В одновременно.

Таким образом, предложенное устройство, в отличие -от известного, сохраняет работоспособность при нали- чии отказавших разрядов в ячейках с одинаковым адресом в двух частях накопителя 7.

Зависимость работоспособности описьшаемого и известного устройств от характера отказа и записываемой информации для приведенного примера (когда искажается слово А) показано в таблице (предполагается, что отказ приводит к искажений слова А.

Из таблицы видно, что при наличии отказавшего разряда, искажающего записанные данные, предложенное устройство работоспособно, что обеспечивает его более высокую надежность. Количество оборудования известного и предложенного устройств при этом примерно одинаково.

Формула изобретения

Оперативное запоминающее устройство с коррекцией ошибок, содержащее коммутаторы, блоки свертки по модулю два, накопитель и блок управ«- ления, причем один из входов первого

2151394

коммутатора являются информационными входами устройства, первый управляющий вход первого коммутатора подключен к первому выходу блока управ- 5 ления, а выходы соединены с одними из входов накопителя и входами первого и второго блоков .свертки по модулю два, выходы, которых подключены к другим входам накопителя, выходы

10 третьего и четвертого блоков свертки по модулю два соединены соответственно с первым и вторым входами блока управления, второй выход которого подключен к управляющему входу

15 второго коммутатора, отличающееся тем, что, с целью по- вьшения надежности устройства, в . него введены регистры с первого по четвертьш, элементы НЕРАВНОЗНАЧ20 НОСТЬ, группы сумматоров по модулю два и группы элементов И, причем,, входы первого и третьего регистров соединены с одними из выходов накопителя, другие выходы которого под-

25 ключены к входам второго и четвертого регистров, прямые выхода1 первого регистра подключены к входам третьего блока свертки по модулю два и первым входам сумматоров по

3Q модулю два первой группы, вторые входы которых соединены с выходами элементов И первой группы, первые входы которых подключены к инверсным выходам третьего регистра и входам первого элемента НЕРАВНОЗНАЧ- НОСТЬ, прямые выходы второго регистра соединены с входами четвертого блока свертки по модулю два и первыми входами сумматоров по модулю два второй группы, вторые входы которых подключены к выходам элемен тов И второй группы, первые входы которых соединены с инверсными выходами четвертого регистра и входами второго элемента НЕРАВНО ЗНАЧНОСТЬ, прямые и инверсные выхо- . ды первого и второго регистров подключены к другим входам первого коммутатора, второй и третий управляющие входы которого соединены соот ветственно с выходом третьего блока свертки по модулю два и вторыми входами элементов И первой группы и с выходом четвертого блока свертки по модулю два и вторыми входами

5 элементов И второй группы, выходы сумматоров по модулю два-групп под- ; ключены к входам второго коммутатора, выходы элементов НЕРАВНОЗНАЧ35

0

НОСТЪ соединены соответственно с третьим и четвертым -входами блока управления, второй и третий выходы которого подключены соответственно к четвертому и пятому управляющим входам первого регистра, четвертый вьгход лока управления соединен с

12151396

управляющими входами третьего и четвертого регистров, а пятый выход - с управляющими входами первого и второго регистров, пятый и 5 шестой зходы блока управления являются управляющими входами устройства.

f / 2Z 23 1 22 23 1 26 25 24 1 25 24 1

I

® Н й Ш @

i/ X X-sl 4 sy

Фиг2

JJ J

П

Ln

2«|

Д

30

271

J2J

.

ВНИШШ Заказ 910/58 Тираж 544 Подписное

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

Фиг..З

Д

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с коррекцией ошибок | 1991 |

|

SU1837364A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1113790A1 |

| Устройство для преобразованиядВОичНОгО КОдА B избыТОчНыйциКличЕСКий КОд | 1978 |

|

SU798797A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1061175A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, предназначенным для использования в системах контроля, управления и т.п. Цель изобретения - повьшение надежности устройства. Устройство содержит накопитель, блоки свертки по модулю два, регистры, группы сумматоров по модулю два, коммутаторы. При записи информации слово, подаваемое на коммутатор, разделяется на два полуслова, для каждого из которых формируется рйзряд четности в блоках свертки по модулю два и вместе с которыми они записываются в накопитель. При считьшании информации происходит коррекция двукратной ошибки при условии, что ошибки находятся в разных полусловах. Коррекция осуществляется при помощи блоков и сумматоров по модулю два. 4 ил.1 табл. § (Л С

| Патент США № 3685015, | |||

| кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Авторское свидетельство СССР . | |||

| кл | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1986-02-28—Публикация

1984-09-11—Подача