Изобретение относится к вычислительной технике и автоматике и может быть использовано для счета импульсов.

Известен счетчик, содержащий в каждом разряде пять элементов И и два триггера с соответствующими связями ti 3.

Недостатками известного устройства являются низкая удельная информационная емкость и сложность реализации.

Наиболее близким к изобретению по технической сущности является счетчик, содержащий в каждом разряде два триггера памяти, выполненные на четырех элементах И-ИЛИ-НЕ, причем выход первого элемента И-ИЛИ-НЕ соединен с входом первой группы И второго элемента И-ИЛИ-НЕ, выход которого соединен с входом первой группы И первого элемента И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ соединен с входом второй группы И четвертого элемента И-ИЛЙ-НЕ, выход которого, соединен с входом первой группы И третьего элемента И-ИЛИ-НЕ, вход первого разряда соединен с входом счетчика С23

Недостатком известного счетчика является большое число применяемых элементов, которое приводит к увеличению потребляемой мощности, а также генерации помех в цепи питания переключающимися элементс1МИ и к снижению удельной инфорйационной емкости счетчика (бит/элемеит /.

Цель изобретения - уменьшение потребляемой мощности, уменьшение генерации помех в цепи питания переключающимися элементами И-ИЛИ-НЕ и увеличение удельной информационной емкости счетчика.

Поставленная цель достигается тем, что в счетчик, содержги11ий в каждом разряде два триггера памяти, выполненные на четырех элементах И-ИЛИ НЕ, выход первого элемента И-ИЛИ-НЕ соединен с входом первой группы И второго элемента И-ИЛИ-НЬ, выход которо соединен с входом первой группы И первого элемента И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НБ соединен с входом первой группы И четвертого элемента И-ИЛИЧ1Е, выход которого соединен с входом первой группы И третьего элемента И-ИЛИ-НЕ, вход первого разряда соединен с входом счетчика, в каждый разряд введен двоичный коммутационный триггер, выполненный на пятом и шестом Элементах И-ИЛИ-ilE, выход первого элемента И-ИЛИ-НЕ. соединен с первым входом второй группы И четвертого и с первым входом первой группы ;й пятого и шестого элементов И-ИЛИгНЕ, выход

второго элемента И-ИЛИ-НЕ соединен с первым входом второй группы И третьего элемента И-ИЛИ-НЕ и с первыми входами вторых групп И пятого и шестого элементов И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ соединен с первым входом второй группы И первого элемента И-ИЛИ-НЕ, с вторым входом первой группы И пятого элемента И-ИЛИ-НЕ и с вторым

входом второй группы И шестого эле.мента И-ИЛИ-НЕ, выход четвертого элемента И-ИЛИ-НЕ соединен с первым входом второй группы И второго элемента Ч-ИЛИ-НЕ, с вторым входом

второй группы И пятого элемента И-ИЛИ-НЕ, с вторым входом первой группы И шестого элемента И-ИЛИ-НЕ и с входом последующего разряда, выход пятого элемента И-ИЛИ-НЕ соединен с вторыми входами вторых групп И третьего и четвертого элементов И-ИЛИ-НЕ и с третьими входами первой и второй групп И и с первым входом третьей группы И шестого элемента И-ИЛИ-НЕ, выход которого соеданен с вторыми входами вторых групп И первого и второго элементов И-ИЛИ-НЕ и с третьим входами первой и второй групп И и с первым входом

третьей группы И пятого элемента

И-ИЛИ-НЕ, а с третьими входами вторых группИ первого, второго, третьего и четвертого элементов И-ИЛИ-НЕ и с вторыми входами третьих групп И пятого и шестого элементов

И-ИЛИ-НЕ соединен вход разряда.

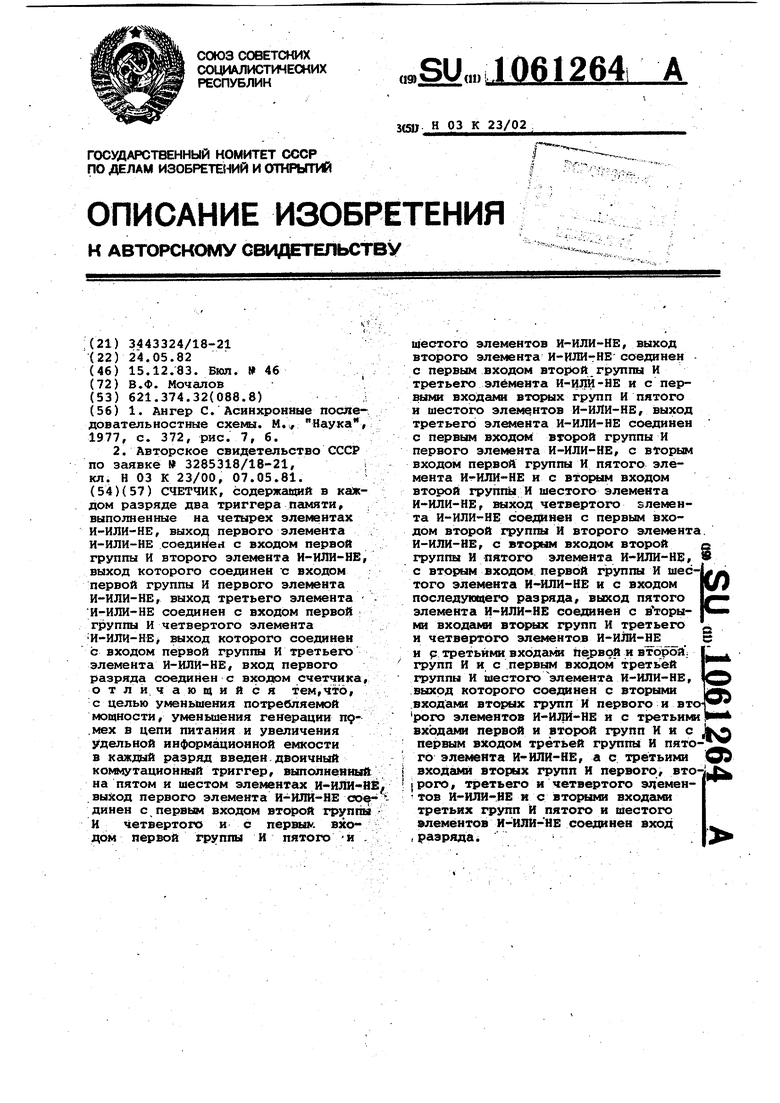

На чертеже представлена схема счетчика.

Устройство содержит разряды 1, в каждом из которых элементы И-ИЛИ-НЕ

2-5 попарно образуют первый и второй тригдеры памяти, а элементы И-ИЛИ-НЕ 6-7 - коммутационный триггер, соответственно первую, вторую и третью группы И 8,9 и 10 элементов И-ИЛИ-НЕ, вход Ц разряда. Рассмотрим работу счетчика на примере работы одного из его раз- . рядов 1.

В исходном состоянии при наличии логического О на входе 11 на выходах элементов 2, 4 и 6 присутствует логический О, а на выходах элементов 3, 5 и 7 - логическая 1. Поэтому при поступлении на

вход 11 сигнала, равного логической 1, на выходе элемента 3 поя§ляёт-. ся логический О, а на выходе элемента 2 - логическая 1. В паузе послепервого входного импульса на

входе 11 присутствует логический О, на выходе элемента б появляется логическая 1, а «а выходе элемента 7 - логический О. С приходом на вход 11 второго входного

импульса на выходе элемента 5 появляется логический О, а иа выхог |де элемента 4 - логическая 1 . В паузе после второго импульса на выходе элемента 7 появляется логическая 1, а на выходе элемента 6iлогический О. Третий входной импульс вызывает появление на выходе элемента 2 логического.О, а %а выходе элемента 3 - логической 1. После окончания действия третьго входного импульса на выходе элемента 6 появляется логическая 1, а на выходе элемента 7 - логический О. С приходом четвертого входного импульса на выходе элемен та 4 появляется логический О, а на выходе элемента 5 - логическая

1. В паузе после четвертого входйого импульса схема устанавливается в исходное состояние. Таким образом каждый из разрядов счетчика имеет четыре устойчивых состояния, а между разрядами организован последовательный перенос.

ТехникЬ-экономическим эффектом , изобретения является уменьшейие числа элементов И-ИЛИ-НЕ на ( .xfsJ/ 7N 100% 14,3%} уменьшение потребляемой мощности примерног на 10%, увеличение удельной информационной емкости на величину, равну

,,|/7()/7N«f7o o.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации булевых функций | 1986 |

|

SU1310801A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для магнитной записи-воспроизведения речевых сигналов | 1990 |

|

SU1739384A1 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Логический пробник | 1986 |

|

SU1386946A1 |

| Устройство для сбора и передачи информации | 1984 |

|

SU1221675A1 |

СЧЕТЧИК, содержащий в каждом разряде два триггера памяти, выполненные на четырех элементах И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с входом первой группы И второго элемента И-ИЛИ-НЕ, выход которого соединен -с входом первой группы И первого элемента И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ соединен с входом первой ; группы И четвертого элемента И-ИЛИ-НЕ выход которого соединен с входом первой группы И третьего элемента И-ИЛИ-НЕ, вход первого разряда соединен с входом счетчика, о т л и ч а ю щ и И с я тем,что, с целью уменьшения потре«5ляемой мощности, уменьшения генерации пф.мех в цепи питания и увеличения Сдельной информгщионной емкости в каждый разряд введен,двоичный коммутацноянаК триггер, выполненный на пятом и шестом элементеис И-ИЛМ- Й, выХод первого элемента И-ИЛИ-НЕ со динен с первым входом второй групга И четвертого и с первым входом первой группы И пятого И ., шестого элементов И-ИЛИ-НЕ, выход второго элемента И-илИгНЕ соединен с первым входом второй группы И третьего элемента И-ИЛИ-НЕ и с первыми входами вторых групп И пятого и шестого элементов И-ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ соединен с первым входом второй группы И первого элемента И-ИЛИ-НЕ, с вторым ВХОД014 первой группы И пятого элемента Иг-или-НЕ и с вторым входом второй группы И шестого элемента И-ИЛИ-НЕ, выход четвертого элемента И-ИЛИ-НЕ соединен с первым входом второй группы И второго элемента. И-ИЛИ-НЕ, с вторым входом второй е группы и пятого элемента И-ШЮ-НЕ, с вторым входом первой группы И шестого элемента И-ИЛИ-НЕ и с входом последующего разряда, выход пятого 1 элемента И-ИЛИ-НЕ соединен с в торы- ми входам1 вто{Я 1х групп И третьего L и четвертого элементов И-ИЛИ-НЕ с и я третьими входами и второй; групп И и с первьп) входомггретьёй группы И шестого элемента И-ИЛИ-НЕ, вьаод которого соединен с вторыми О) .входами вторых групп И первого и второго элементов И-ИЛИ-НЕ и с третьики входами первой и второй групп Икс J| первым входом третьей группы И пято- го элемекга И ИЛИ-НЕ, а с третьими Од входами вторых групп И первого, вто-Js j рого, третьего и четвертого элементов И-ИЛИ-НЕ НС вторыми входами третьих групп И пятого и шестого элементов И-ИЛИ-НЕ соединен вход ,раэряда.

//

LJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| АН rep С | |||

| Асинхронные последовательностные схемш | |||

| М., Наука, 1977, с | |||

| Электромагнитный счетчик электрических замыканий | 1921 |

|

SU372A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3285318/18-21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-15—Публикация

1982-05-24—Подача