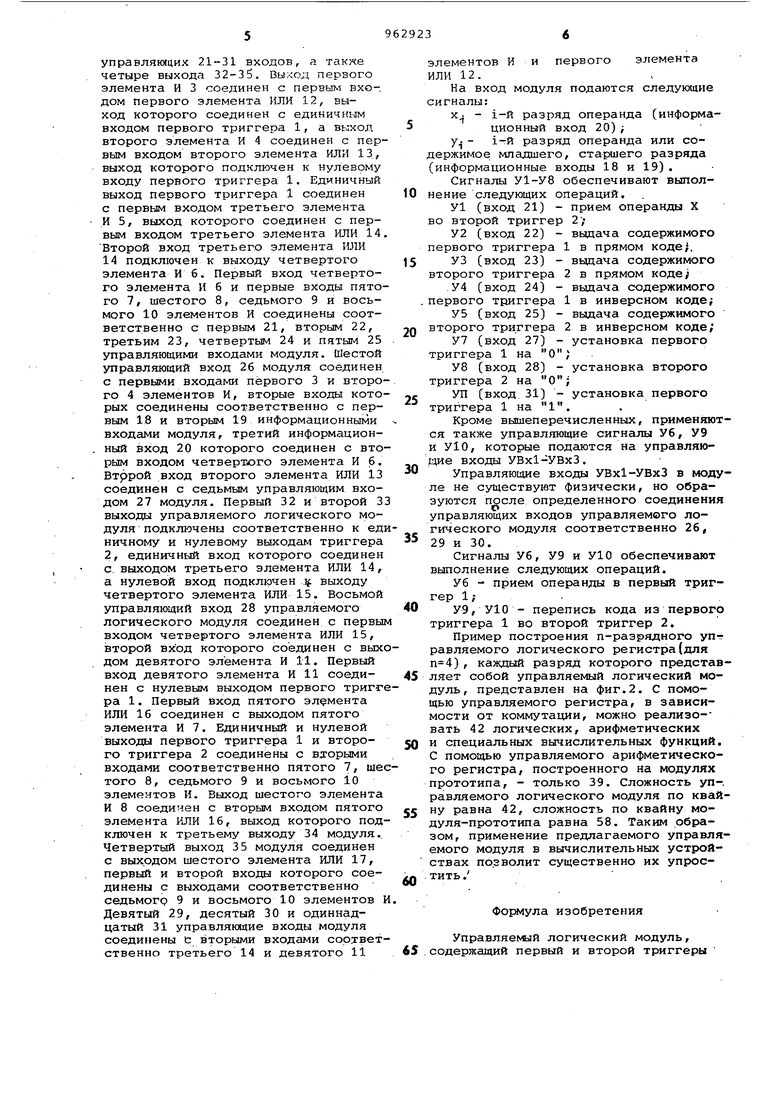

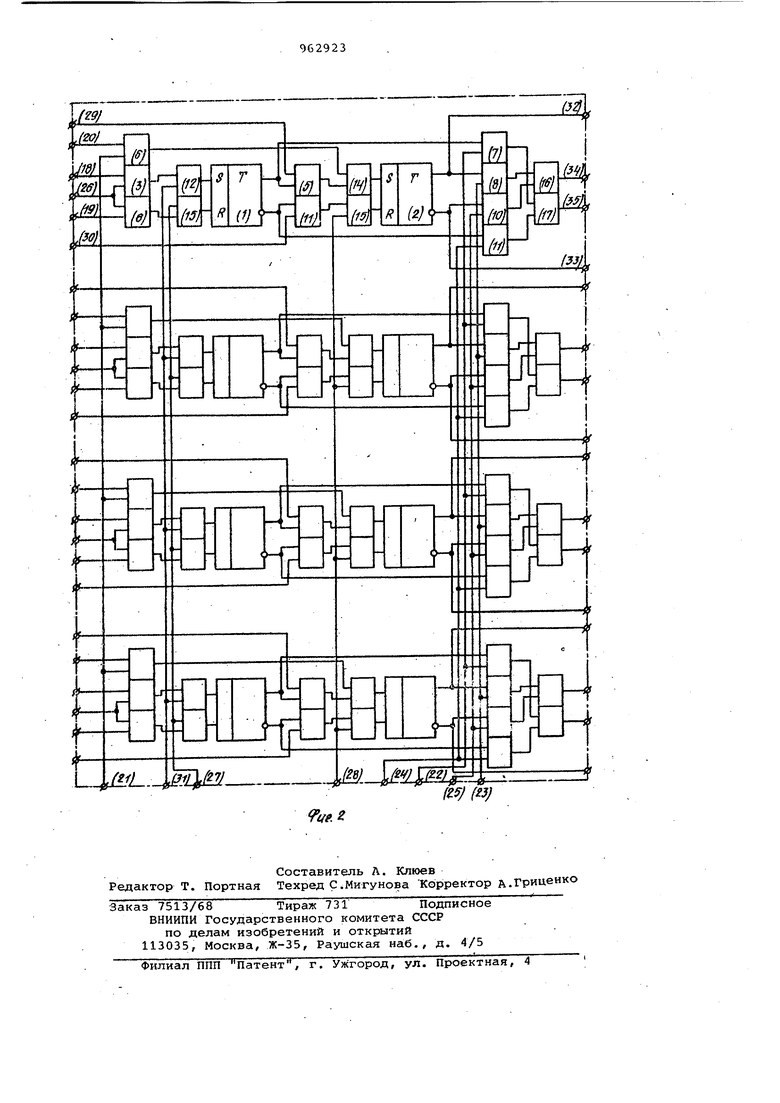

Изобретение относится к вычислительной технике и предназначено для реализации узлов и устройств цифровых вычислительных машин методами интегральной технологии со средним и большим уровнями интеграции. Известен управляемый арифметический модуль, содержащий триггер, логические элементы И, ИЛИ и. НЕ 1. Недостатком известного модуля являются ограниченные функциональные возможности, поэтому его использование для реализации нерегулярных устройств цифровой вычислительной машины, например, устройства управления нецелесообразно. Кроме того, вследст вне применения IК триггеров, высока сложность модуля. Наиболее близким техническим решением к предлагаемому является управляемый арифметический модуль, содержащий первый и второй триггеры, четырнадцать элементов И, шесть элементов ИЛИ, причем выход первого эле мента И соединен с первым входом пер вого элемента ИЛИ, выход которого со единен с единичным входом первого триггера, а выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к нулевому .входу первого-триггера, единичный выход которого соединен с первым входом третьего элемента И,-выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, первый вход которого и первые входы пятого, шестого, седьмого и восьмого элементов И соединены, соответственно, с первым, вторым, третьим, четвертым и пятым управляющими входами управляемого арифметического модуля, шестой управляющий вход которого соединен с первыми входами первого и второго элементов И, вторые вхо, .ы которых .соединены, соответственно, с первым и вторым информационными входами управляемого арифметического модуля, третий информационный вход которого соединен со вторым входом четвертого элемента И, а второй вход второго элемента ИЛИ соединен . с седьмым управляьэщим входом управляемого арифметического модуля, первый и второй выходы которого подключены, соответственно, к единичному и нулевому выходам второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, а нулевой вход подключен к выходу четвертого элемента ИЛИ, а восьмой управляющий вход управляемого арифметического мо дуля соединен с первым входом четвер того элемента ИЛИ, второй вход котор го соединен с выходом девятого элемента И,первый вход которого соединен с нулевым выходом первого триггера, а первый вход пятого элемента ИЛИ со динен с выходом пятого элемента И,второй вход которого соединен с четвертым „информационным входом модуля, пятый информационный вход которого соедине со вторыми входами шестого и восьмог элементов И, а шестой информационный вход - со вторым входом седьмого элемента И и с Первы входом десятого элемента И, апервый вход пятого элемента И связан со вторым входом десятого элемента И, выход которого соединен с первым входом одиннадцатого элемента И, второй вхо кдторого связан с выходом восьмого элемента И, а выход одиннадцатого элемента И - с первыми входами двенадцатого и тринадцатого элементов И,, вторые -входы которых соединены, соответственно, с единичным и нулевым выходами второго триггера/ а выходы двенадцатого и тринадцатого элементов И связаны соответственно, с третьим входом второго элемента ИЛИ и со вторым входом первого элемента ИЛИ, четвертые входы которых подключены,к выходам, соответственно, шестого и четырнадцатого элементов И, третий вход первого элемента ИЛИ соединен с выходом седьмого элемента И, а первый вход четырнадцатого элемента И связан со вторым входо пятого элемента И, а второй вход с первым входом седьмого элемента И а девятый и десятый управляющие входы модуля соединены со вторыми входами, соответственно, пятого и шестого элементов ИЛИ, третьи входы которых связаны с одиннадцатым управляющим входом модуля, а первый вход шестого элемента ИЛИ подключен к первому входу пятого элемента ИЛИ, выход которого соединен со вторым входом третьего элемента И, а выход шестого элемента ИЛИ - со вторым входом девятого элемента И, а выходы первого триггера связаны, соответственно , единичный - с третьим выходом, а нулевой - с четвертым 2 Однако указанный управляемый логический модуль сложен. Цель изобретения - упрощение модуля. Поставленная цель достигается тем, что в управляемом логическом модуле,- содержащем первый и второй триггеры, девять элементов И, шесть элементов ИЛИ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соедирк-:н с единичны) входом первого триггера, выход второго элемента И соединен с первым «хопом второго элемента ИЛИ, выход которого подклюгчен к нулевому входу первого триггера, единичный выход которого соединен с первым входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу четвертс1го элемента И, первые входы четвертого пятого, шестого, седьмого и восьмого элементов И соединены соответственно с первым, вторым, третьим, четвертым и пятым управляющими входами модуля, шестой управляющий вход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым информационными входами модуля, третий информационный вход которого соединен с вторым входом четвертого элемента И, а второй вход второго элемента ИЛИ - с седьмым управляющим входом модуля, первый и второй выходы которого подключены соответственно к единичному и нулевому выходс1М второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, а нулевой вход подключен к выходу четвертого элемента ИЛИ, восьмой управляющий вход модуля соединен с первыгл входом четвертого элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, первый вход которого соединен с нулевым выходом первого триггера, а первый вход пятого элe :eнтa ИЛИ соединен с выходом пятого элемента И, единич, ные выходы первого и второго триггеров соединены с. вторыми входами cor ответственно пятого, шестого элементов И, нулевые выходы первого и второго триггеров подключены к вто-: рым входам соответственно седьмого и восьмого элементов, а выход шестого элемента И соединен с вторым входом пятого элемента ИЛИ, выход которого подключен к третьему выходу модуля, четвертый выход которого соединен с выходом шестого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно седьмого и восьмого элементов И, а девятый, десятый и одиннадцатый управляющие входы модуля соединены с вторыми входами соответственно третьего и девятого элементов И и первого элемента ИЛИ. На фиг.1 представлена схема управляемого логического модуля; на фиг.2схема управляемого регистра, состоящего из предложенных модулей. Модуль содержит первый 1 и второй 2 RS-триггеры, девять элементов И 3-11, шесть элементов ИЛИ 12-17, три информационных 18-20 и одиннадцать

управляющих 21-31 входов, а также четыре выхода 32-35. Выход первого элемента И 3 соединен с первым входом первого элемента ИЛИ 12, выход которого соединен с единичным входом первого триггера 1, а выход второго элемента И 4 соединен с первым входом второго элемента ИЛИ 13, выход которого подключен к нулевому входу первого триггера 1. Единичный выход первого триггера 1 соединен с первым входом третьего элемента И 5, выход которого соединен с первым входом третьего элемента ИЛИ 14, Второй вход третьего элемента ШШ 14 подключен к выходу четвертого элемента И 6. Первый вход четвертого элемента И б и первые входы пятого 7, шестого 8, седьмого 9 и восьмого 10 элементов И соединены соответственно с первым 21, вторым 22, третьим 23, четвертым 24 и пятым 25 управляющими входами модуля. Шестой управляющий вход 26 модуля соединен с первыми входами первого 3 и второго 4 элементов И, вторые входы которых соединены соответственно с первым 18 и вторым 19 информационными входами модуля, третий информационный вход 20 которого соединен с вторым входом четвертого элемента И б. Втррой вход второго элемента ИЛИ 13 соединен с седьмым управляющим входом 27 модуля. Первый 32 и второй 33 выходы управляемого логического модуля подключены соответственно к единичнo лy и нулевому выходам триггера 2, единичный вход которого соединен с. выходом третьего элемента ИЛИ 14, а нулевой вход подкл1рчен выходу четвертого элемента ИЛИ 15. Восьмой управляющий вход 28 управляемого логического модуля соединен с первым входом четвертого элемента ИЛИ 15, второй вход которого соединен с выходом девятого элемента И 11, Первый вход девятого элемента И 11 соединен с нулевым выходом первого триггера 1. Первый вход пятого элемента ИЛИ 16 соединен с выходом пятого элемента И 7. Единичный и нулевой выходы первого триггера 1 и второго триггера 2 соединены с вторыми входами соответственно пятого 7, шестого 8, седьмого 9 и восьмого 10 элементов И. Выход шестого элемента И 8 соединен с вторым входом пятого элемента ИЛИ 16, выход которого подключен к третьему выходу 34 модуля.. Четвертый выход 35 модуля соединен с выходом шестого элемента ИЛИ 17, первый и второй входы которого соединены с выходами соответственно седьмого 9 и восьмого 10 элементов И Девятый 29, десятый 30 и одиннадцатый 31 управляющие входы модуля соединены с вторыми входами соответственно третьего 14 и девятого 11

элементов И и первого элемента ИЛИ 12.

На вход модуля подаются следующие сигналы:

х - i-й разряд операнда (информа5 ционный вход 20);

i-й разряд операнда или содержимое младшего, старшего разряда (информационные входы 18 и 19).

Сигналы У1-У8 обеспечивают выполнение следующих операций,

У1 (вход 21) - прием операнды X во второй триггер 2;

У2 (вход 22) - вьщача содержимого первого триггера 1 в прямом коде. 5 УЗ (вход 23) - вьщача содержимого второго триггера 2 в прямом коде)

У4 (вход 24) - выдача содержимого . первого триггера 1 в инверсном коде;

У5 (вход 25) - выдача содержимого Q второго триггера 2 в инверсном коде;

У7 (вход 27) - установка первого триггера 1 на

У8 (вход 28) - установка второго триггера 2 на

f УП (вход.31) - установка первого триггера 1 на 1,

Кроме вышеперечисленных, применяются также управляющие сигналы У6, У9 и У10, которые подаются на управляющие входы УВх1-УВхЗ,

Управляющие входы УВх1-УВхЗ в модуле не существуют физически, но образуются после определенного соединения управляющих входов управляемого логического модуля соответственно 26, 29 и 30,

Сигналы Уб, У9 и У10 обеспечивают выполнение следующих операций,

Уб - прием операнды в первый триггер 1; .

У9, У10 - перепись кода из первого триггера 1 во второй триггер 2,

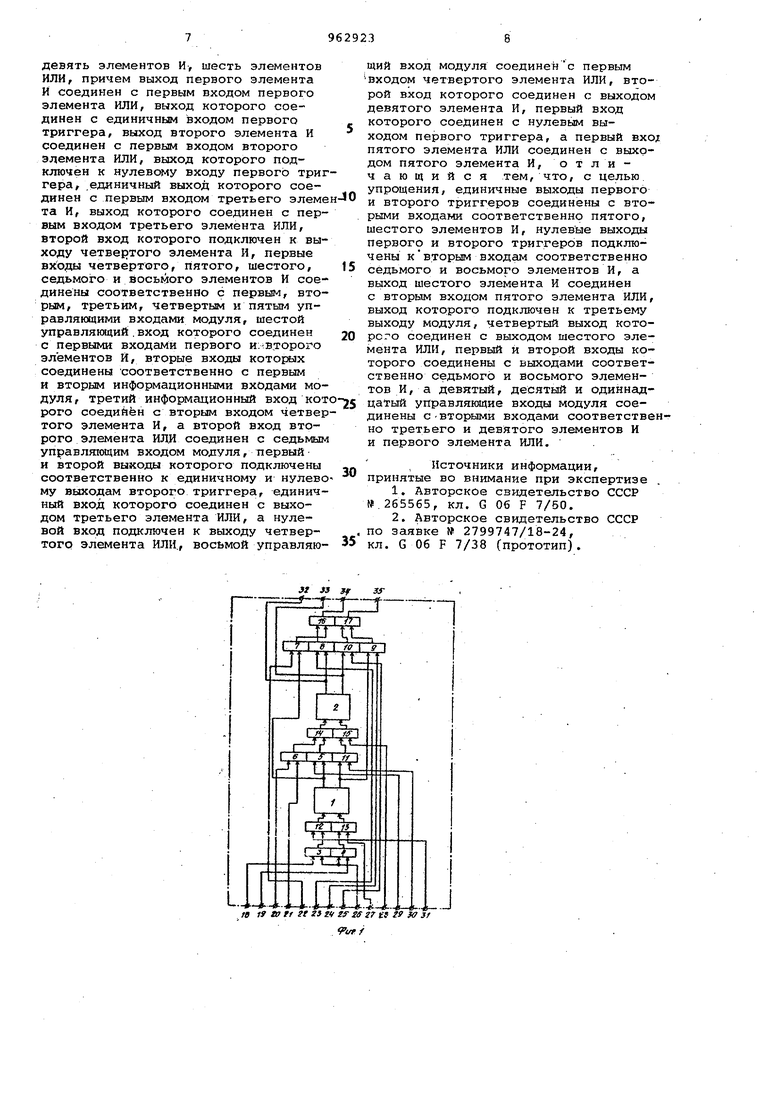

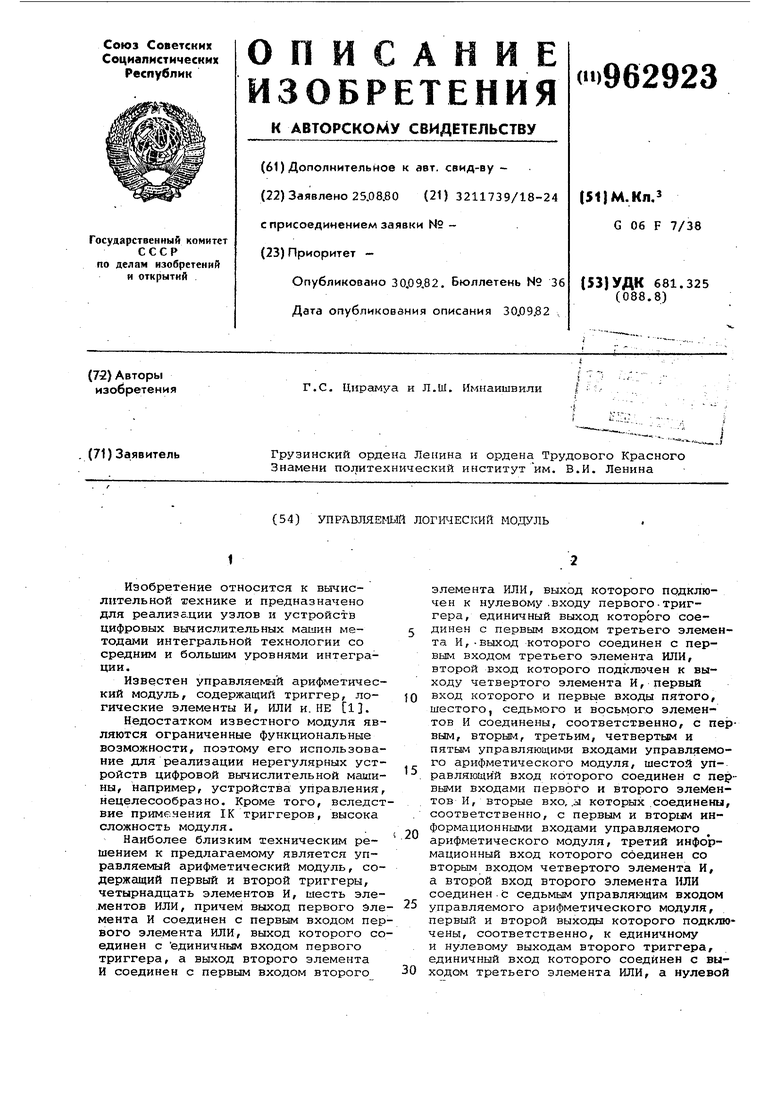

Пример построения п-разрядного упт равляемого логического регистра(для ), каждый разряд которого представляет собой управляемый логический модуль, представлен на фиг,2, С помощью управляемого регистра, в зависимости от коммутации, можно реализовать 42 логических, арифметических 0 и специальных вычислительных функций. С помощью управляемого арифметического регистра, построенного на модулях прототипа, - только 39, Сложность уп-. равляемого логического модуля по квай5 У равна 42, сложность по квайну модуля-прототипа равна 58. Таким образом, применение предлагаемого управляемого модуля в вычислительных устройствах по.зволит существенно их упростить,

0

Формула изобретения

Управляемый логический модуль, 65 .содержащий первый и второй триггеры

девять элементов И шесть элементов ИЛИ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с единичным входом первого триггера, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого подключен к нулевому входу первого триггера, .единичный выход которого соединен с первым входом третьего элеме та И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, первые входы четвертого, пятого, шестого, седьмого и восьмого элементов И соединены соответственно с первым, вторым, третьим, четвертым и пятыгл управляющими входами модуля, шестой управляющий.вход которого соединен с первыми входами первого и.-в,торого элементов И, вторые входы которых соединены соответственно с первым и вторым информационными входами модуля, третий информационный вход кот рого соедийён с вторым входом четвертого элемента И, а второй вход второго элемента ИДИ соединен с седьмым управляющим входом модуля, первый и второй выходы которого подключены соответственно к единичному и нулево му выходам второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, а нулевой вход подключен к выходу четвертого элемента ИЛИ., восьмой управляющий вход модуля соединенс первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, первый вход которого соединен с нулевым выходом первого триггера, а первый вхо пятого элемента ИЛИ соединен с выходом пятого элемента И, отличающийся тем, что, с целью упрощения, единичные выходы первого и второго триггеров соединены с вторыми входами соответственно пятого, шестого элементов И, нулевые выходы первого и второго триггеров подключены квторым входам соответственно седьмого и восьмого элементов И, а выход шестого элемента И соединен с вторым входом пятого элемента ИЛИ, выход которого подключен к третьему выходу модуля, четвертый выход которого соединен с выходом шестого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно седьмого и восьмого элементов И, а девятый, десятый и одиннадцагый управляющие входы модуля соединены сВторыми входами соответствено третьего и девятого элементов И и первого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР №.265565, кл. G 06 F 7/50.

2.Авторское свидетельство СССР по эаявке 2799747/18-24,

кл. G 06 F 7/38 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Процессор | 1981 |

|

SU962964A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

.

п

.J

Авторы

Даты

1982-09-30—Публикация

1980-08-25—Подача