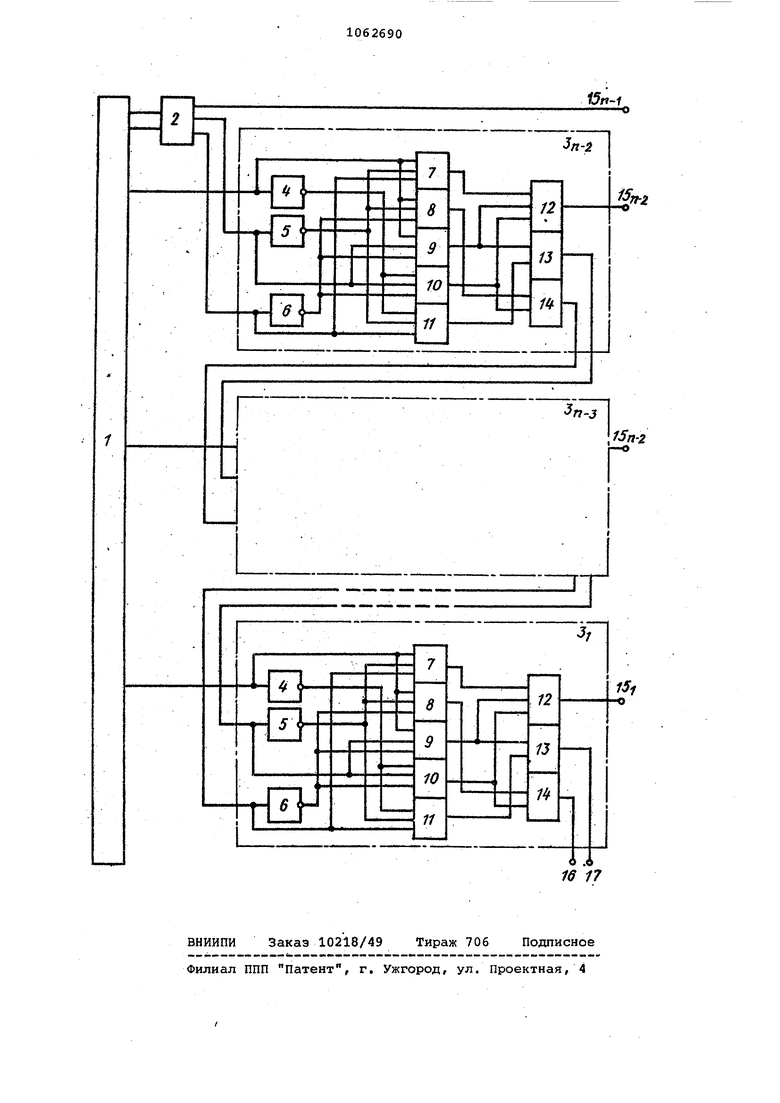

Изобретение относится к вычислительной технике и может быть исполь зовано в специализированных вычисли тельных устройствах, Известно устройство для деления двоичных чисел на три, содержащее 17/2 однотипных логических схем, каж дая КЗ которых содержит двухразрядный регистр делимого, двувходовый дешифратор, логический блок, реализующий логические выражения определения значений двух разрядов и двух функций переноса l . Это устройство имеет большие аппаратурные затраты, .связанные с:-при менением П/2 дешифраторов. Наиболее близким по технической сущности к предлагаемому является устройство для деления двоичных чисел на три 2 , содержащее регистр делимого и (У1- 1) блоков формирова ния частного одноразрядных вычитателей (, и число разрядов делимого связанных последовательно, каждый из которых состоит из полусумматора элемента сложения по модулю два, элемента И и элемента ИЛИ, причем выходы разрядов регистра делимого соединены с входами соответствующих одноразрядных вычитателей, выходы которых подключены к выходным шинам устройства. Это устройство имеет сравнительно невысокое быстродействие. Целью изобретения является повышение быстродействия устройства Указанная цель достигается тем, что в устройство для деления двоичных чисел на три, содержащее регистр делимого и (п- 2) блоков фор мирования частного, причем каждый блок форш-грования разряда частного содержит первый элемент И и первый элемент ИЛИ, первый вход которого соелипен с выходом первого элемента И данного блока формирования разряда частного, введены дешифратор, а каж,цый блок формирования разряда частнрго - три элемента НЕ, второй, третр1й, четвертый и пятый элементы И, второй и третий элементы ИЛИ, причем выход каждого разряда с первого по (п- 2)-и регистра делимого соединен с входом первого элемента НЕ и первыми входами первого, второ го и третьего элементов И соответствующего блока формирования разряд частного, в котором выход первого элемента НЕ.соединен с первыми входами четвертого и-пятого элементов И, выход второго элемента НЕ соединен с BTOpbUviH входами первого, второго и пятогоэлементов И, вход вто рого элемента НЕ подключен к вторым входам третьего и четвертого элементов И, выход третьего элемента НЕ соединен С третьими входами втор го, третьего и четвертого элементов И, вход третьего элемента НЕ соединен с третьими входами первого и пятого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами третьего и четвертого элементов И, входы второго элемента ИЛИ соединены с выходами третьего и пятого элементов И, входы третьего элемента ИЛИ соединены с выходами второго и четвертого элементов И, выход первого элемента ИЛИ каждого блока формирования разряда частного соединен с соответствующей выходной шиной частного, выходы f h-l) -го и ц-го разрядов регистра делимого подключены к входам дешифратора, первый выход которого соединен с (и - 1)-и выходной шиной частного, а второй и третий выходы подключены к входам соответственно второго и третьего элементов НЕ (h-2)-го блока формирования разряда частного, входы второго и третьего элементов НЕ каждого блока формирования разряда частного подключены к выходам соответственно второго и третьего элементов ИЛИ последующего блока формирования разряда частного, выходы второго и третьего элементов ИЛИ первого блока формирований разряда частного соединены с выходными шинами остатка. На чертеже представлена схема устройства для деления двоичных чисел на три. Устройство содержит регистр 1 делимого, дешифратор 2, ( h- 2) блоков 3 формирования разряда частного, калсдый из которых содержит элементы НЕ 4 - 6, элементы И 7 - 11, элементы ИЛИ. 12 - 14, Выходами устройства являются выходные шины 15 и шины 16 и 17 остатка. Устройство работает следующим образом, Делимое записывается в регистр 1 Два .старших разряда регистра 1 анализируются дешифратором 2, на первом выходе.которого формируется единица при наличии единицы на выходах обоихстарших разрядов регистра 1. На втором выходе формируется единица при наличии единицы только на выходе П -го разряда регистра 1, На третьем выходе формируется единица при наличии единицы на выходе .( п - 1) -го разряда регистра. Первый выход дешифратора 2 является {И- 1) -ым разрядом частного, второй и третий выходы дешифратора 2 являются выходами, на которых формигйуются остатки io и 01 соответственно, полученные при делении информации, поступающей с выходов двух старших разрядов регистра 1,

В блоке 3„.2. формирования ( п-2 -го разряда частного анализируется информация, поступающая с(м-2|-го разряда регистра 1 и остатки от деления двух старших разрядов -регистра 1, поступающие с второго и третьего выходов дешифратора 2. На первом выходе этого блока формируется единица при наличии единицы на следующих его входах: на первом и втором, или на первом и третьем, или только на втором. На втором выходе этого блока формируется единица при наличии единицы на, следуюцих его входах: первом и втором или на третьем. На третьем выходе этого блока формируется единица при наличии единицы на первом входе или на втором. Первый выход этого блока является (и разрядом частного, второй и третий выходы являются выходами остатков 10 и 01 соответственно, полученные при делении трехразрядного двоичного числа, поступающего на его входы

В блоке,3 формирования(И-З)- разряда частного анализируется информация, поступающая с (п-З)-го разряда регистра 1 и остатки от деления трех старших разрядов регистра 1. Работа этого блока формирования («-3)i-ro разряда частного и всех последующих блоков формирова0ния разрядов частного аналогична рассмотренному выше.

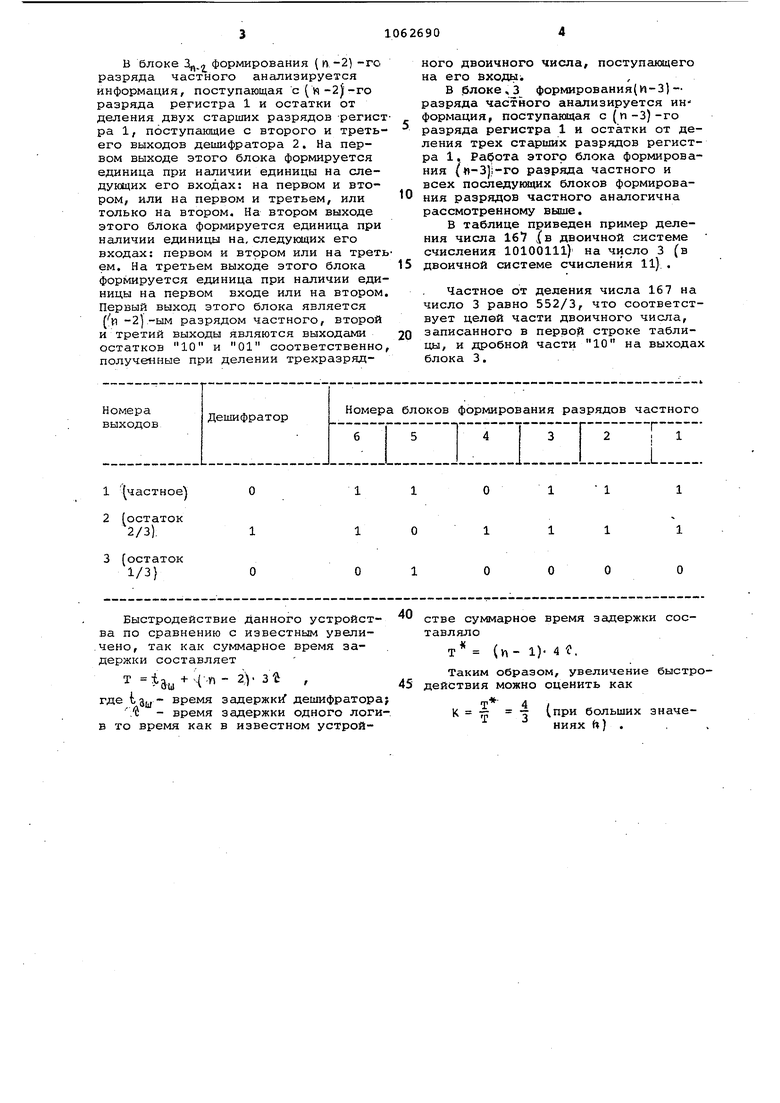

В таблице приведен пример деления числа ,(в двоичной системе счисления 10100111) на число 3 (в 5 двоичной системе счисления 11).,

Частное от деления числа 167 на число 3 равно 552/3, что соответствует целей части двоичного числа, 0 записанного в первой строке таблицы, и дробной части 10 на выходах блока 3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел на три | 1985 |

|

SU1260947A1 |

| Устройство для деления двоичных чисел на три | 1988 |

|

SU1571579A1 |

| Устройство для деления на три | 1989 |

|

SU1667058A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Устройство для деления п-разрядных двоично-десятичных чисел | 1982 |

|

SU1026139A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

УСТРОЙСТВО Д31Я ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ НА ТРИ, содержащее регистр делимого и (п - 2) блоков формированиа разрядов частного, причем каждый блок формирования разряда частного содержит первый элемент И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента И данного блока формирования разряда частного, отличающееся тем, что, с целью повышения быстродействия, оно содержит дешифратор, а каждый блок формирования разряда частного содержит три элемента НЕ, второй, третий, четвертый и пятый элементы И,второй и третий элементы ИЛИ, причем выход каждого разряда с первого по ((п-2) -и регистра делимого соединен с входом первого элемента НЕ и первыми входами первого, второго и третьего элементов И соответствующего блока формирования разряда частного, в котором выход первого элемента НЕ соединен с первыми входами четвертого и пятого элементов И, выход вто- рого элемента НЕ соединен с вторыми входами первого, второго и пятого элементов И, вход второго элемента НЕ подключен к вторым входам. третьего и четвертого элементов И, выход третьего элемента НЕ соединен с третьими входами второго, третьего и четвертого элементов И, вход третьего элемента НЕ соединен с третьими входами первого и пятого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами третьего и четвертого элементов И, входы второгоэлемента . ИЛИ соединены с выходами третьего и пятого элементов И, входы третьего элемента ИЛИ соединены с выходами второго и четвертого элементов И, выход первого элемента ИЛИ каждого (Л блока формирования разряда частного соединен с соответствующей выходной шиной частного, выходы (и- 1)-го и П-го разрядов регистра делимого подключены к входам дешифратора, первый выход которого соединен с : (п- 1) -и выходной шиной частного, а второй и третий выходы подключены к входам соответственно второго и третьего элементов НЕ (ti - 2) -го блока формирования разряда частного., входы второго и третьего элементов НЕ каждого блока формирования разряда частного подключены к выходам соответственно второго и третьего элементов ИЛИ последугацего блока формирования разряда частного, выходы второго и третьего элементов ИЛИ первого блока формирования частного соединены с выходными шинами остатка.

за по сравнению с известным увеличено, так как суммарное время задержки составляет Т -±, + 2t ,45 задержка дешифратора; ,& - время задержки одного логив то время как в известном устройтавляло„, ) (и- ) 4 . Таким образом, увеличение быстродействия можно оценить как Т 4 / К 7{Г о упри больших значениях ft) .

Q

6

« «

iSr

n-2

n

8

т

11

n-j

15n-2

г

I5i

12 -o

8

10

n

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления п-разрядного двоичного кода на три | 1974 |

|

SU506853A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 758153, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-02-11—Подача