ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления на три | 1987 |

|

SU1437856A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Устройство для деления двоичных чисел на три | 1988 |

|

SU1571579A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах. Целью изобретения является повышение быстродействия устройства. Устройство для деления двоичных чисел на три содержит регистр 1, дешифратор 2 и (N-2)/3 блоков 3 формирования разрядов частного. Быстродействие устройства составляет T = Tдш + NΤ, где Τ - время задержки одного логического элемента, Tдш - время задержки дешифратора. 1 з.п.ф-лы, 2 фиг., 2 табл.

О О vj

О

ся со

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных устройствах.

Целью изобретения является повышение быстродействия устройства.

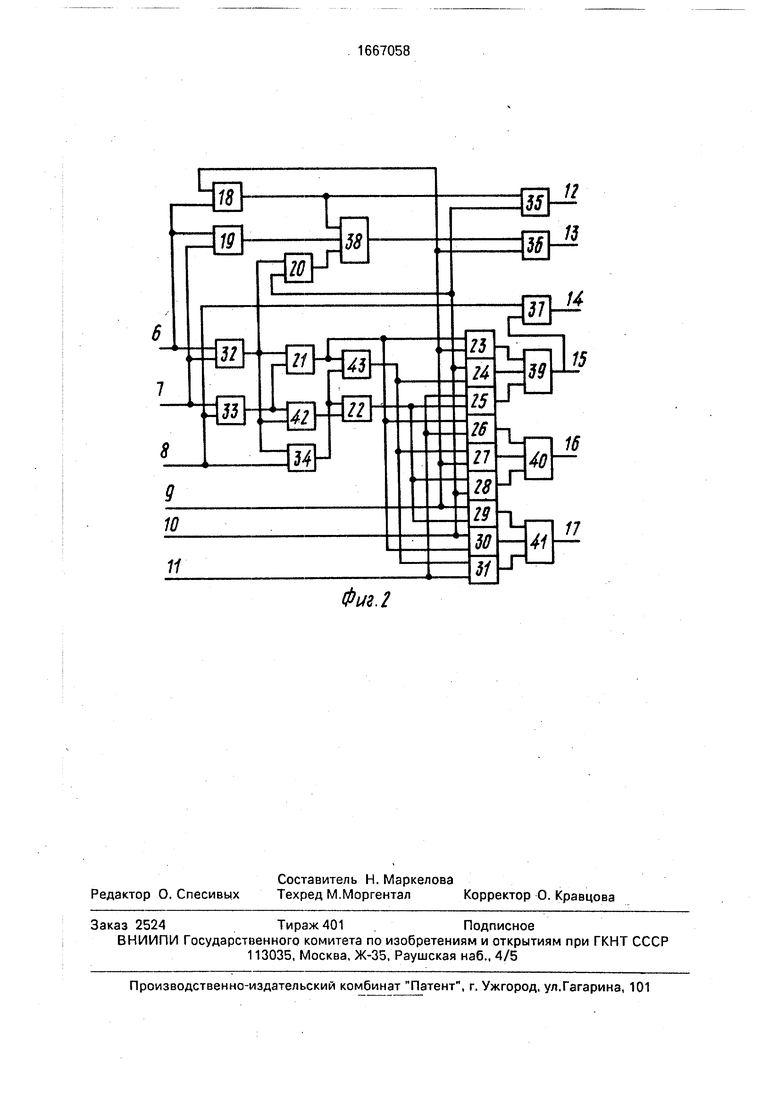

На фиг. 1 представлена функциональная схема устройства для деления на три; на фиг. 2 - функциональная схема блока формирования разрядов частного.

Устройство (фиг. 1) содержит регистр 1, дешифратор 2, блоки 3i,32Зп-2/з формирования разрядов частного 3, выходную шину 4, выходную шину 5 остатка.

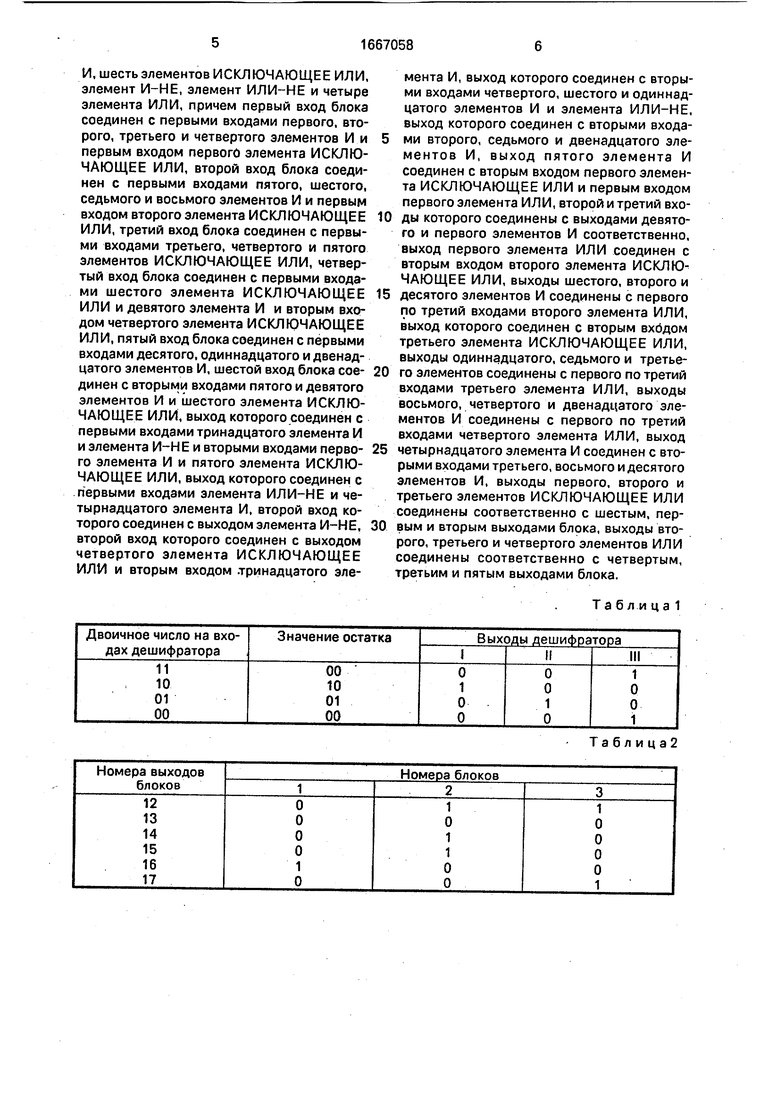

Блок формирования разрядов частного (фиг. 2) содержит шестой вход 6 блока, четвертый вход 7 блока, третий вход 8 блока, второй вход 9 блока, первый вход 10 блока, пятый вход 11 блока, шестой выход 12 блока, первый выход 13 блока, второй выход 14 блока, четвертый выход 15 блока, третий выход 16 блока, пятый выход 17 блока, пятый, девятый, первый, тринадцатый, четырнадцатый, шестой, второй, десятый, одиннадцатый, седьмой, третий, восьмой, четвертый и двенадцатый элементы И 18-31, шестой, четвертый, пятый, первый, второй и третий элементы 32-37 ИСКЛЮЧАЮЩЕЕ ИЛИ, с первого по четвертый элементы ИЛ И 38-41, элемент И-НЕ 42, элемент ИЛИ-НЕ 43.

Устройство работает следующим образом.

Делимое записывается в регистр 1. Два старших разряда регистра 1 анализируются дешифратором 2, на первом выходе которого формируется единица при наличии единицы на выходах обоих старших разрядов регистра 1. На втором выходе дешифратора формируется единица при наличии единицы на выходе старшего разряда регистра 1. На третьем выходе формируется единица при наличии единицы на втором разряде регистра. На четвертом выходе формируется единица при наличии нулей или единиц на обоих входах дешифратора. Первый выход дешифратора 2 является старшим разрядом частного, на втором, третьем и четвертом выходах дешифратора 2 формируется остаток 10, 01 и 00 соответственно, полученный при делении на три двухразрядного числа, поступающего на дешифратор 2.

В первом блоке 3 формирования разрядов частного происходит деление на три пятиразрядного двоичного числа, поступающего на вход 10 и вход 9, входы 6-8 блока 3. На выходах 12, 13, 14 блока 3 формируются три разряда частного. Значение остатка от деления формируется на выходах 16, 15, 17 блока 3 соответственно 10, 01 и 00.

Аналогично работают и все блоки 3. На выходных шинах 4 формируется частное от деления на три, на выходных шинах 5 остатка - остаток.

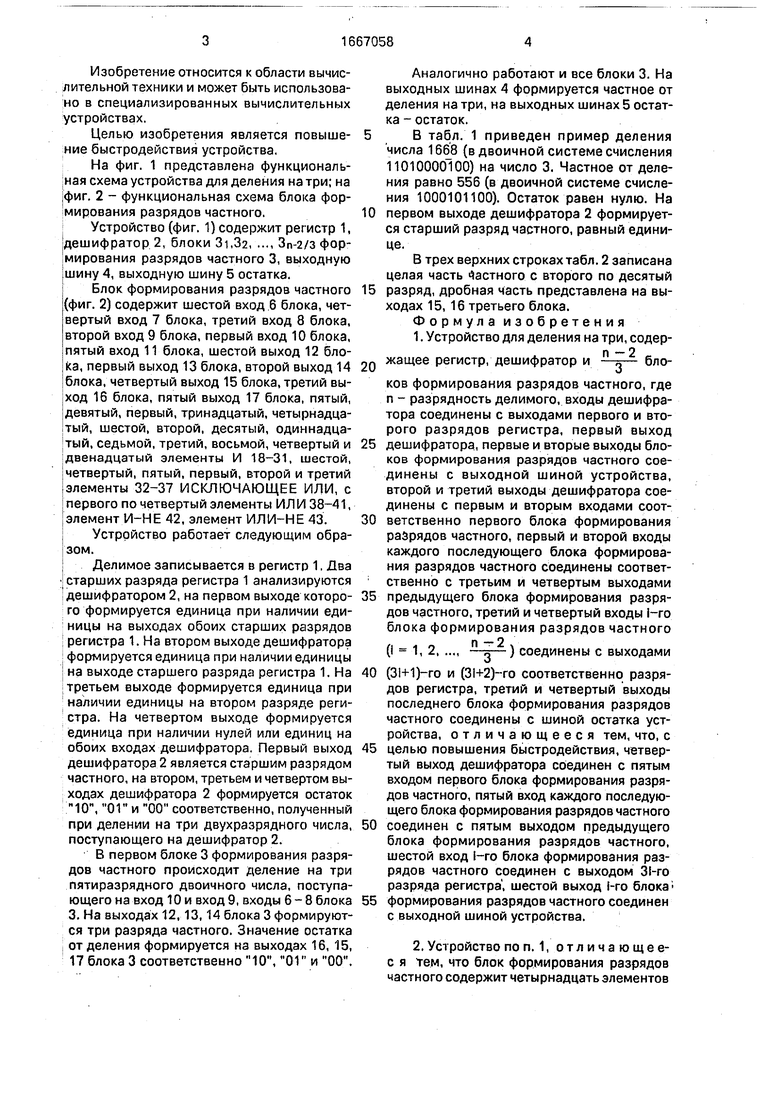

В табл. 1 приведен пример деления

числа 1668 (в двоичной системе счисления 11010000100) на число 3. Частное от деления равно 556 (в двоичной системе счисления 1000101100). Остаток равен нулю. На первом выходе дешифратора 2 формируется старший разряд частного, равный единице.

В трех верхних строках табл. 2 записана целая часть частного с второго по десятый разряд, дробная часть представлена на выходах 15, 16 третьего блока.

Формула изобретения

блоков формирования разрядов частного, где п - разрядность делимого, входы дешифратора соединены с выходами первого и второго разрядов регистра, первый выход

дешифратора, первые и вторые выходы блоков формирования разрядов частного соединены с выходной шиной устройства, второй и третий выходы дешифратора соединены с первым и вторым входами соответственно первого блока формирования разрядов частного, первый и второй входы каждого последующего блока формирования разрядов частного соединены соответственно с третьим и четвертым выходами

предыдущего блока формирования разрядов частного, третий и четвертый входы 1-го блока формирования разрядов частного

п -- О

(I 1, 2 -я-) соединены с выходами

(31+1)-го и (3l+2)-ro соответственно разрядов регистра, третий и четвертый выходы последнего блока формирования разрядов частного соединены с шиной остатка устройства, отличающееся тем, что, с

целью повышения быстродействия, четвертый выход дешифратора соединен с пятым входом первого блока формирования разрядов частного, пятый вход каждого последующего блока формирования разрядов частного

соединен с пятым выходом предыдущего блока формирования разрядов частного, шестой вход 1-го блока формирования разрядов частного соединен с выходом 31-го разряда регистра , шестой выход 1-го блокаформирования разрядов частного соединен с выходной шиной устройства.

И, шесть элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, элемент ИЛИ-НЕ и четыре элемента ИЛИ, причем первый вход блока соединен с первыми входами первого, второго, третьего и четвертого элементов И и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход блока соединен с первыми входами пятого, шестого, седьмого и восьмого элементов И и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход блока соединен с первыми входами третьего, четвертого и пятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый вход блока соединен с первыми входами шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и девятого элемента И и вторым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый вход блока соединен с первыми входами десятого, одиннадцатого и двенадцатого элементов И, шестой вход блока сое- динен с вторыми входами пятого и девятого элементов И и шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. выход которого соединен с первыми входами тринадцатого элемента И и элемента И-НЕ и вторыми входами перво- го элемента И и пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первыми входами элемента ИЛИ-НЕ и четырнадцатого элемента И, второй вход которого соединен с выходом элемента И-НЕ, второй вход которого соединен с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторым входом .тринадцатого элемента И, выход которого соединен с вторыми входами четвертого, шестого и одиннадцатого элементов И и элемента ИЛИ-НЕ, выход которого соединен с вторыми входами второго, седьмого и двенадцатого элементов И, выход пятого элемента И соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входом первого элемента ИЛИ, второй и третий входы которого соединены с выходами девятого и первого элементов И соответственно, выход первого элемента ИЛИ соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы шестого, второго и десятого элементов И соединены с первого по третий входами второго элемента ИЛИ, выход которого соединен с вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы одиннадцатого, седьмого и третьего элементов соединены с первого по третий входами третьего элемента ИЛИ, выходы восьмого, четвертого и двенадцатого элементов И соединены с первого по третий входами четвертого элемента ИЛИ, выход четырнадцатого элемента И соединен с вторыми входами третьего, восьмого и десятого элементов И, выходы первого, второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с шестым, первым и вторым выходами блока, выходы второго, третьего и четвертого элементов ИЛИ соединены соответственно с четвертым, третьим и пятым выходами блока.

Таблица

Таблица2

Фш.2

| Устройство для деления п-разрядного двоичного кода на три | 1974 |

|

SU506853A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления на три | 1987 |

|

SU1437856A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-03-22—Подача