операционной секции, управляющий пход каждого j -го (j г2,3, ..., выходного мультиплексора операционного блока соединен с j -м выходом первой группы п информационных выходов сдвигового регистра с первыг управляющим входом ( +1) -г межсекционного мультиплексора операционного блока, с вторым управляющим входом j -го межсекционного мультиплексора операционного блока и с управляющим входом (j -1)-го входного мультиплексора операционного блока, управляющий вход первог выходного мультиплексора операционного блока соединен с управляющим входом первого и с первым управляющим входом второго межсекционных мультиплексоров операционного блока и с первшл выходом первой группы П информационных выходов сдвигового регистра, управляющий вход (п выходного мультиплексора операционного блока соединен с вторым управляющим входом (h lj--ro межсекциониого мультиплексора операционного блока, с управляющим входом (п-2)-го входного мультиплексора операционного блока и с выходом первой группы информационных выходов регистра сйвига, -и выход первой группы и информационных выходов которого соединен с управляющим входом h -го межсекционного мультиплексора операци-J онкого блока, первый информационный вход каждого -го и второй информационный вход калодого { i +1)-го межсекционных мультиплексоров операционного блока соединен с выходом признаков -и операционной секции второй информационный вход первого межсекционного мультиплексора операционного блока соединен с входом признаков первой операционной секци первый информационный вход , п -го межсекционного мультиплексора операционного блока соединен с выходом признаков п -и операционной секции выход кахадого Кто ( к - 1,2,...., 11 -1) межсекционного мультиплексора операционного блока соединен с входом признаков (к +1)-и операционной секции, выход П -го межсекционного мультиплексора операционного блока соединен с информационным входом мультиплексора логических условий, выход каждого i -го входного мультиплексора операционного блока соединен с информационным входом (i +1)-и операционной секции, первый информационный вход каждого m -го (п1 1,2,...,11-3} и второй информационный вход каждого (т+1)-го входных мультиплексоров операционного блока соединены с (ni+l)-M входом группы информационных входов микпропроцессора, второй информационный вход первого и первый информационный вход (п-2)-го входных мультиплексоров операционного блока соединены соответственно с вторым и с (h-l)-M входами группы информационных входов микропроцессора, выходы выходных мультиплексоров блока микропрограммного управления соединены с адресныг и входами блока памяти микрокоманд, первый информационный вход каждого -го и второй информационный вход каждого ( +1}-го выходных мультиплексоров блока микропрограммного управления соединены с информационны - выходом ( секции микропрограммного управления, второй информационный вход первого выходного мультиплексора блока микропрограммного управления соединен с информационным выходом первой секции микпропрограммного управления, первый информационный вход (h-l)-ro выходного муль.типлексора блока микропрограммного управления соединен с информационным выходом 11 -и секции микропрограммного управления, управляющий вход каждого j -гО выходного мультиплексора блока микропрограммного управления соединен с j -м выходом второй группы ( И -1) информационных выходов сдвигового peгиcтjpa с первым управляющим входом (j + {)-го межсекционного мультиплексора блока микропрограммного управления, со вторым управляющим входом j -го межсекционного мультиплексора блока микропрограммного управления и с управляющим входом (1 -1)-го входного мультиплексора блока микропрограммного управления, управляющий вход первого выходного мультиплексора блока микропрограммного управления соединен с управляквдим входом первого и с первым управлшющим входом второго межсекционных мультиплексоров блока микропрограммного управления и с первым выходом второ группы ( и-1) информационных выходов сдвигового регистра, управляющий вход (h-l)-ro выходного мультиплексора блока микропрограммного управления соединен с вторым управляющим входом, (n-l)-ro межсекционного мультиплексора блока микропрограммного управления, с управляющим входом (ц-2)-го входного мультиплексора блока микропрограммного управления и с (п-1) -м выходом второй группы (п-1) информационных выходов сдвигового регистра, первый информационный вход , i -го и второй информационный вход (i +1)-го межсекционного мультиплексоров блока микропрограммного управления соединены с выходом признаков 4 -И секции микропрограммного управления, второй информационный вход первого

и первый информационный вход ( межсекционных мультиплексоров блока микропрограммного управления соединены соответственно с входом признаков первой секции микропрограммного управления и с выходом признаков ()й секции микропрограмviHoro управления, выход К -го межсекционного мультиплексора блока микропрограммного управления соединен с входом признака к+l)-и секции микропрограммного управления, выход каждого ( -го входного мультиплексора блока микропрограммного управления соединен с информационным входом секции микропрограммного управления, первый информационный вход каждого М -го и второй информационный вход каждого (nfi+l -ro входных мультиплексоров блока микропрограммного управления соединены с ( входом первой группы информационных выходов регистра микрокоманд, второй информационный первого и первый информационный входы ( входных мультиплексоров блока микропрограм- .. много управления соединены соответственно с вторым и с (п -1)-м входами первой группы информационных

выходов регистра микрокоманд, выход дешифратора соединен с входом сброса счетчика, установочный вход которого соединен с входом начальной установки микропроцессора и с установочным входом сдвигового регистра, вход синхронизации которого соединен с третьими управля;ощими входами секций микропрограммного управления и с выходом переполнения счетчика, счетный вход которого соединен с входом синхронизации микропроцессора, вход управления сдвигом и выход старшего разряда сдвигового регистра подключены соответственно к шине нулевого .потенциала и к выходу неисправности микропроцессора. 2, Микропроцессор по п. 1, о т л и ч а. ю щ и и с я тем, что, операционная секция состоит из дешифратора приемника результата, группы регистров общего назначения, мультиплексора операндов, су1-1матора, первого и второго блоков элементов ИЛИ, блока элементов НЕ, Первого, второго, третьего, четвертого, пятого и шестого блоков элементов И, дешифратора операций, накапливающего сдвигового регистра, информационный вход которого соединен с информационными входами группы регистров обего назначения и с выходом второго блока элементов ИЛИ, входы которого соединены соответственно с выходами первого, второго, третьего, четвертого и пятого блоков элементов И, первые входы которых соединены соответственно с первым, вторым, третьим.

етвертьлм и плтым выходами дешифратора операций, шестой выход которого соединен с управляющим входом накапливающего сдвигового регистра, вход синхронизации которого соединен с первым выходом дешифратора приемника результата, остальные выходы которого соединены с входами записи группы регистров общего назначения, группа, информационных выходов которых соединена с группой информационных входов мультиплексора операндов, выход которого соединен с первыг- информационным входом сумматора, с первьями входами шестого блока элементов И и первого блока элементов ИЛИ, вторые входы первого блока элементов ИЛИ, пятого и шестого бло ков элементов И, второй информационный вход сумматора, вход блока sjieментов НЕ и информационный вход накапливающего сдвигового регистра соединены с информационным входом операционной секции, вход переноса сумматора и вход сдвига накапливающего сдвигового регистра соединены с входом признаков операционной секции, выход сумматора.соединен с вторым входом первого блока элементов И, выход шестого блока элементов И соединен с вторьам входом второго блока элементов И, выход первого блока элементов ИЛИ соединен с вторым входом третьего блока элементов И, выход блока элементов НЕ соединен с вторым входом четвертого блока элементов И, вход дешифратора операций, управляющий вход мультиплексора операндов, вход дешифратора приемника результата соединены соответственно с входами группы входов кода микроопераций операционной секции, информационный вход мультиплексора операндов соединен с информационным входом процессорной секции, управляющий вход дешифратора приемника результата соединен с входом синхронизации процессорной секции, выход переноса сумматора и выход старшего разряда накапливающего сдвигового регистра соединены с выходом признаков операционной секции.

3. Микропроцессор по п. 1, отличающийся тем, что секция микропрограммного управлейия состоит из регистра, блока элементов ИЛИ, первого и второго блоков элементов И, сумматора, выход которого соединен с первым входом первого блока элементов И, второй вход которого соединен с нулевым входом второго блока элементов И и с первым управляющим входом секции, первый вход сумматора подключен к шине нулевого потенциала, второй вход сумматора соединен с информационным входом секции и с единичным

входом второго блока элементов И, выход которого подключен к первому входу -блока элементов ИЛИ, второй вход .которого соединен с выходом первого блока элементов И, выход блока элементов ИЛИ соединен с информационным входом регистра, выход которого соединен с информационным выходом секции, вход установки в

единицу, вход установки в ноль и вход синхронизации регистра соединены соответственно с вторым управляющим входом, с третьим управляющим входом и с входом синхронизации секции, вход и выход переноса сумматора соединены соответственно с входом и . выходом признаков секции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

1. СЕКЦИОННЫЙ МИКРОПРОЦЕССОР, содержащий блок памяти микрокоманд, регистр микрокоманд, мультиплексор логических условий, операционный блок, состоящий из h -операционных секций { п J 2, блок микропрограммного управления, состоящий из ц секций микропрограммного управления, первый управляющий вход каждой из которых соединен с первым информационным выходом регистра микрокоманд, вход синхронизации которого соединен с входами синхронизации операционных секций, секций . микропрограммного управления и с входом синхронизации микропроцессора, информационные входы первой и h -и секций микропрограммного управления соединены соответственно с первым и ( п-1)-м выходами первой группы информационных выходов регистра микрокоманд, информационные входы первой и я -и операционных секций соединены соответственно с первым и ( п-1)-м входами группы информационных входов микропроцессора, входы признаков первой секции микропрограммного управления и первой операционной секцией соединены соответственно с выходом мультиплексора логических условий и с вторым информационным выходом регистра микрокоманд, вторая группа идформационных выходов которого соединена с Группами входов кода микроопераций операционных секций, управляющий вход мультиплексора логических условий соединен с третьим информационным выходом регистра микрокоманд, группа информационных входов которого соединена с группой информационных выходов блока памяти микрокоманд вход начальной установки микропроцессора соединен с вторыми управляющими входами секций-микропрограммного управления, о т л и ч а ю щ и и с я тем, что, с целью повы-г : шения надежности. в него введены дешифратор, счетчик и сдвиговый регистр, в операционный блок введены (п-1) выходных мультиплексоров, (/) п межсекционных мультиплексоров и (и-2) входных мультиплексоров, а в блок микропрограммного управления введены (n-l) выходных мультиплексоров, (h-1) межсекционных мультиплексоров и { h-2) входных мультиплексоров, причем выходы выходных мультиплексоров операционного блока соединены с информационными выходами микропроцессора и с входами дешифратора, управляющий вход которого соединен с четвертым информационным выходом регистра микрокоманд, первый информационный вход каждого -го ( - 1,2, . . .(ц-2) выходного | мультиплексора операционного блока | соединен с вторым информационным вхо дом (л +1)-го выходного мультиплек,сора операционного блока и с инфор мационным выходом (+1)-й операционной секции, второй информационный вход первого выходного мультиплексора операционного блока соединен с информационным выходом первой операционной секции, первый информационный вход (fi -1)-го выходного мультиплексора операционного блока соединен с инфОЕ 1ационным выходом П -и

Изобретение относится к вычислительной технике и может быть испольровано для обработки данных в системах управления повышенной надежности.

Известен микропроцессор, содержащий секционный операционный блок микропрограммного управления, блок памяти микрокоманд, регистр микрокоманд l .

Недостатком данного устройства . является низкая надежность.

Наиболее близким по технической сущности является секционный микропроцессор , содержащий блок памяти микрокоманд, регистр микрокоманд, мультиплексор, логических условий, операционный блок, состоящий из И -операционных секций (nt2), блок микропрограммного управления, состоящий из И секций микропрограммного управления, первый управляющий вход, каждый из которых соединен с первым информационным выходом регистра микрокоманд, вход синхронизации которого соединен с входами синхронизации операционных секций, секций микропрограммного управления и с ВХОДОМ синхронизации микропроцесора, информационные входы первой и И -и секций микропрограммного управления соединены соответственно с первым и (и-1)-м выходами первой группы информационных выходов регисра микрокоманд, информационные входы первой и Н й операционных секций соединены соответственно с первым и ( входаг-1и группы информационных входов микропроцессора, входы признаков первой секции микропрограммного управления и первой операционной секции соединены соответственно с выходом мультиплексора логических условий и с вторым информационным выходом регистра микрокоманд, вторая группа информационных выходов которого соединена с группами входов кода микроопераций операционных секций, управляклций вход мультиплексора логических условий

соединен с третьим информационным выходом регистра микрокоманд, группа информационных входов которого соединена с группой .: информационных выходов блока памяти микрокоманд, вход начальной установки микропроцессора соединен с вторыми управляющими входами секций микропрограммного управления 2 .

Недостатком данного микропроцессора является низкая надежность, обусловленная тем, что в случае выхода из строя хотя бы одной микропроцессорной секций все устройство оказывается неработоспособным.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в секционный микропроцессо содержащий блок памяти микрокоманд, регистр микрокоманд, мультиплексор логических условий, операционный блок, состоящий из И -операционных секций ), блок микропрограммного управления, состоящий из П секций микропрограммного управления, первый управляющий вход каждой из которых соединен с первым информационным выходом регистра микрокоман вход синхронизации которопо соединен с входами синхронизации операционных секций, секций микропрограммного управления и с входом синхронизации микропроцессора, информационные входы первой и fl -и секций микропрограммного управления соединены соответственно с первым и (п -1) -м выходами первой группы информационных выходов регистра микрокоманд, информационные входы первой и Г) -и операционных секций соединены соответственно с первым и ( п -1) -м входами группы информационных входов микропроцессора, входы признаков первой секции микропрограммного управления и первой операционной секции соединены соответственно с выходом мультиплексора логических условий и с вторым ииформационным выходом регистра мийрокоманд, вторая группа информационных выходов которого соединена с группами входов кода микроопераций операционных секций, управляющий

вход мультиплексора логических условий соединен с третьим информационным выходом регистра микрокоманд, группа информационных входов которого соединена с группой информационных выходов блока памяти микрокоманд, вход начальной установки микропроцессора соединен с вторыми управляющими входами секций -микропрограммного управления, введены дешифратор, счетчик и сдвиговый регистр, в операционный блок введены (И -1) выходных мультиплексоров, П межсекционных мультиплексоров и (ii -2) входных мультиплексоров, а в блок микропрограммного управления введены (п -1) выходных мультиплексоров, (п -1 межсекционных мультиплексоров и (и-2) входных мультиплексоров, причем выходы выходных мультиплексоров операционного блока соединены с информационными выходами микропроцессора и с входами дешифратора, управляющий вход которого соединен с четвертым информационным выходом регистра микрокоманд, первый информационный вход каждого i -го ( 1, 2,...,h-2) выходного мультиплексора операционного блока соединен с вторым информационным входом (+1)-го выходного мультиплексора операционного

блока и с информационным выходом (( +1)-и операционной рекции, второй информационный вход первого выходного мультипЛексора операционного блока соединен с инфор1«Г ционныгл ыходом первой операционной секции, первый информационный вход {г -1) -го выходного мультиплексора операционного блока соединен с инфор «1ационным выходом И -а операционной секции, управляющий вход каждого j -го () г-2,3,..., h-2) выходного мультиплексора операционного блока соединен с } -м выходом первой группы И информационных выходов сдвигового регистра, с первым управляющим входом (J +1)-го межсекционного мультиплексора операционного блока, с вторым управляющим входом j -го межсекционного мультиплексора операционног о блока и с управляющим входом ( j -l)-го входного мультиплексора операционного блока, управляющий вход первого выходного мультиплексора операционного блока соединен с управляющим входом первого и с первым управляющим входом вторрго межсекционного мультиплексора операционного блока и с первым выходом первой группы П информацион ных выходов сдвигового регистра, управляющий вход (n-l)-ro

выходного мультиплексора опёрациоь ного блока соединен с вторым управляющим входом (ii-l)-ro межсекционного мультиплексора операционного блока, с управляющим входом ( входного мультиплексора операционного блока и с выходом первой группы информационных выходо регистра сдвига;, fi -и выход первой группы. М информационных выходов , которого соединен с управляющим входом 11 -го межсекционного мультиплексора операционного блока, первый информационный вход каждого

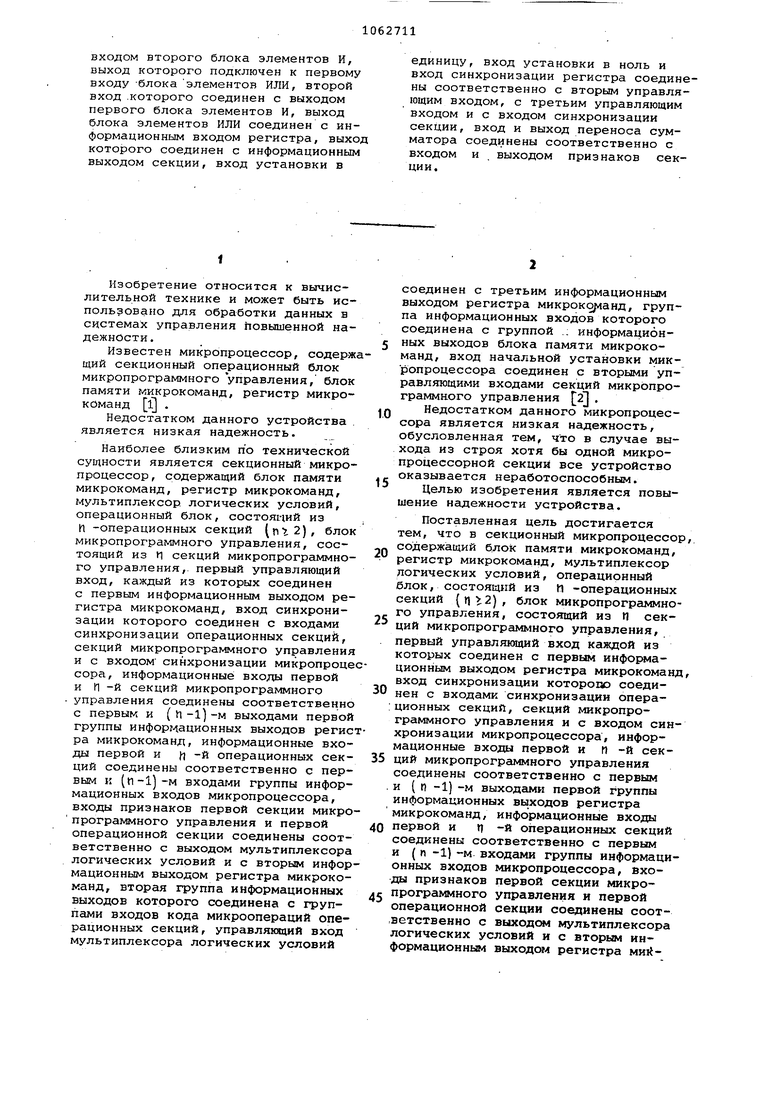

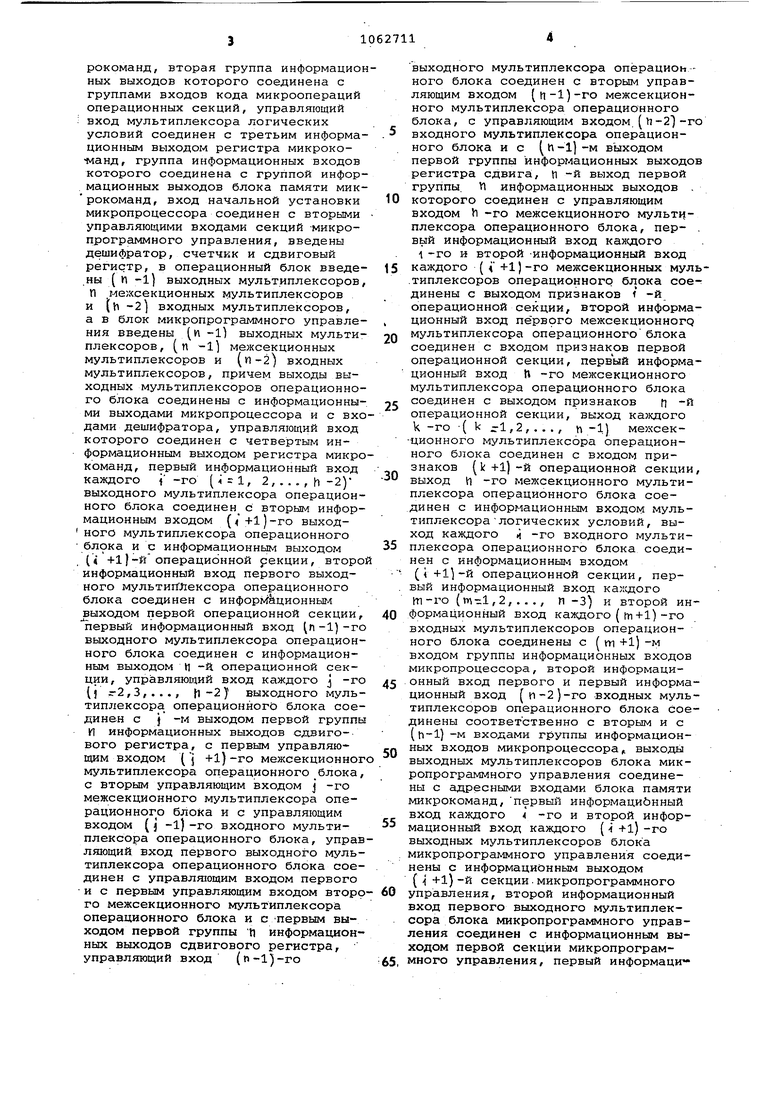

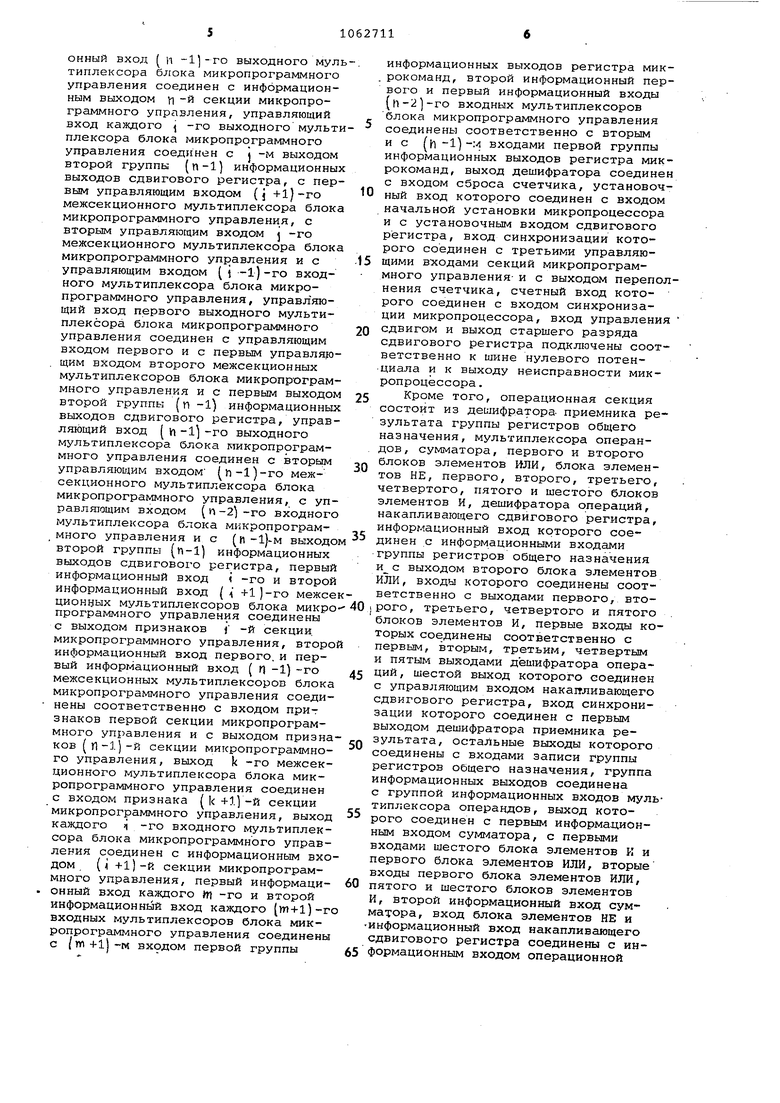

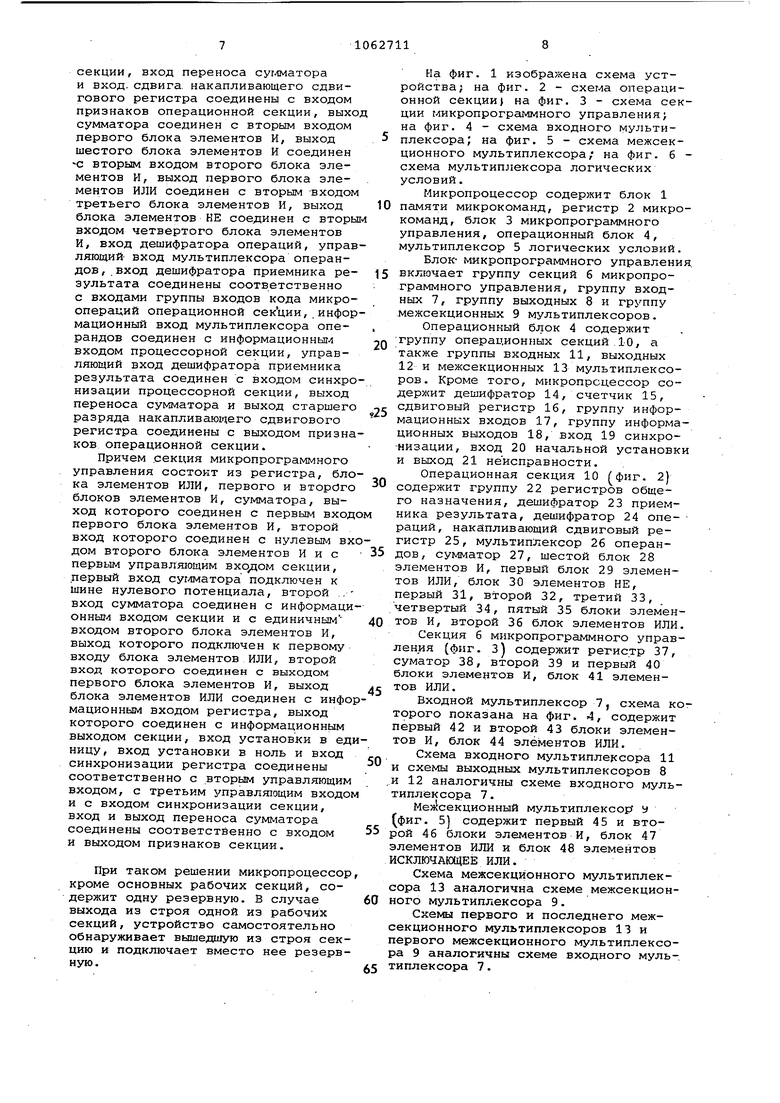

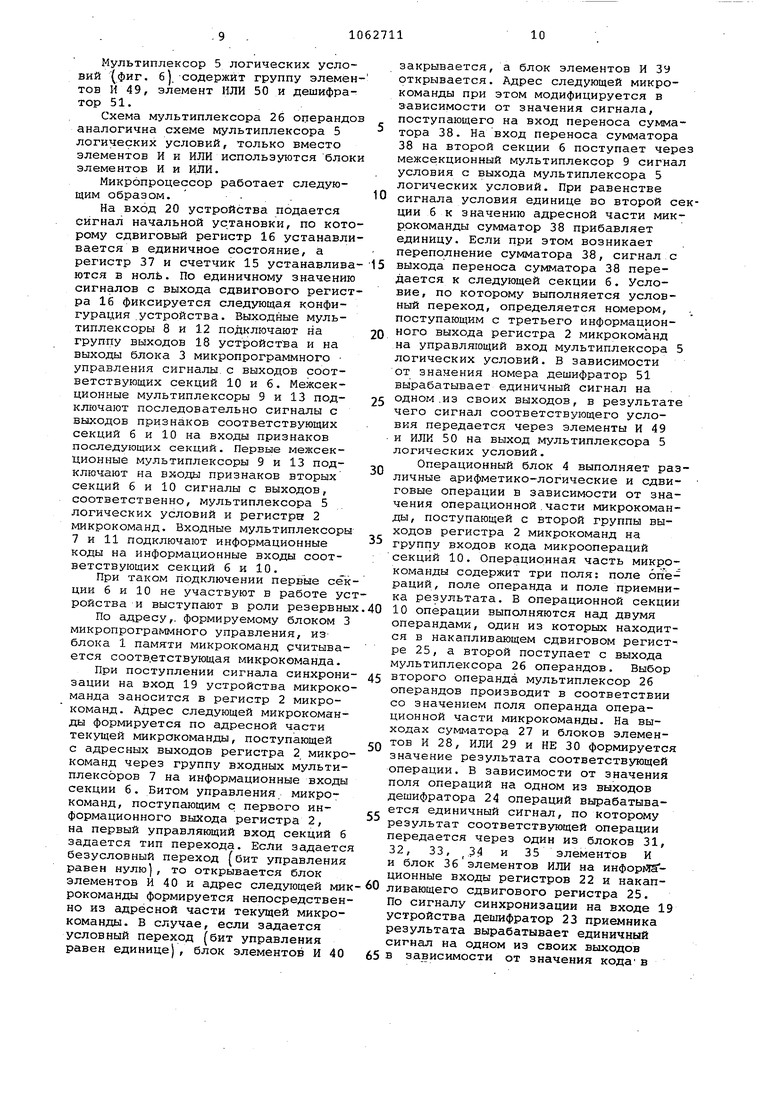

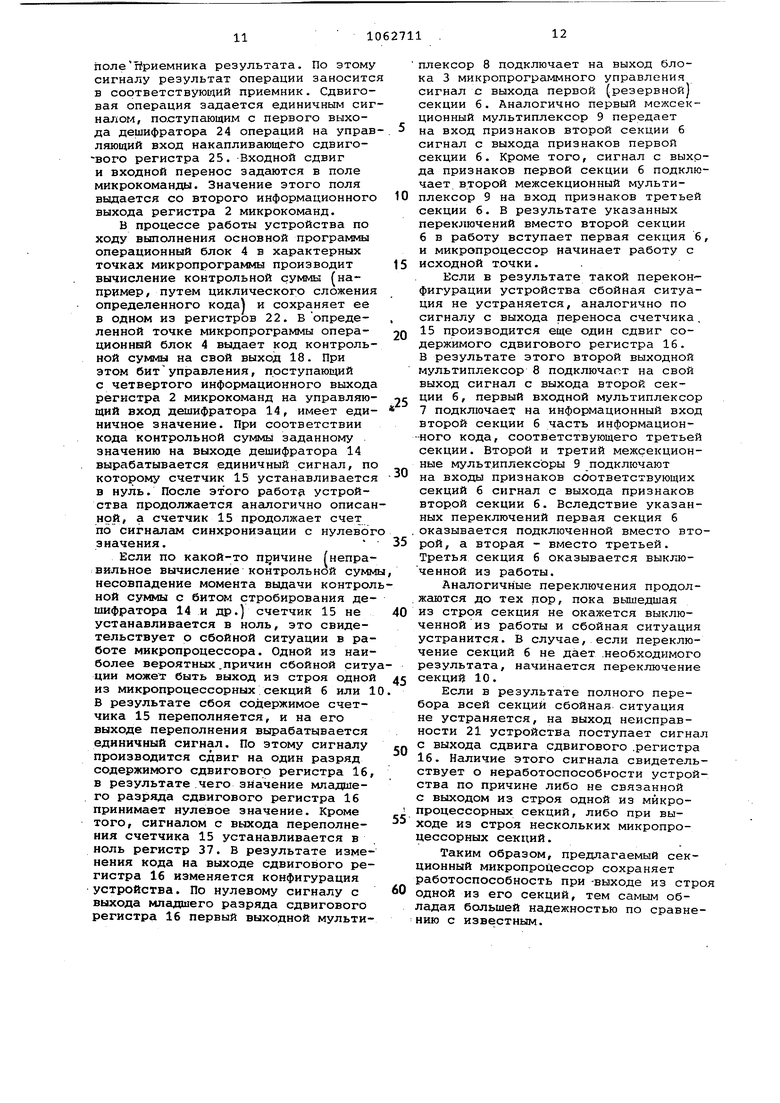

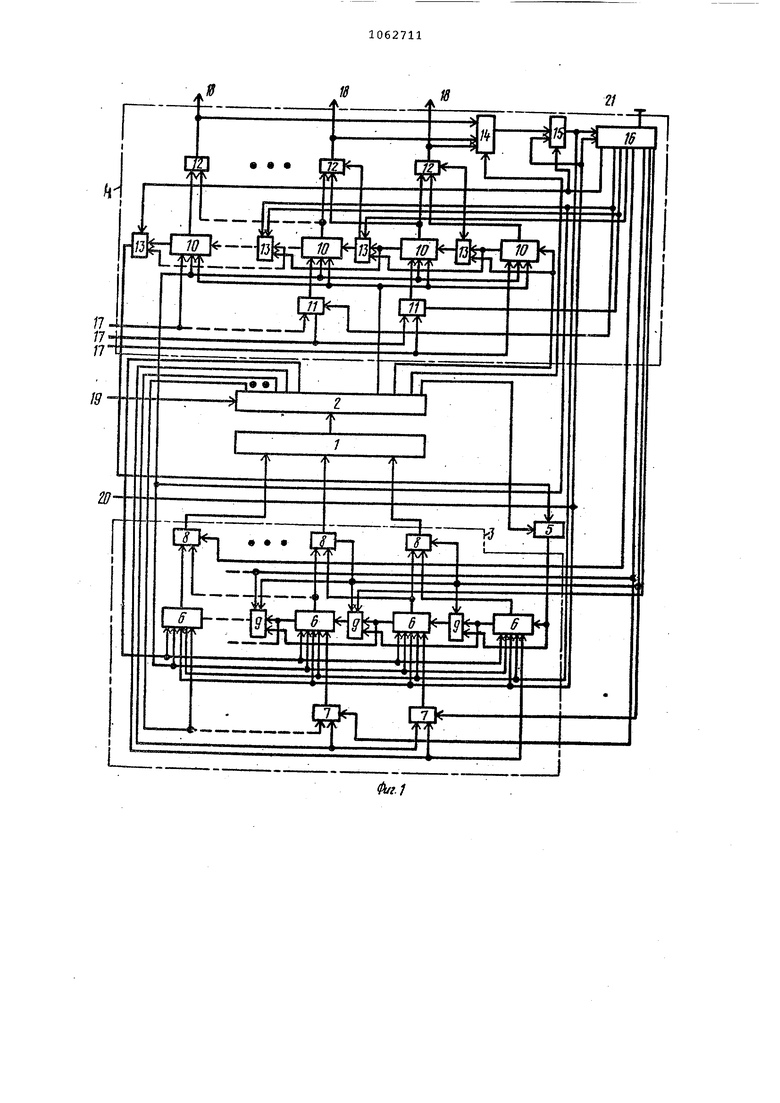

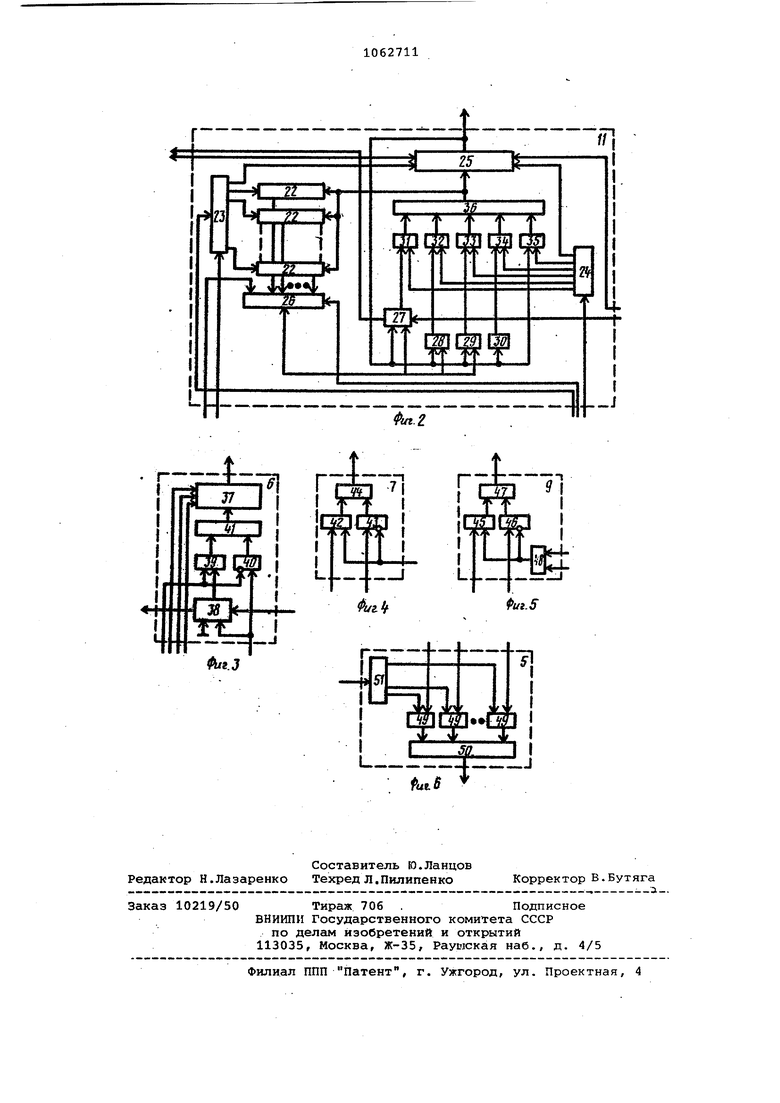

1 -го и второй -информационный вход каждого (4 +1)-го межсекционных мул.типлексоров операционного блока соединены с выходом признаков f -и операционной секции, второй информационный вход первого межсекционногд мультиплексора операционного блока соединен с входом признаков первой операционной секции, первый информационный вход ft -го межсекционного мультиплексора операционного блока соединен с выходом признаков f -и операционной секции, выход калодого k -го -( k -1,2,,,., -I ме хсек-ционного мультиплексора операционного блока соединен с входом признаков (k+l)-й операционной секции выход И -го межсекционного мультиплексора операционного блока соединен с информационным входом мультиплексора логических условий, выход каждого и -го входного мультиплексора операционного блока соединен с информационным входом (v+11-й операционной секции, первый информационный вход каясдого Hi -го (т-1,2, . . ., п -3) и второй информационный вход каждого ( tn+1)-го входных мультиплексоров операционного блока соединены с (m +1)-м входом группы информационных входов микропроцессора, второй информационный вход первого и первый информационный вход п-2)-го входных мультиплексоров операционного блока соединены соответственно с вторым и с (fi-1) -м входами группы информационных входов микропроцессора, выходы выходных мультиплексоров блока микропрограммного управления соединены с адресными входами блока памяти микрокоманд, первый информационный вход каждого -го и второй информационный вход каждого (-i +l) -го выходных мультиплексоров блока микропрограммного управления соединены с информационным выходом ( 1 +1)-и секции.микропрограммного управления, второй информационный вход первого выходного мультиплексора блока микропрограммного управления соединен с информационным выходом первой секции микропрограммного управления, первый информаци онный вход ( 11 выходного муль типлексора блока микропрограммного управления соединен с информационным выходом ц-и секции микропрограммного управления, управляющий вход каждого j -го выходного мульти плексора блока микропро граммного управления соединен с j -м выходом второй группы (п-1) информационных выходов сдвигового регистра, с перBfciM управляющим входом (j +1)-го межсекционного мультиплексора блока микропрограммного управления, с вторым управляющим входом j -го межсекционного мультиплексора блока микропрограммного уп{эавления и с управляющим входом (i -l)-го входного мультиплексора блока микропрограммного управления, управляющий вход первого выходного мультиплексора блока микропрограммного управления соединен с управляющим входом первого и с первым управляющим входом второго межсекционных мультиплексоров блока микропрограммного управления и с первым выходом второй группы (п -1) информационных выходов сдвигового регистра, управляющий вход ( выходного мультиплексора блока микропрограммного управления соединен с вторым управляющим входом (n-l)-ro межсекдионного мультиплексора блока микропрограммного управления, с управляющим входом ( входного мультиплексора блока микропрограммного управления и с (л-1)-м выходо второй группы {п-1) инфopIvlaциoнныx выходов сдвигового регистра, первый информационный вход i -го и второй информационный вход ( i +1)-го межсе ционцых мультиплексоров блока микро программного управления соединены с выходом признаков } -и секции, микропрограммного управления, второ информационный вход первого, и первый информационный вход ( Г) -1) -го межсекционных мультиплексоров блока микропрограммного управления соединены соответственно с входом прит знаков первой секции микропрограммного уп1:авления и с выходом призна ков (г1-1)-й секции микропрограммного управления, выход k -го межсекционного мультиплексора блока микропрограммного управления соединен с входом признака ( | +1 -и секции микропрограммного управления, выход каждого 1 -го входного мультиплексора блока микропрограммного управления соединен с информационным вхо дом ( +1)-й секции микропрограммного управления, первый информационный вход каждого rt} -го и второй информационный вход каждого (т+1)-г входных мультиплексоров блока микропрограммного управления соединены с /W+1J-M входом первой группы информационных выходов регистра микрокоманд, второй информационный первого и первый информационный входы входных мультиплексоров блока микропрограммного управления соединены соответственно с вторым и с ( входами первой группы информационных выходов регистра микрокоманд, выход дешифратора соединен с входом сброса счетчика, установочный вход которого соединен с входом начальной установки микропроцессора и с установочным входом сдвигового регистра, вход синхронизации которого соединен с третьими управляющими входами секций микропрограммного управления- и с выходом переполнения счетчика, счетный вход которого соединен с входом синхронизации микропроцессора, вход управления сдвигом и выход старшего разряда сдвигового регистра подключены соответственно к шине нулевого потенциала и к выходу неисправности микропроцессора . Кроме того, операционная секция состоит из дешифратора- приемника результата группы регистров общего назначения, мультиплексора операндов, сумматора, первого и второго блоков элементов ИЛИ, блока элементов НЕ, первого, второго, третьего, четвертого, пятого и шестого блоков элементов И, дешифратора операций, накапливающего сдвигового регистра, информационный вход которого соединен .с информационными входами группы регистров общего назначения выходом второго блока элементов ИЛИ, входы которого соединены соответственно с выходами первого, втоporo, третьего, четвертого и пятого блоков элементов И, первые входы которых соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами дешифратора операций , шестой выход которого соединен с управляющим входом накапливающего сдвигового регистра, вход синхронизации которого соединен с первым выходом дешифратора приемника результата, остальные выходы которого соединены с входами записи группы регистров общего назначения, группа информационных выходов соединена с группой информационных входов мультиплексора операндов, выход которого соединен с первым информационным входом сумг-iaTopa, с первыми входами шестого блока элементов И и первого блока элементов ИЛИ, вторые входы первого блока элементов ИЛИ, пятого и шестого блоков элементов И, второй информационный вход сумматора, вход блока элементов НЕ и Информационный вход накапливающего сдвигового регистра соединены с информационным входом операционной секции, вход переноса суглматора и вход, сдвига, накапливающего сдвигового регистра соединены с входом признаков операционной секции, выхо сумматора соединен с вторым входом первого блока элементов И, выход шестого блока элементов И соединен -с вторым входом второго блока элементов И, выход первого блока элементов ИЛИ соединен с вторым входом третьего блока элементов И, выход блока элементов КЕ соединен с вторь входом четвертого блока элементов И, вход дешифратора операций, управ ляющий- вход мультиплексора операндов, .вход дешифратора приемника результата соединены соответственно с входами группы входов кода микро операций операционной секции, инфор мационный вход мультиплексора oneрандов соединен с информационны./ входом процессорной секции, управляющий вход дешифратора приемника результата соединен с входом синхро низации процессорной секции, выход переноса сумматора и выход старшего разряда накапливающего сдвигового регистра соединены с выходом призна ков операционной секции. Причем .секция микропрограммного управления состоит из регистра, бло ка элементов ИЛИ, первого и второго блоков элементов И, сумматора, выход которого соединен с пepвы 1 вход первого блока элементов И, второй вход которого соединен с нулевым вх дом второго блока элементов И и с первым управляющим входом секции, .первый вход суглматора подключен к шине нулевого потенциала, второй . вход сумматора соединен с информаци онны входом секции и с единичным входом второго блока элементов И, выход которого подключен к первому входу блока элементов ИЛИ, второй вход которого соединен с выходом первого блока элементов И, выход блока элементов ИЛИ соединен с инфо мационным входом регистра, выход которого соединен с информационным выходом секции, вход установки в ед ницу, вход установки в ноль и вход синхронизации регистра соединены соответственно с вторым управляющим входом, с третьим управляющим входо и с входом синхронизации секции, вход и выход переноса сумматора соединены соответственно с входом и выходом признаков секции. При таком решении микропроцессор кроме основных рабочих секций, содержит одну резервную. В случае выхода из строя одной из рабочих секций, устройство самостоятельно обнаруживает вышедшую из строя сек цию и подключает вместо нее резерв ную. На фиг. 1 изображена схема устройства; на фиг. 2 - схема операционной секции} на фиг. 3 - схема секции микропрограммного управления; на фиг. 4 - схема входного мультиплексора; на фиг. 5 - схема межсекционного мультиплексора; на фиг. 6 схема мультиплексора логических условий. Микропроцессор содержит блок 1 памяти микрокоманд, регистр 2 микрокоманд, блок 3 микропрограммного управления, операционный блок 4, мультиплексор 5 логических условий. Блок- микропрограммного управления, включает группу секций б микропрограммного управления, группу входных 7, группу выходных 8 и группу межсекционных 9 мультиплексоров. Операционный блок 4 содержит группу операционных секций 10, а также группы входных 11, выходных 12 и межсекционных 13 мультиплексоров. Кроме того, микропроцессор содержит дешифратор 14, счетчик 15, сдвиговый регистр 16, группу информационных входов 17, группу информационных выходов 18, вход 19 синхро-низации, вход 20 начальной установки и выход 21 неисправности. Операционная секция 10 фиг. 2) содержит группу 22 регистров общего назначения, дешифратор 23 приемника результата, дешифратор 24 операций, накапливающий сдвиговый регистр 25, мультиплексор 26 операндов, сумматор 27, шестой блок 28 элементов И, первый блок 29 элементов ИЛИ, блок 30 элементов НЕ, первый 31, второй 32, третий 33, четвертый 34, пятый 35 блоки элементов И, второй 36 блок элементов ИЛИ. Секция 6 микропрограммного управления (фиг. 3) содержит регистр 37, суматор 38, второй 39 и первый 40 блоки элементов И, блок 41 элементов ИЛИ. Входной мультиплексор 7, схема которого показана на фиг. А, содержит первый 42 и второй 43 блоки элементов И, блок 44 элементов ИЛИ. Схема входного мультиплексора 11 и схемы выходных мультиплексоров 8 и 12 аналогичны схеме входного мультиплексора 7. Мел секционный мультиплексос У (фиг. 5) содержит первый 45 и второй 46 блоки элементов И, блок 47 элементов ИЛИ и блок 48 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Схема межсекционного мультиплексора 13 аналогична схеме межсекционного мультиплексора 9. Схемы первого и последнего межсекционного мультиплексоров 13 и первого межсекционного мультиплексора 9 аналогичны схеме входного мультиплексора 7. Мультиплексор 5 логических условий (фиг. б, содержит группу элемён тов Н 49, элемент ИЛИ 50 и дешифратор 51. Схема мультиплексора 26 оцерандо аналогична схеме мультиплексора 5 логических условий, только вместо элементов И и ИЛИ используются блок элементов И и ИЛИ. Микропроцессор работает следующим образом. . . На вход 20 устройства подается сигнал начальной ус.тановки, по кото рому сдвиговый регистр 16 устанавли вается в единичное состояние, а регистр 37 и счетчик 15 устанавлива ются в ноль. По единичному значению сигналов с выхода сдвигового регист ра 16 фиксируется следующая конфигурация .устройства. Выходные мультиплексоры 8 и 12 подключают на группу выходов 18 устройства и на выходы блока 3 микропрограммного управления сигналы.с выходов соответствующих секций 10 и 6. Межсекционные мультиплексоры 9 и 13 подключают последовательно сигналы с выходов призна.ков соответствующих секций 6 и 10 на входы признаков последующих секций. Первые межсекционные мультиплексоры 9 н 13 подключают на входы признаков вторых секций 6 и 10 сигналы с выходов, соответственно, мультиплексора 5 логических условий и регистра 2 микрокоманд. Входные мультиплексоры 7 и 11 подключают информационные коды на информационные входы соответствующих секций 6 и 10. При таком подключении первые сёк ции 6 и 10 не участвуют в работе ус ройства и выступают в роли резервны По адресу,, формируемому блоком 3 микропрограммного управления, из блока 1 памяти микрокоманд считывается соответствующая микрокоманда. При поступлении сигнала синхрони зации на вход 19 устройства микроко манда заносится в регистр 2 микрокоманд. Адрес следующей микрокоманды формируется по адресной части текущей микрокоманды, поступающей с адресных выходов регистра 2 микро команд через группу входных мультиплексоров 7 на информационные входы секции 6. Битом управления, микрокоманд, поступающим с первого информационного выхода регистра 2, на первый управляющий вход секций 6 задается тип перехода. Если задаетс безусловный переход (бит управления равен нулю, то открывается блок элементов И 40 и адрес следующей ми рокоманды формируется непосредствен но из адресной части текущей микрокоманды. В случае, если задается условный переход (бит управления равен единице), блок элементов И 40 закрывается, а блок элементов И ЗУ открывается. Адрес следующей микрокоманды при этом модифицируется в зависимости от значения сигнала, поступающего на вход переноса сумматора 38. На вход переноса сумматора 38 на второй секции 6 поступает через межсекционный мультиплексор 9 сигнал условия с выхода мультиплексора 5 логических условий. При равенстве сигнала условия единице во второй секции 6 к значению адресной части микрокоманды сумматор 38 прибавляет единицу. Если при этом возникает переполнение сумматора 38, сигнал с выхода переноса сумматора 38 передается к следующей секции 6. Условие, по которому выполняется условный переход, определяется номером, поступающим с третьего информационного выхода регистра 2 микрокоманд на управляющий вход мультиплексора 5 логических условий. В зависимости от знамения номера дешифратор 51 вырабатывает единичный сигнал на одном .из своих выходов, в результате чего сигнал соответствующего условия передается через элементы И 49 и ИЛИ 50 на выход мультиплексора 5 логических условий. Операционный блок 4 выполняет различные арифметико-логические и сдвиговые операции в зависимости от значения операционной.части микрокоманды, поступающей с второй группы выходов регистра 2 микрокоманд на группу входов кода микроопераций секций 10. Операционная часть микрокоманды содержит три поля: поле операций, поле операнда и поле приемника результата. В операционной секции 10 операции выполняются над двумя операндами, один из которых находится в накапливающем сдвиговом регист ре 25, а второй поступает с выхода мультиплексора 26 операндов. Выбор второго операнда мультиплексор 26 операндов производит в соответствии со значением поля операнда операционной части микрокоманды. На выходах сумматора 27 и блоков элементов И 28, ИЛИ 29 и НЕ 30 формируется значение результата соответствующей операции. В зависимости от значения поля операций на одном из выходов дешифратора 24 операций вырабатывается единичный сигнал, по которому результат соответствующей операции передается через один из блоков 31, 32, 33, 34 и 35 элементов И и блок 36 элементов ИЛИ на инфорйЗ ционные входы регистров 22 и накапливающего сдвигового регистра 25. По сигналу синхронизации на входе 19 устройства дешифратор 23 приемника результата вырабатывает единичный сигнал на одном из своих выходов в зависимости от значения кодав

полейриемника результата. По этому сигналу результат операции заноситс в сортветствуюодий приемник. Сдвиговая операция задается единичным сигналом, поступающим с первого выхода дешифратора 24 операций на управляющий вход накапливающего сдвиго-вого регистра 25. Входной сдвиг и входной перенос задаются в поле микрокоманды. Значение этого поля вьщается со второго информационного выхода регистра 2 микрокоманд.

В процессе работы устройства по ходу выполнения основной программы операционный блок 4 в характерных точках микропрограммы производит вычисление контрольной суммы (например, путем циклического сложения определенного кода) и сохраняет ее в одном из регистров 22. вопределенной точке микропрограммы операционный блок 4 выдает код контрольной суммы на свой выход 18. При этом бит управления, поступающий с четвертого информационного выхода регистра 2 микрокоманд на управляющий вход дешифратора 14, имеет единичное значение. При соответствии кода контрольной суммы заданному значению на выходе дешифратора 14 вырабатывается единичный сигнал, по которому счетчик 15 устанавливается в нуль. После этого pa6oTfi устройства продолжается аналогично описанной, а счетчик 15 продолжает счет по сигналам синхронизации с нулевог значения.

Если по какой-то причине (неправильное вычисление контрольной сумм несовпадение момента выдачи контрол ной суммы с битом стробирования дешифратора 14 и др.) счетчик 15 не устанавливается в ноль, это свидетельствует о сбойной ситуации в работе микропроцессора. Одной из наиболее вероятных.причин сбойной ситу ции может быть выход из строя одной из микропроцессорных секций б или 1 В результате сбоя содержимое счетчика 15 переполняется, и на его выходе переполнения вырабатывается единичный сигнал. По этому сигналу производится сдвиг на один разряд содержимого сдвигового регистра 16, в результате чего значение младшего разряда сдвигового регистра 16 принимает нулевое значение. Кроме того, сигналом с выхода переполнения счетчика 15 устанавливается в ноль регистр 37. В результате изменения кода на выходе сдвигового регистра 16 изменяется конфигурация устройства. По нулевому сигналу с выхода младшего разряда сдвигового регистра 16 первый выходной мультиплексор 8 подключает на выход блока 3 микропрограг 1много управления сигнал с выхода первой (резервной) секции б. Аналогично первый межсекционный мультиплексор 9 передает на вход признаков второй секции б сигнал с выхода признаков первой секции б. Кроме того, сигнал с выхода признаков первой секции б подключает второй межсекционный мультиплексор 9 на вход признаков третьей секции б. В результате указанных переключений вместо второй секции

6в работу вступает первая секция б, и микропроцессор начинает работу с исходной точки.

Если в результате такой переконфигурации устройства сбойная ситуация не устраняется, аналогично по сигналу с выхода переноса счетчика. 15 производится еще один сдвиг содержимого сдвигового регистра 16. В результате этого второй выходной мультиплексор 8 подключает на свой выход сигнал с выхода второй секции б, первый входной мультиплексор

7подключает на информационный вход второй секции б часть информацион-ного кода, соответствующего третьей секции. Второй и третий межсекционные мультиплексоры 9 подключают на входы признаков соответствующих секций б сигнал с выхода признаков второй секции б. Вследствие указанных переключений первая секция б

. оказывается подключенной вместо второй, а вторая - вместо третьей. Третья секция б оказывается выключенной из работы.

Аналогичные переключения продол.жаются до тех пор, пока вышедшая из строя секция не окажется выключенной из работы и сбойная ситуация устранится. В случае, если переключение секций б не дает .необходимого результата, начинается переключение секций 10.

Если в результате полного перебора всей секций сбойная ситуация не устраняется, на выход неисправности 21 устройства поступает сигнал с выхода сдвига сдвигового .регистра

0 16. Наличие этого сигнала свидетельствует о неработоспособности устройства по причине либо не связанной с выходом из строя одной из микропроцессорных секций, либо при выходе из строя нескольких микропроцессорных секций.

Таким образом, предлагаемый секционный микропроцессор сохраняет работоспособность при -выходе из строя одной из его секций, тем самым обладая большей надежностью по сравнению с известным.

.

.В

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| „Elektronic Design ,.1978, V | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| „EDN , 1978, V | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1983-12-23—Публикация

1982-05-28—Подача