мента ИЛИ, выход которого подключен к входам управления сдвигом регистра множителя и регистра произведения и Информационному входу счетчика циклов, выход счетчика количества буферных регистров подключен к первому информационному входу третьей схемы сравнения и к управляющему входу коммутатора, информационный вход которого соединен с BTOJXJM выходом регистра множимого, а выходы подключены к информационным входам буферных регистров, выходы которых соединены с информационными входами сумматора с третьего по U-ый соответственно, второй вход третьей схемы сравнения подключен к входу эначе ния 2-1 устройства, выход первого элемента ИЛИ блока управления подключен к управляющему входу второй схемы сравнения, второй выход которой подключен к второму входу первого элемента И блока управления, выход которого соединен с первым входом второго элемента ИЛИ блока управления, выход которого соединен с управляющим входом узла выдачи разряда и входом третьего элемента задержки блока управления, выход которого соединен с первым входом четвертого элемента И блока управления и через четвертый элемент задержки блока управления подключен к первым входам пятого и шестого элементов И блока управления, первый и второй выходы третьей cxcNtti сравнения соединены с вторыми входами шестого и пятого элементов И блока управления соответственно, выход пятого элемента И блока управления соединен с первым входом управления чтением регистра множимого и через пятый элемент задержки блока управления подключен к информационным входам счетчика тактов и счетчика количества буферных регистров и входу шестого элемента задержки блока управления, выход которого подключен к второму входу второго элемента ИЛИ блока управления, второй вход четвертого элемента И блока управления соединен с первым выходом первой схег«л сравнения, второй выход

которой подключен к управляющему входу третьей схемы сравнения, выход шестого элемента И блока управления соединен с первым входом третьего элемента ИЛИ блцра управления и чере седьмой элемент задержки блока управ,Пленяя подключен к первым входам четвертого и пятого элементов ИЛИ блока управления и входу восьмого элемента задержки блока управления, выход которого подключен к третьему входу второго элемента ИЛИ блока управления, выход четвертого элемента И блока управления подключен к входу девятого элемента задержки блока управления и второму входу третьего элемента ИЛИ блока управления, выход которого соединен с вторыми входами управления чтением регистра произведения и регистра множимого и входами управления чтением буферных регистров, выход девятого элемента задержк блока управления соединен с входом десятого элемента задержки блока управления и вторым входом четвертого элемента ИЛИ блока управления, выход которого подключен к управляющему входу счетчика количества буферных регистров, выход десятого элемента задержки блока управления соединен а вторым входом элемента ИЛИ и первЕлм входом шестого элемента ИЛИ блока управления, выход которого подключен к вторым входам второго и третьего элементов И блока управления, второй вход шестого элемента ИЛИ блока управления подключен к выходу второго элемента задержки блока управления, вход запуска устройства соединен с третьим входом четвертого элемента ИЛИ блока управления и первым входом седьмого элемента ИЛИ блока управления, второй вход которого соединен с выходом девятого элемента задержки и вторым входом пятого элемента ИЛИ блока управления, выход седьмого элемента ИЛИ блока управления подключен к управляющему входу счетчика тактов, выход пятого элемента ИЛИ блока управления соединен с входами управления записью буферных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU920705A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1984 |

|

SU1185328A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

| Устройство для умножения | 1990 |

|

SU1789981A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ В ПОЗИЦИОННОЙ ИЗБЫТОЧНОЙ (f, К) -СИС ТЕМЕ СЧИСЛЕНИЯ, содержащее регистр множимого, регистр множителя, регистр произведения, сумматор, счетчик Циклов, счетчик тактов, блок информационной разгрузки, узел выдачи разряда, первую схему сравнения и блок управления, содержшций первый, второй и третий элементы И, первый элемент ИЛИ и первый, второй и третий элементы задержки, причем первые выходы регистра множимого и регистра произведения соединены с первым и вторым информационными входами сумматора соответственно, первый информационный вход регистра произве дения соединен с выходом сумматора, второй выход регистра произведения соединён с информационным входом блока информационной разгрузки, выход младшего разряда регистра множителя соединен с информационным входом узла выдачи разряда, выход кото рого соединен с первым входом, первой схемы сравнения, второй вход которой подключен к выходу счетчика тактов, вход запуска устройства соединен с управляющим входом счетчика циклов, выход признака равенства нулю которого соединен с управляющим входом блока информационной разгрузки,вход запуска устройства через первый элемент задержки блока управления подключен к первому входу первого элемента ИЛИ блока управления, выход которого через второй элемент заде)жки блока управления подключен к первому входу первого элемента И блока управления, выход признака неравенства нулю счетчика циклов подключен к первому входу второго элемента И блока управления, выход которого подключен к второму входу первого элемента ИЛИ блока управления, выход признака равенства нулю счетчика циклов подключен к первому входу третьего элемента И блока управления , выход которого соединен с первым входом управления чтением регистра произведения, информационный выход блока информационной разгрузки соединен с вторым информационным входом регистра произведения,выход признака окончания разгрузки блока ин3d формационной разгрузки подключен к ходу признака окончания работы устрой ства, отл и. чающееся тем, 4 что, с целью повышения быстродей ствия, при t 2, где (.K-rM)j эо в устройство введены коммутатор,

Изобретение относится к области вычислительной техники и может быть использовано при построе нии арифметических устройств ЦВМ.

Известно устройство для умножения чисел с фикЬированной запятой в по иционной системе счисления, содержащее

регистры множимого и множителя, регистр произведения, сумматор, блок управления, причем выходы регистров множимого и произведения соединены с входами сукматора, выход которого соединен с входом регистра произведения СП . Это устройство не позволяет выпол нять операцию умножения чисел с фиксированной запятой в позиционных избыточных (г, k- - системах счислени, использование которых позволяет повышать быстродействие операционных устройств за счет исключения перенос через несколько разрядов при суммиро вании, ввиду того, что его структура и принцип действия не учитывают специфики представления в таких система счисления чисел с фиксированной запя той .. Наиболее близким по технической сущности к предложенному является 1устиЬйство для умножения чисел в позиционной избыточной (г, k) - системе счиления, содержащее регистр множимого, регистр множителя, регистр произведения, сукниатор, блок управлентля причем информационные входы сумма:бора соединены с выходом регистра множимого и первым выходом регистра произведения, первый информационный вход которого соединен с выходом сумматора, блок информационной разгрузки, реверсивный счетчик циклов, счетчик тактов, схему сравне ния количества тактов, узел выдачи разряда причем второй выход регистра произведения соединен с информационным входом блока информационной разгрузки выхсщ младшего разряда регистра множителя соединен с информационным вхо дом узла выдачи разрядов, управляющий вход которого соединен с первым выходом блока управления, а выход соединен с первым входом схемы сравнения количества тактов, второй вход которой соединен с выходом счетчика тактов, первый выход схемы сравнения количества тактов соединен с управля ющим входом регистра множимого, первым управляющим входом регистра произведения и первым входом блока управления, второй выход которого соединен с управляющим входом cyi iaTopa второй и третий управляющие входы ре гистра произведения соединены соответственно с третьим и четвертым выходами блока управления, второй выхрд схемы сравнения количества тактов со единен с управляющим входом регистра множителя, четвертым управляющим вхо дом регистра произведения и первым вхрдсм счетчика тактов, второй и тре тий входы которого соединены соответ ственно с пятым и шестым выходами блока управления, седьмой выход кото рого соединен с первым входом реверсивного счетчика циклов, второй вход которого соединен с вторым выходом схемы сравнения количества тактов, первый, второй, и третий выходы реверсивного счетчика циклов соединены соответственно с вторым и третьим входами блока управления и управляющим входом блока информационной разгрузки, информационный и управляющий выходы которого соединены соответственно с вторым инфоБмационным входом регистра произведения и четвертым входс 1 блока управления, пятый вход которого соединен с управляющим входом устройства, выход индикации которого соединен с восьмым выходом блока управления, причем блок управления содержит усилители-формирователи,элементы И, ИЛИ и задержки, причем вход первого усилителя-формирователя соединен с пятым входом блока, а выход - с вторым, третьим, пятым, седьмым выходами блока и входом первого элемента задержки, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с -первым выходом блока, и входом второго элемента задержки, выход которого соединен с первыми входами первого, второго и третьего элементов- И, вторые входы которых соединены соответственно с 1первым, вторым и третьим выходами блока, выход первого элемента И соединен с шестым выходом блока и че рез третий элемент задержки - с вторым входом элемента ИЛИ, третий вхрд которого соединен с выходом второго элемента И, выход третьего элемента И соединен с четвертым выходом блока, четвертый вход которого соединен с входом второго усилителя-формирователя, выход которого соединен с восьмым выходом блока С21. Недостатком этого устройства является невысокое быстродействие: при получении сумм частичных произведений выполняется суммииование только двух операндов-регистров множимого и произведения. Пусть .в разряде множителя на некотором л. -том такте выполнения операции умножения записана цифра dl. 2. Это значит, что для получения частичного произведения на этом такте Нсшо просуммировать содержимое регистра множимого с содержимым регистра произведения последовательно оСд, раз. Цель изобретения - повыпение быстродействия. Поставленная цель достигается . тем, что в устройство для умножения в позиционной избыточной ( rj К)системе счисления, содержащее регистр множимого, регистр множителя, регистр произведения, сумматор, счетчик циклов, счетчик тактов, блок информационной разгрузки, узел выдачи разряда, первую схему сравнения и блрк управления, содержащий первый, второй и третий элементы И, первый элемент ИЛИ и первый, второй и третий элементы задержки, причем первые выходы регистра множимого и регистра произведения соединены с первым и

вторым информационными входами сумматора соответственно, первьлй информационный вход регистра произведения еоешинен с выходом сумматора, второй выход регистра произведения соединен с информационным входом блока информационной раггрузки, выход младшего разряда регистра множителя соединен с информационным входом узла выдачи разряда, выход которого соединен с первым входом первой схемы сравнения второй вход которой подключен к выходу счетчика тактов, вход запуска устройства соединен с управляющим входом счетчика циклов, выход приз нака равенства нулю которого соединен с управляющим входом блока информационной разгрузки, вход запуска устройства через первый элемент задержки блока управления подключен к первому входу первого элемента ИЛИ блока управления, выход которого через второй элемент задержки блока управле- ния подключен к первому входу первого элемента И блока управления, выход признака неравенства нулю счетчика диклов подключен к первому ,входу второго элемента И блока управления, выход которого подключен к второму входу первого элемента ИЛИ блока управления, выход признака равенства нулю счетчика циклов подключен к входу третьего элемента И блока Управления, выход которого соединен с первым входом управления чтениемрегистра произведения, информационный выход блока информационной разгрузки соединен с вторым информационным входом регистра произведения выход признака окончания разгрузки блока информационной разгрузки подключен к выходу признака окончания работы устройства,введены коммутатор (12-2) буферных регистров, вторая и третья схемы сравнения, элемент ИЛИ, счетчик количества буферных регистров , а в блок управления введены шесть элементов ИЛИ, три элемента И и семь элементов задержки, причем выход младшего разряда регистра множителя подключён к первому информационному входу второй схемы сравнения, второй информационный вход которой подключен ко входу значения О устройства, а первый вход соединен с первым входом элемента ИЛИ, выход которого подключен к входам управления сдвигом регистра множителя и регистра произведения и информационному входу счетчика циклов, выход счетчика количества буферных регистров подключен к первому информационному входу третьей схемы сравнения и к управляющему входу коммутатора, информационный вход которого соединен -с вторым выходом регистра множимого, а выходы подключены к информационным входам

буферных регистров, выходы которых соединены с информационными входами сумматора с третьего по -ый соответственно, второй вход третьей схемл сравнения подключен к входу значения &-1 устройства, выход первого элемента ИЛИ блока управления подключен к управляющему входу вторйй схемы сравнения, второй выход которой подключен к второму входу первого элемента И блока управления, выход которого соединен с первым входом второго элемента ИЛИ блока управления, выход которого соединен с управляющим входом узла выдачи разряда и .. входом третьего .элемента задержки блока управления, выход которого соединен с первым входом четвертого элемента И блока управления и через четвертый элемент задержки блока управления подключен к первым входам пятого и шестого элементов И блока управления, первый и второй выходы третьей схема сравнения соединены с вторыми входами шестого и пятого элементов И блока управления соответственно, выход пятого элемента И блока управления соединен с первым входом управления чтением регистра множимог и через пятый элемент задержки блока управления подключен к информационным входам счетчика тактов и счетчика количества буферных регистров и входу шестого элемента задержки блока управления, выход которого подключен к второму входу второго элемента ИЛИ блока управления, второй вход четвертого элемента И блока управления соединен с первым выходом первой схемы сравнения, второй выход которо подключен к управляющему входу третьей схемы сравнения, выход шестого элемента И блока управления соединен с первым входом третьего элемента ИОД блока управления и через седьмой элемент задержки блока управления подключен к первым входам четвертого и пятого элементов ИЛИ блока управления и входу восьмого элемента задержки блока управления, выход которого подключен к третьему входу второго элемента ИЛИ блока управления , выход четвертого элемента И блока управления подключен к входу девятого элемента задержки блока управления и второму входу третьего элемента ИЛИ блока управления, выход которого соединен с вторыми входами управления чтением регистра пронэведения и регистра множимого и входами управления чтением буферных регистров, выход девятого элемента задержки блока управления соединен с входом десятого элемента задержки блока управления и входом четвертого элемента ИЛИ блока управления, выход которого подключен к управляющему

входу-счетчика количества буферных регистров, выход десятого элемента задержки блока управления соединен с вторым входом элемента ИЛИ и первым входом шестого элемента ИЛИ блок управления, выход которого подключен к вторым входам второго и третьего элементов И блока управления, второй вход шестого элемента ИЛИ блока управления подключен к вых.сщу второго элемента задержки блока управления, вход запуска устройства соединеи с третьим входом четвертого элемента ИЛИ блока управления и первым входом седьмого элемента ИЛИ блока управления, второй вход котороге соединен с выходом девятого элемента задержки и вторым входсш пятого элемента ИЛИ блока управления выход седыиюго элемента ИЛИ блока управления подключен к управляющему входу счетчика тактов, выход пятого элемента ИЛИ блока управления соединен с входами управления записью буферных регистров.

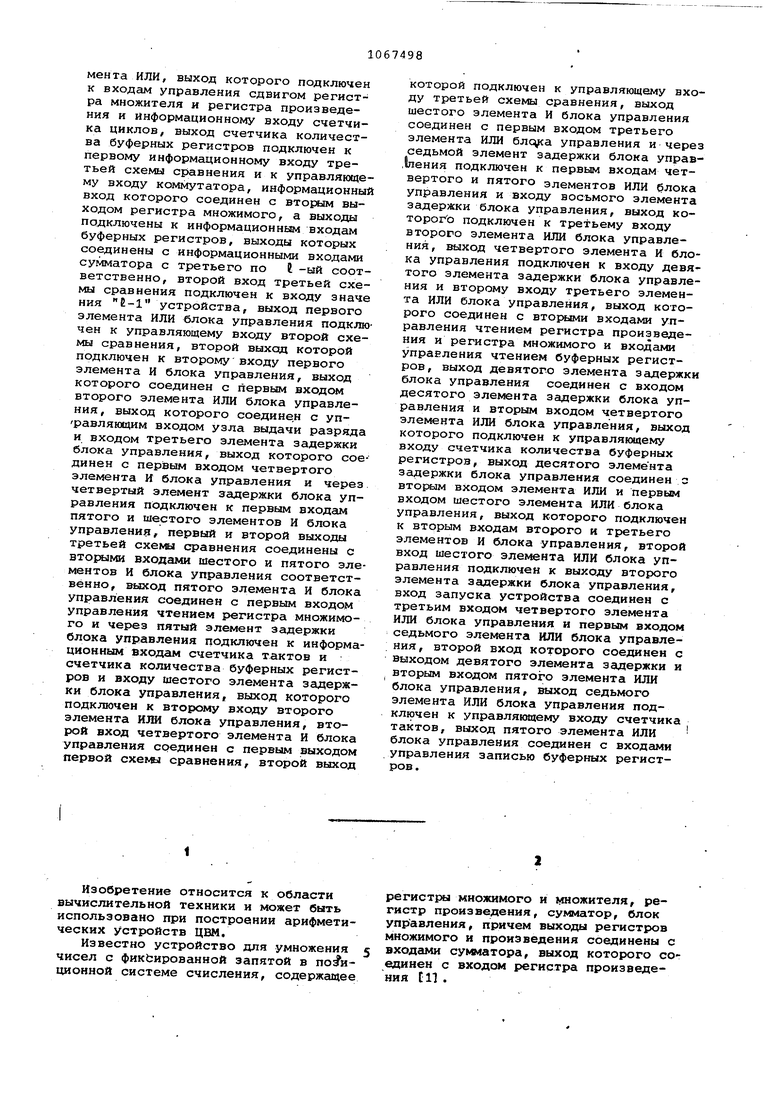

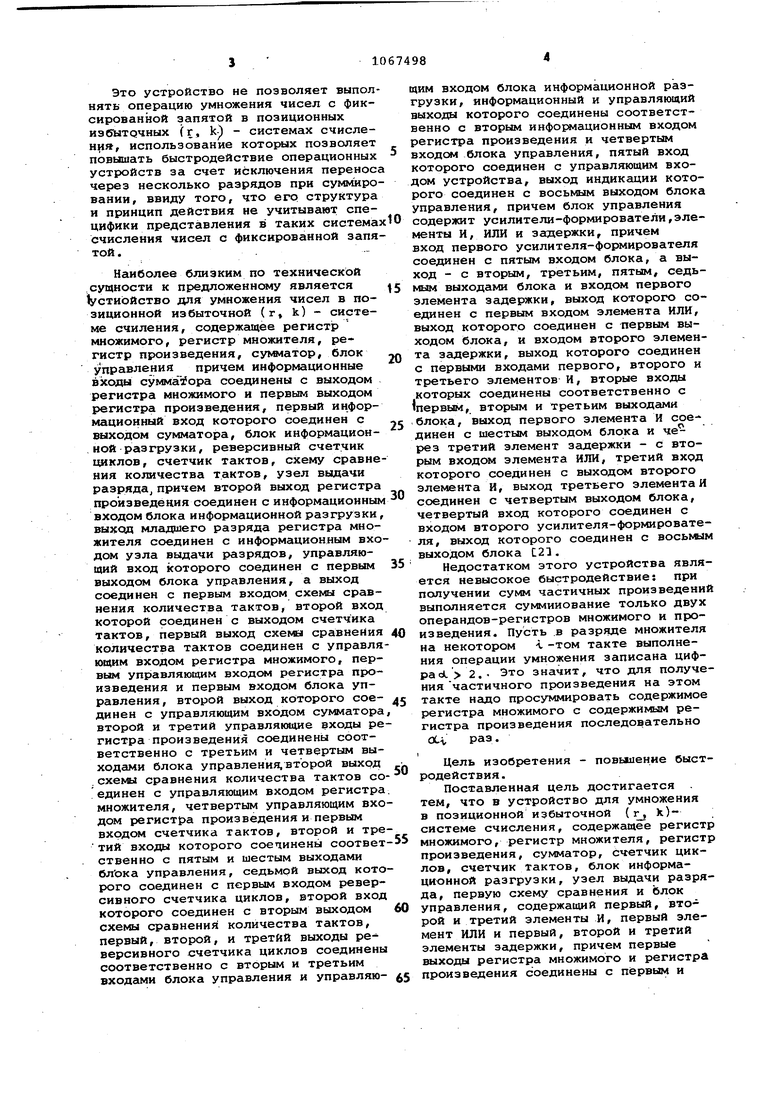

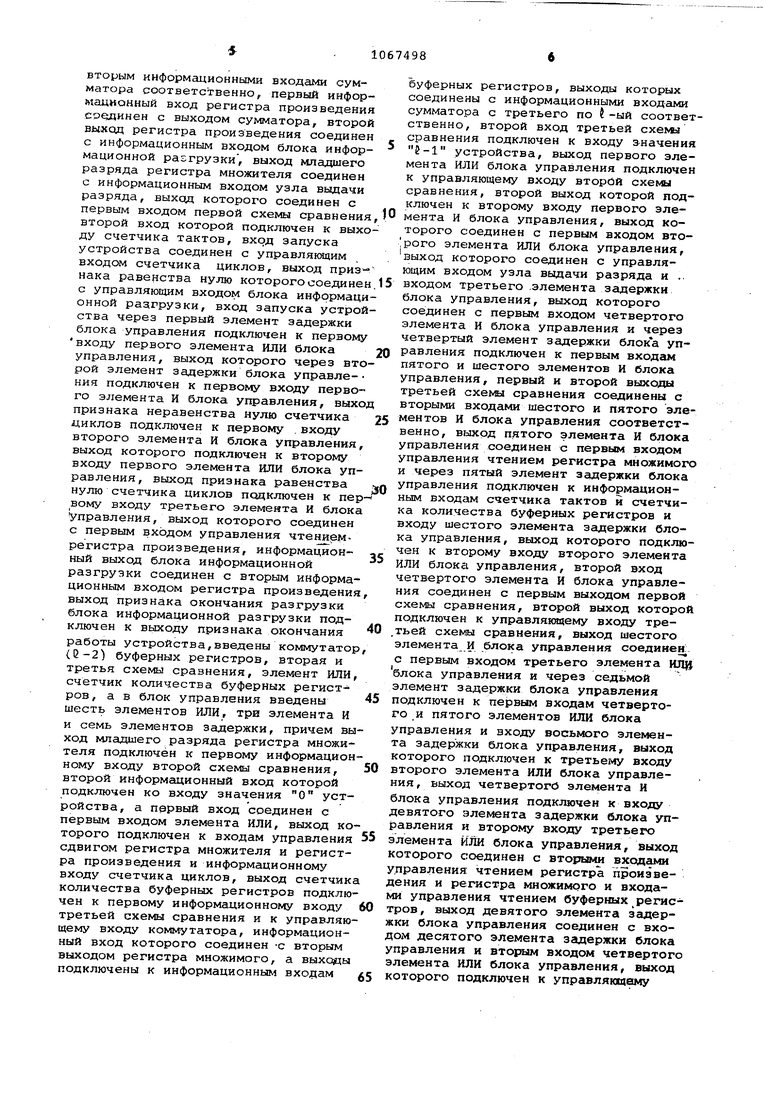

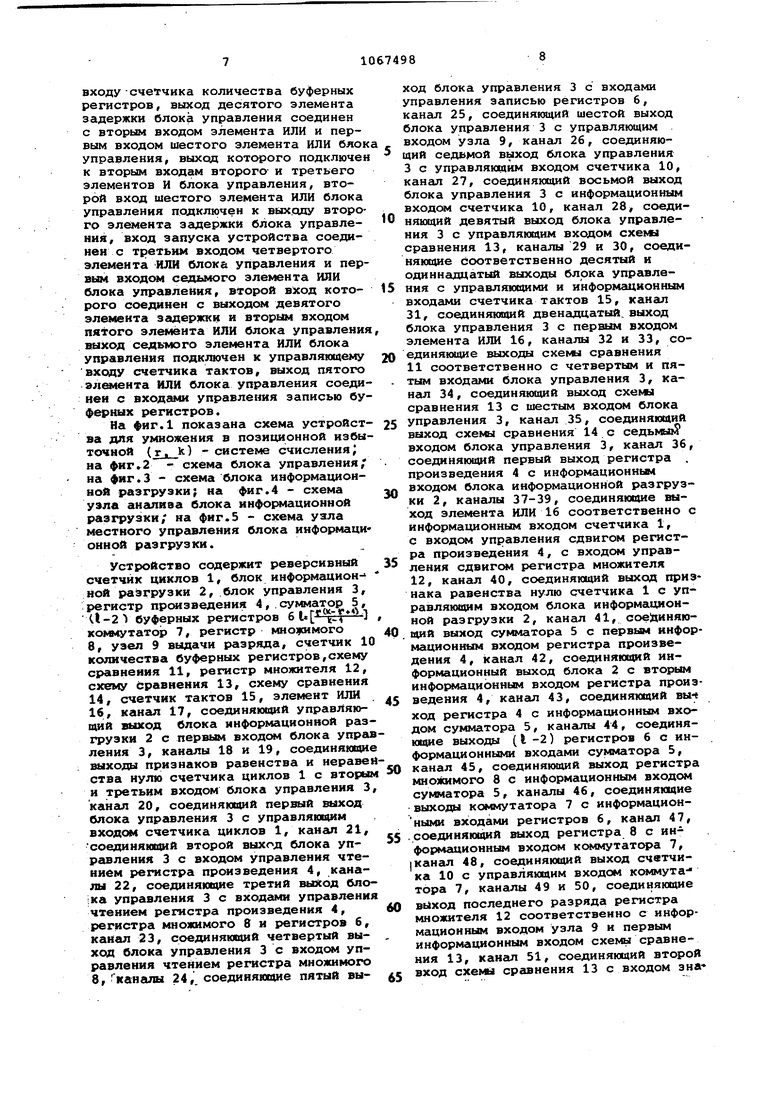

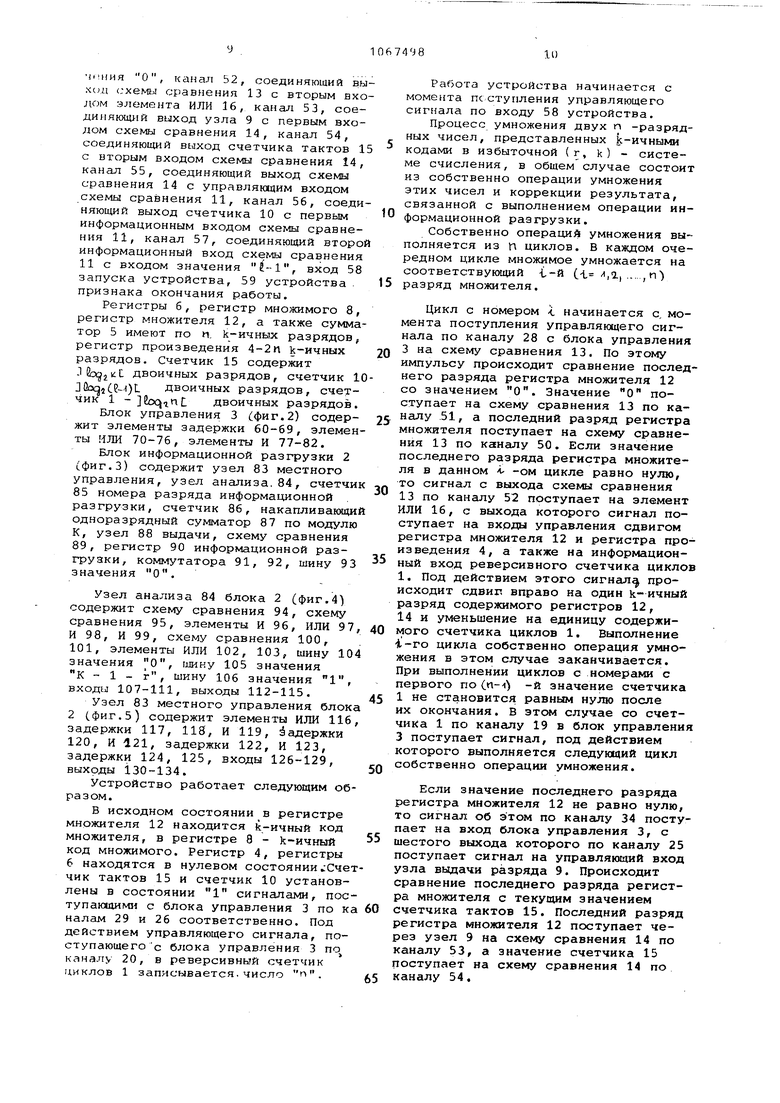

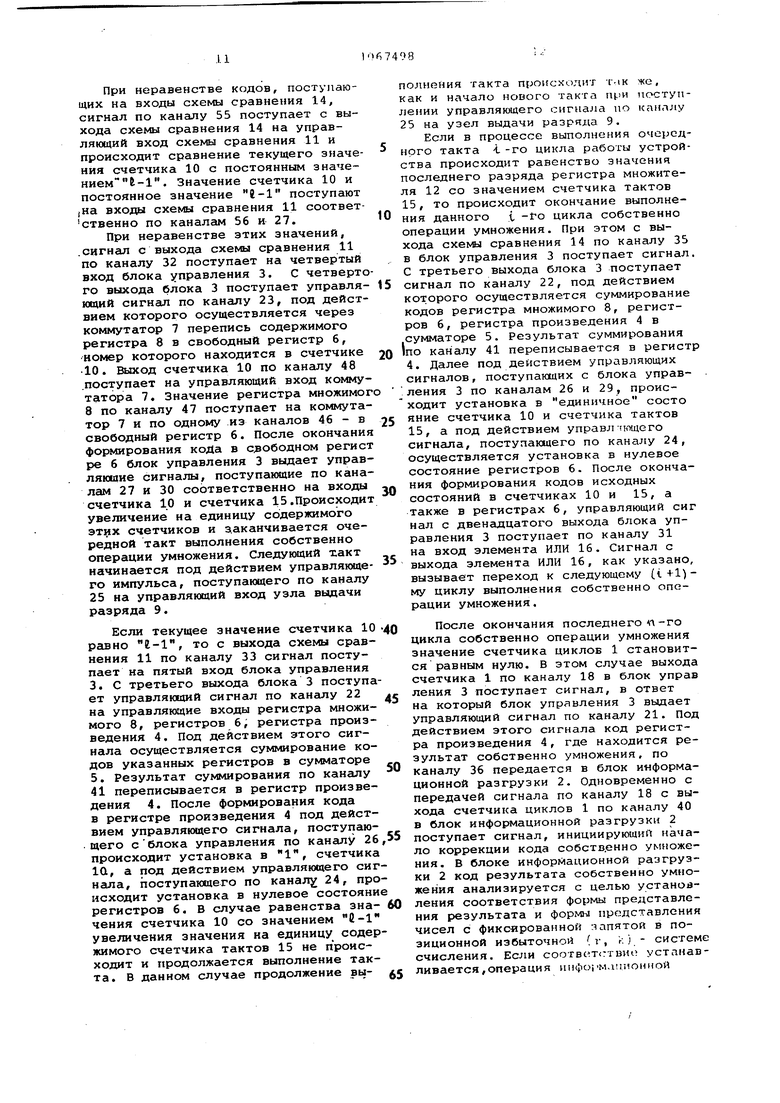

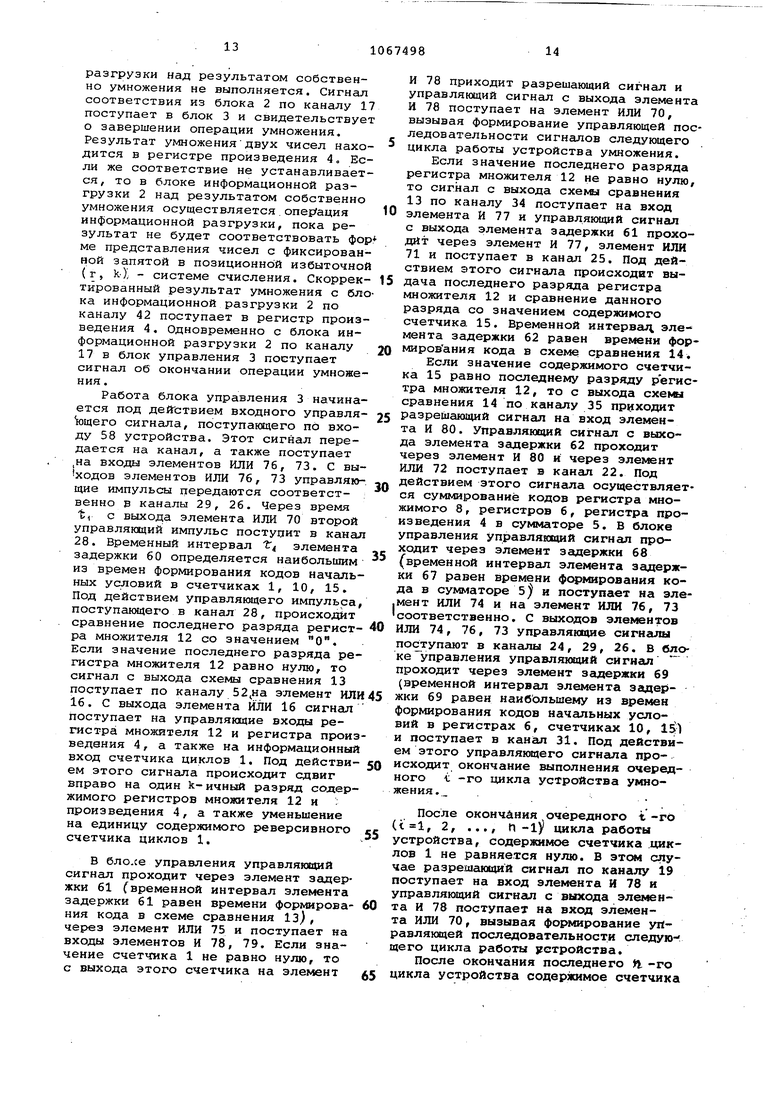

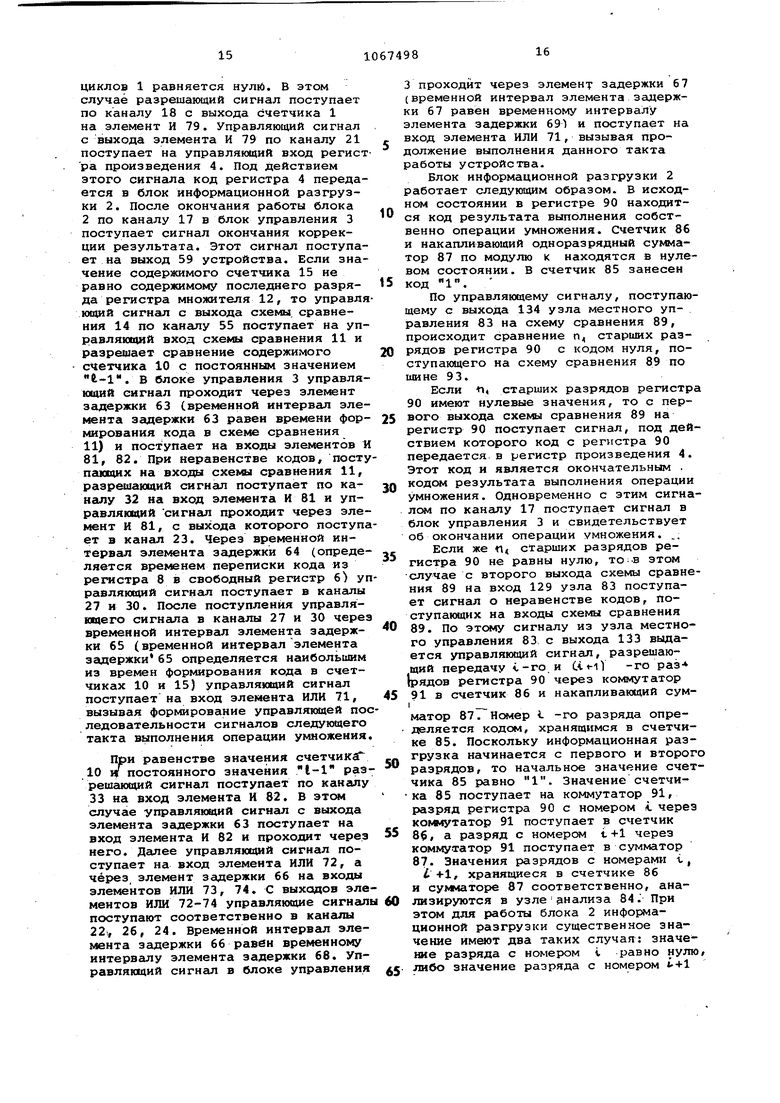

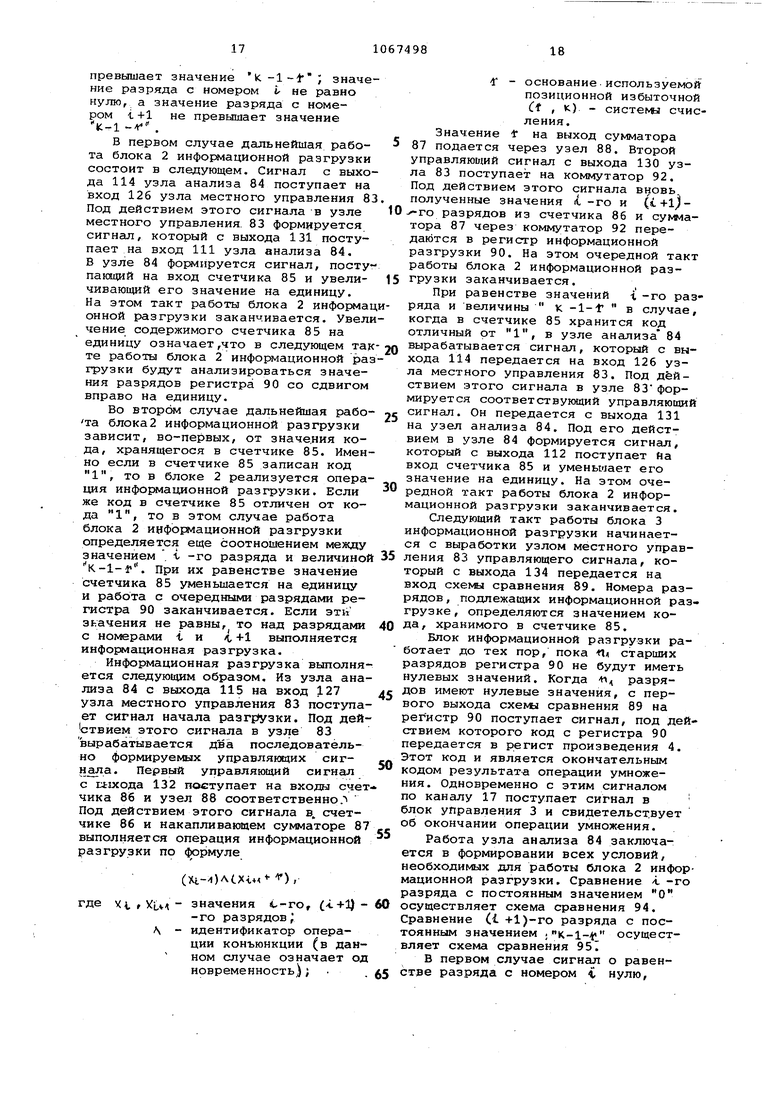

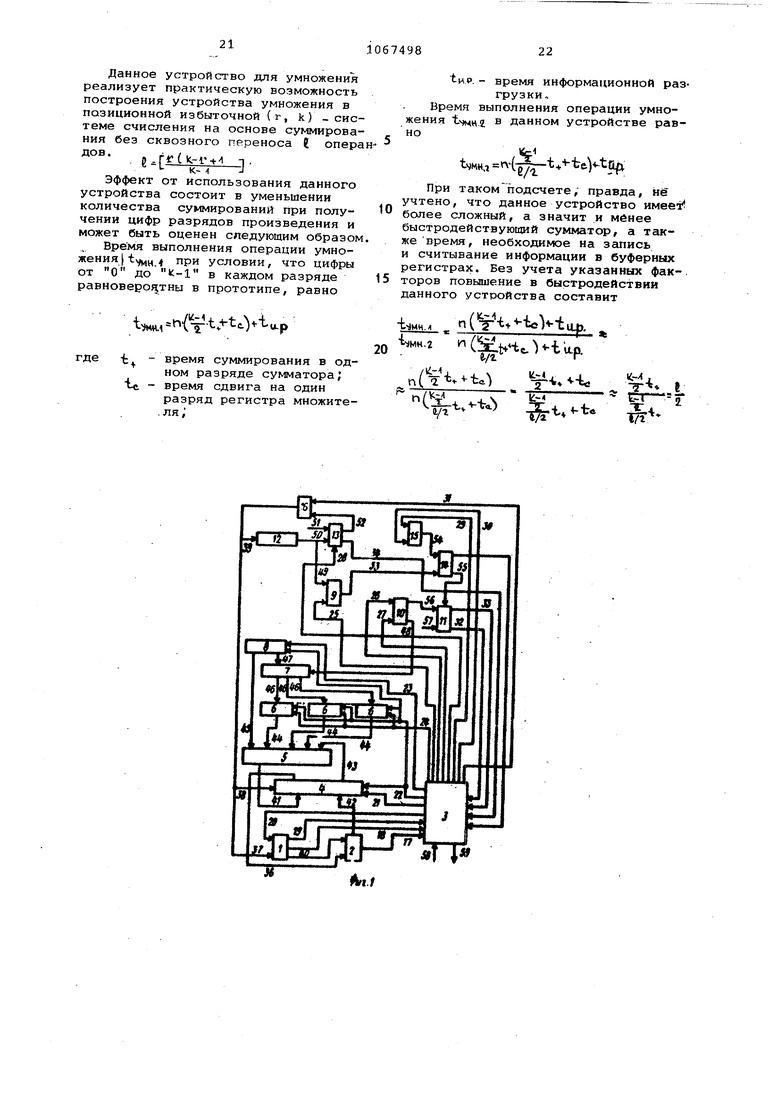

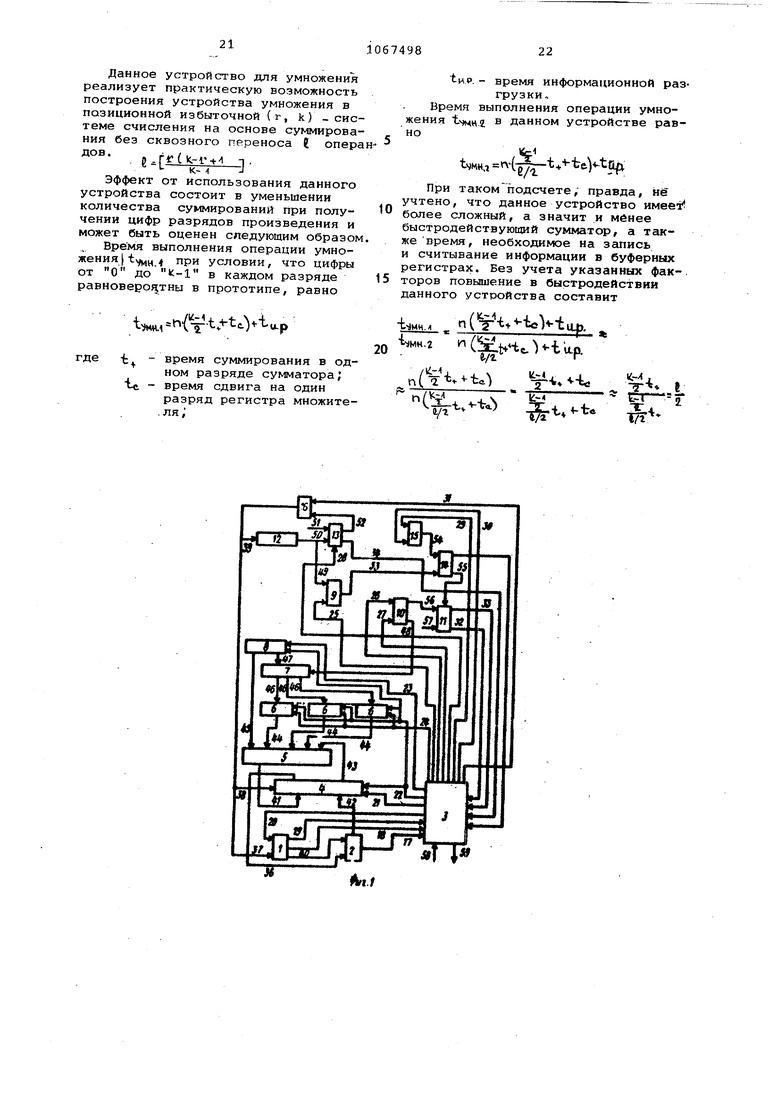

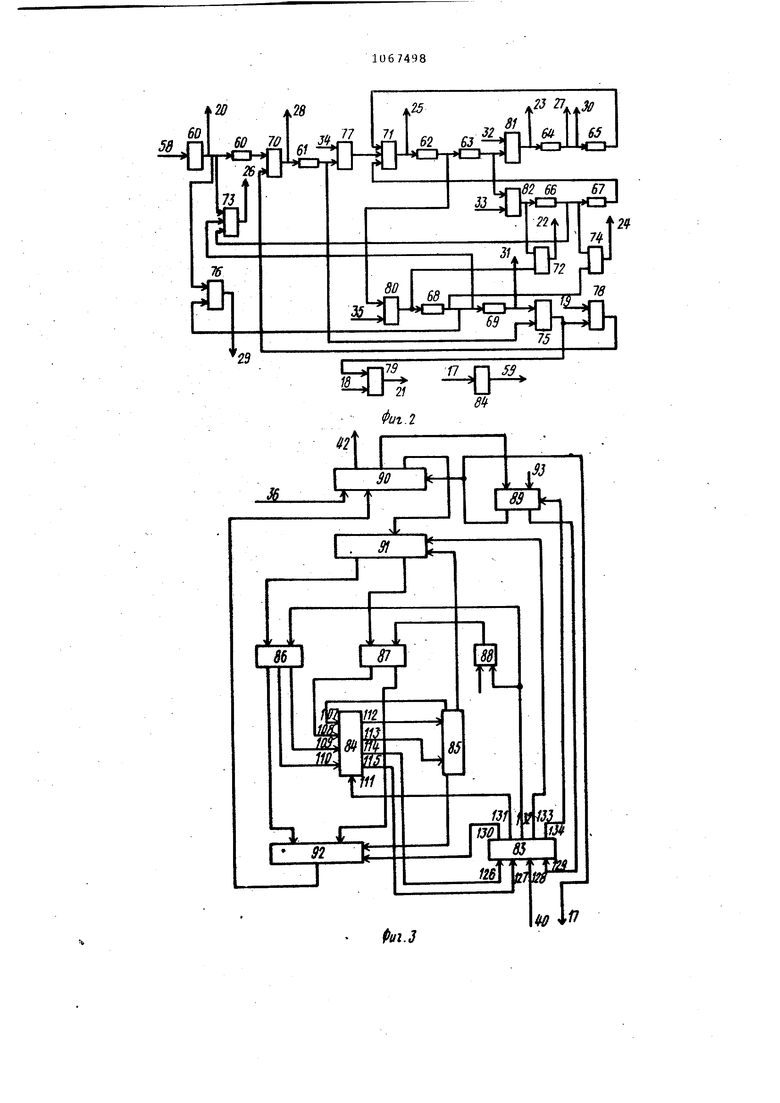

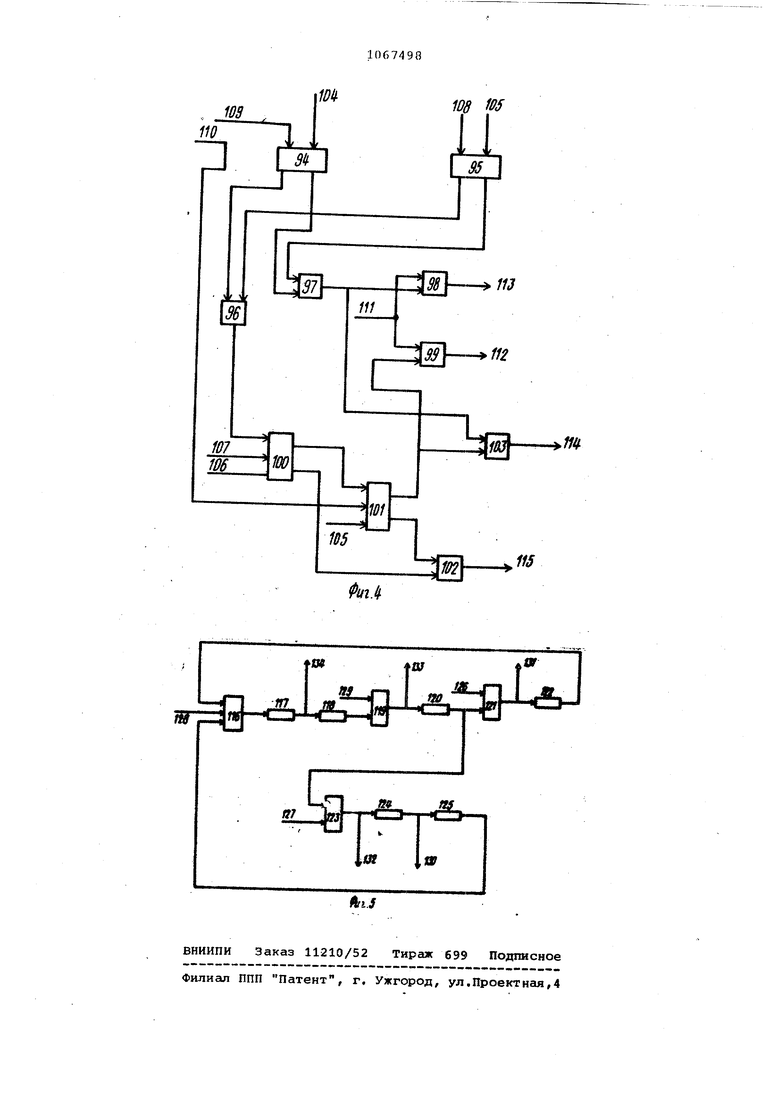

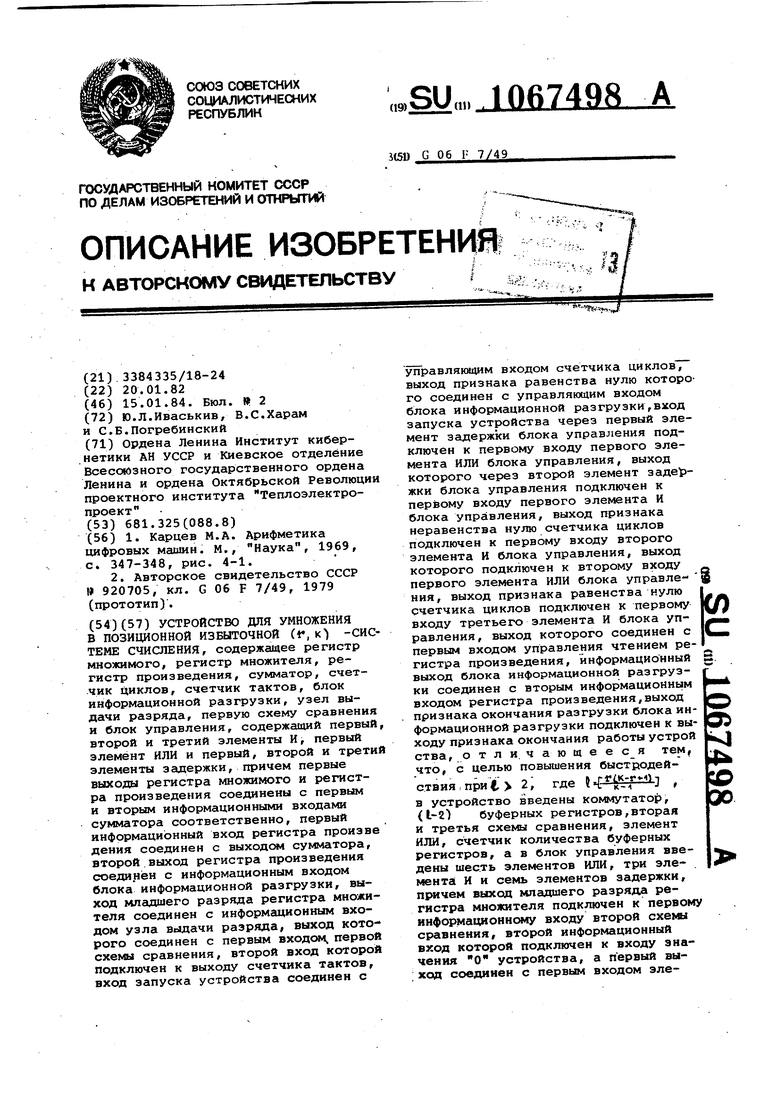

На фиг.1 показана схема устройстза для умножения в позиционной избыточной (г. it) - системе счисления; на фиг.2 - схема блока управления; на фиг.3 - схема блока информационной разгрузки; на фиг.4 - схема узла анализа блока информационной разгрузки/ на фиг.5 - схема узла местного упргшления блока информаци онной разгрузки.

Устройство содержит реверсивный счетчик циклов 1, блок информацион- ной разгрузки 2, блок управления 3, регистр произведения 4,.сумматор 5, Ч1-2 V буферных регистров 3 ко|««утато)р 7, регистр мноч«мого 8, узел 9 выдачи разряда, счетчик 10 количества буферных регистров,схему сравнения 11, регистр множителя 12, схему сравнения 13, схему сравнения 14, счетчик тактов 15, элемент ИЛИ 16, канал 17, соединяющий управляюои1й выход бл;ока информационной разгрузки 2 с первым ВХОДСЯ4 блока управления 3, каналы 18 и 19, соединяющие выходы признаков равенства и неравенства нулю счетчика циклов 1 с вторым и третьим входом блока управления 3, канал 20, соединяющий первый выход блока управления 3 с управляющим ВХОДСХ4 счетчика циклов 1, кангш 21, соединяющий второй выход блока управления 3 с входом управления чтением регистра прсжзведения 4, каналы 22, соединяющие третий выход бло:ка управления 3 с входами управления чтеиием регистра произведения 4, регистра множимого 8 и регистров 6, канал 23, соединяющий четвертый выход блока управления 3 с входом управления чтением регистра множимого 8,каналы 24, соедивяюцие пятый выход блока управления 3 с входами управления записью регистров 6, канал 25, соединяющий шестой выход блока управления 3 с управлякяцим входом узла 9, канал 26, соединяющий седьмой выход блока управления 3 с управляющим входом счетчика 10, канал 27, соединяющий восьмой выход блока управления 3 с информационным входсм счетчика 10, канал 28, соединяющий девятый выход блока управления 3 с управляющим входом схеьсл сравнения 13, каналы 29 и 30, соединяющие соответственно десятый и одиннсщцатый выходы блока управления с управляющими и информационным входами счетчика тактов 15, канал 31, соединяющий двенадцатый, выход блока управления 3 с первым входом элемента ИЛИ 16, каналы 32 и 33, соединякедие выходы схекы сравнения 11 соответственно с четвертым и пятым входами блока управления 3, канал 34, соединяющий выход схемл сравнения 13 с шестым входом блока управления 3, канал 35, соединяющий выход схемы сравнения 14 с седьмы входом блока управления 3, кангш 36, соединяющий первый выход регистра произведения 4 с информационн1 М входом блока информационной разгрузки 2, каналы 37-39, соединяющие выход элемента ИЛИ 16 соответственно с информационным входом счетчика 1, с входом управления сдвигом регистра произведения 4, с входом управления сдвигом регистра множителя 12, канал 40, соединяющий выход приз нака равенства нулю счетчика 1 с управляющим входом блока информационной разгрузки 2, канал 41, сое:диняющий выход сумматора 5 с первым информационным входом регистра произведения 4, канал 42, соединяющий информационный выход блока 2 с вторым информационным входом регистра произведения 4, канал 43, соединяющий выход регистра 4 с информационным входом сумматора 5, каналы 44, соединяющие выходы (I -2) регистров 6 с информационными входами сумматора 5, канал 45, соединяющий выход регистра MHOiiotMoro 8 с информационным входом сумматора 5, каналы 46, соединяющие выходы коммутатора 7 с информационными входами регистров 6, канал 47, .соединяющий выход регистра 8 с информгщионным входом коммутатора 7, Iканал 48, соединяющий выход счетчика 10 с управляющим входом кся мута- тора 7, каналы 49 и 50, соединяющие вь1ход последнего разряда регистра множителя 12 соответственно с информационным входом узла 9 и первым информационным входом схемы сравнения 13, канал 51, соединяющий второй вход схемы сравнения 13 с входом зна чиИИя О, канал 52, соединяющий вы ход cxeMw сравнения 13 с вторым вхо дом элемента ИЛИ 16, канал 53, соединяющий выход узла 9 с первым входом схемы сравнения 14, канал 54, соединяющий выход счетчика тактов 1 с вторым входом схемы сравнения 14, канал 55, соединяющий выход схемы сравнения 14 с управляющим входом схемы сравнения 11, канал 56, соеди няющий выход счетчика 10 с первым информационным входом схемы сравнения 11, канал 57, соединяющий второ информационный вход схемы сравнения 11 с входом значения -1, вход 58 запуска устройства, 59 устройства . признака окончания работы. Регистры б, регистр множимого 8, регистр множителя 12, а также сумма тор 5 имеют по и, k-ичны-х разрядов, регистр произведения 4-2и k-ичных разрядов. Счетчик 15 содержит L двоичных разрядов, счетчик 1 JQctjjCe-Ot- двоичных разрядов, счетчик 1 ) двоичных разрядов. Блок управления 3 (фиг.2) содержит элементы задержки 60-69, элемен ты ИЛИ 70-76, элементы И 77-82. Блок информационной разгрузки 2 (фиг.З) содержит узел 83 местного управления, узел анализа. 84, счетчи 85 номера разряда информационной разгрузки, счетчик 86, накапливающи одноразрядный сумматор 87 по модулю К, узел 88 выдачи, схему сравнения 89, регистр 90 информационной разгрузки, коммутатора 91, 92, щину 93 значения Узел анализа 84 блока 2 (фиг.4) содержит схему сравнения 94, схему сравнения 95, элементы И 96, ИЛИ 97 И 98, И 99, схему сравнения 100, 101, элементы ИЛИ 102, 103, шину 104 значения О, ишну 105 значения К - 1 - г, шину 106 значения 1, входы 107-111, выходы 112-115. Узел 83 местного управления блока 2 (фиг.5) содержит элементы ИЛИ 116 задержки 117, 118, И 119, Задержки 120, И 121, задержки 122, И 123, задержки 124, 125, входы 126-129, выходы i30-134. Устройство работает следующим образом. В исходном состоянии в регистре множителя 12 находится k-ичный код множителя, в регистре 8 - k-ичньгй код множимого. Регистр 4, регистры 6 находятся в нулевом состоянии .гСчет чик тактов 15 и счетчик 10 установлены в состоянии 1 сигналами, поступающими с блока управления 3 по ка налам 29 и 26 соответственно. Под действием управляющего сигнала, поступающего с блока управления 3 по каналу 20, в реверсивный счетчик циклов 1 записывается, число Работа устройства начинается с момента поступления управляющего сигнала по входу 58 устройства. Процесс умножения двух п -разрядных чисел, представленных k-ичными кодами в избыточной (г, k) - системе счисления, в общем случае состоит из собственно операции умножения этих чисел и коррекции результата, связанной с выполнением операции информационной разгрузки. Собственно операций умножения выполняется из п циклов. В каждом очередном цикле множимое умножается на соответствующий i-й (1 ,, tT) разряд множителя. Цикл с номером 1 начинается с, момента поступления управляющего сигнала по каналу 28 с блока управления 3 на схему сравнения 13, По этому импульсу происходит сравнение последнего разряда регистра множителя 12 со значением О. Значение О поступает на схему сравнения 13 по каналу 51, а последний разряд регистра множителя поступает на схему сравнения 13 по каналу 50. Если значение последнего разряда регистра множителя в данном -ом цикле равно нулю, то сигнал с выхода схемы сравнения 13по каналу 52 поступает на элемент ИЛИ 16, с выхода которого сигнал поступает на вхрды управления сдвигом регистра множителя 12 и регистра произведения 4, а также на информационный вход реверсивного счетчика циклов 1. Под действием этого сигналу происходит СДВИГ вправо на один к- ичный разряд содержимого регистров 12, 14и уменьшение на единицу содержимого счетчика циклов 1, Выполнение i-ro цикла собственно операция умиожения в этом случае заканчивается. При выполнении циклов с номерами с первого по (n-) -и значение счетчика 1 не становится равным НУ.ЛЮ после их окончания. В этом случае со счетчика 1 по каналу 19 в блок управления 3 поступает сигнал, под действием которого выполняется следующий цикл собственно операции умножения. Если значение последнего разряда регистра множителя 12 ие равно нулю, то сигнал об этом по каналу 34 поступает на вход блока управления 3, с шестого выхода которого по каналу 25 поступает сигнал на управляющий вход узла выдачи разряда 9. Происходит сравнение последнего разряда регистра множителя с текущим значением счетчика тактов 15. Последний разряд регистра множителя 12 поступает через узел 9 на схему сравнения 14 по каналу 53, а значение счетчика 15 поступает на схему сравнения 14 по каналу 54. При неравенстве кодов, поступающих на входы схемы сравнения 14, сигнал по каналу 55 поступает с выхода схемы сравнения 14 на управляющий вход схемы сравнения 11 и происходит сравнение текущего значения счетчика 10 с постоянным значением t-1. Значение счетчика 10 и постоянное значение J-1 поступают |На входы схемы сравнения 11 соответственно по каналам 56 и 27. При неравенстве этих значений, .сигнал с выхода схемы сравнения 11 по каналу 32 поступает на четвертый вход блока управления 3. С четверто го выхода блока 3 поступает управляющий сигнал по каналу 23, под действием которого осуществляется через коммутатор 7 перепись содержимого регистра 8 в свободный регистр 6, номер которого находится в счетчике 10. Выход счетчика 10 по каналу 48 .поступает на управляющий вход коммутатора 7. Значение регистра множимог 8 по каналу 47 поступает на коммутатор 7 и по одному из каналов 46 - в свободный регистр 6. После окончания формирования кода в свободном регист ре 6 блок управления 3 выдает управляющие сигналы, поступаняцие по каналам 27 и 30 соответственно на входы счетчика 1.0 и счетчика 15 .Происходит увеличение на единицу содержимого этух счетчиков и заканчивается очередной такт выполнения собственно операции умножения. Следующий хакт начинается под действием управляквде го импульса, поступающего по каналу 25 на управляющий вход узла выдачи разряда 9. Если текущее значение счетчика 10 pciBHo , то с выхода схемы сравнения 11 по каналу 33 сигнал поступает на пятый вход блока управления 3. С третьего выхода блока 3 поступа ет управляющий сигнал по кангшу 22 на управляющие входы регистра множимого 8, регистров 6, регистра произведения 4. Под действием этого сигнала осуществляется суммирование кодов указанных регистров в сумматоре 5. Результат суммирования по каналу 41 переписывается в регистр произведения 4. После формирования кода в регистре произведения 4 под действием управляющего сигнала, поступающего сблока управления по каналу 26 происходит установка в 1, счетчика 101, а под действием управляющего сиг нала, поступающего по каналу 24, про исходит установка в нулевое состояни регистров 6. В случае равенства значения счетчика 10 со значением й-1 увеличения значения на единицу содер жимого счетчика тактов 15 не происходит и продолжается выполнение такта. В данном случае продолжение выподнеНия такта npoitcxtijuiT т-лк же, как и начало нового такта при поступлении управляющего сигнала по каналу 25 на узел выдачи разряда 9. Если в процессе выполнения очередного такта i-го цикла работы устройства происходит равенство значения последнего разряда регистра множителя 12 со значением счетчика тактов 15, то происходит окончание выполнения данного t -to цикла собственно операции умножения. При этом с выхода cxeNtJ сравнения 14 по каналу 35 в блок управления 3 поступает сигнал. С третьего выхода блока 3 поступает сигнал по каналу 22, под действием которого осуществляется суммирование кодов регистра множимого 8, регистров 6, регистра произведения 4 в сумматоре 5. Результат суммирования то каналу 41 переписывается в регистр 4. Далее под действием управляющих сигналов, поступающих с блока управления 3 по каналам 26 и 29, происходит установка в единичное состо яние счетчика 10 и счетчика тактов 15, а под действием управл-ппщего сигнала, поступающего по каналу 24, осуществляется установка в нулевое состояние регистров 6. После окончания формирования кодов исходных состояний в счетчиках 10 и 15, а также в регистрах 6, управляющий сиг нал с двенадцатого выхода блока управления 3 поступает по каналу 31 на вход элемента ИЛИ 16. Сигнал с выхода элемента ИЛИ 16, как указано, вызывает переход к следующему (i 41)му циклу выполнения собственно операции умножения. После окончания последнего АЛ-го цикла собственно операции умножения значение счетчика циклов 1 становится равным нулю. В этом случае выхода счетчика 1 по каналу 18 в блок управ ления 3 поступает сигнал, в ответ на который блок управления 3 выдает управляющий сигнал по каналу 21. Под действием этого сигнала код регистра произведения 4, где находится результат собственно умножения, по каналу 36 передается в блок информационной разгрузки 2. Одновременно с передачей сигнала по каналу 18 с выхода счетчика циклов 1 по каналу 40 в блок информационной разгрузки 2 поступает сигнал, инициирующий начало коррекции кода собств.енно умножения. В блоке информационной разгрузки 2 код результата собственно умножения анализируется с целью установления соответствия формы представления результата и формы представления чисел с фиксированной запятой в позиционной избыточной (г, к) - системе счисления. Если соотвс тствие устанавливается, операция ИНфОрМ.1 111ОНИОЙ

разгрузки над результатом собственно умножения не выполняется. Сигнал соответствия из блока 2 по каналу 17 поступает в блок 3 и свидетельствует о завершении операции умножения. Результат умножениядвух чисел находится в регистре произведения 4. Если же соответствие не устанавливается, то в блоке информационной разгрузки 2 над результатом собственно умножения осуществляется . операция информационной разгрузки, пока результат не будет соответствовать фор ме представления чисел с фиксированной запятой в позиционнЬй избыточной (г, К-), - системе счисления. Скорректированный результат умножения с блока информационной разгрузки 2 по каналу 42 поступает в регистр произведения 4, Одновременно с блока информационной разгрузки 2 по каналу 17 в блок управления 3 поступает сигнал об окончании операции умножения .

Работа блока управления 3 начинается под действием входного управля ющего сигнала, поступающего по входу 58 устройства. Этот сигйал передается на канал, а также поступает ,на входы элементов ИЛИ 76, 73. С выходов элементов ИЛИ 76, 73 управляющие импульсы передаются соответственно э каналы 29, 26. Через время t, с выхода элемента ИЛИ 70 второй управлякадий импульс поступит в канал 28. Временный интервал t элемента задержки 60 определяется наибольшим из времен формирования кодов начальных условий в счетчиках 1, 10, 15, Под действием управляющего импульса, поступающего в канал 28, происходит сравнение последнего разряда регистра множителя 12 со значением О. Если значение последнего разряда регистра множителя 12 равно нулю, то сигнал с выхода схемы сравнения 13 поступает по каналу 52jHa элемент ИЛИ 16. С выхода элемента ИЛИ 16 сигнал поступает на управляющие входы регистра множителя 12 и регистра произведения 4, а также на информационный вход счетчика циклов 1. Под действием этого сигнала происходит сдвиг вправо на один К-ичн1дй разряд содержимого регистров множителя 12 и ; произведения 4, а также уменьшение на единицу содержимого реверсивного счетчика циклов 1.

В бло.се управления управляющий сигнал проходит через элемент задержки 61 (временной интервал элемента задержки 61 равен времени формирования кода в схеме сравнения 13), через элемент ИЛИ 75 и поступает на входы элементов И 78, 79. Если значение счетчика 1 не равно нулю, то с выхода этого счетчика на элемент

И 78 приходит разрешающий сигнал и управлякадий сигнал с выхода элемента И 78 поступает на элемент ИЛИ 70, вызывая формирование управляющей последовательности сигналов следующего цикла работы устройства умножения.

Если значение последнего разряда регистра множителя 12 не равно нулю, то сигнал с выхода схеквя сравнения 13 по каналу 34 поступает на вход элемента И 77 и управляющий сигнал с выхода элемента задержки 61 проходит через элемент И 77, элемент ИЛИ 71 и поступает в канал 25. Под действием этого сигнала происходит выдача последнего разряда регистра множителя 12 и сравнение данного разряда со значением содержимого счетчика. 15. Временной интервги элемента задержки 62 равен времени формирования кода в схеме сравнения 14, Если значение содержимого счетчика 15 равно последнему разряду регистра множителя 12, то с выхода схеки сравнения 14 по каналу 35 пр(1ходит разрешающий сигнал на вход элемента И 80. Управляющий сигнал с выхода элемента задержки 62 проходит через элемент И 80 и через элемент ИЛИ 72 поступает в канал 22, Под действием этого сигнала осуществляется суммирование кодов регистра множимого 8, регистров 6, регистра произведения 4 в сумматоре 5, В блоке управления управляющий сигнал проходит через элемент задержки 68 {временной интервал элемента задержки 67 равен времени фс мирования кода в сумматоре 5 и поступает на эле.мент ИЛИ 74 и на элемент ИЛИ 76, 73 соответственно, С выходов элементов ИЛИ 74, 76, 73 управлякхцие сигналы поступают в каналы 24, 29, 26, В блоке управления управляющий сигнал проходит через элемент згщержки 69 (временной интервал элемента задержки 69 равен наибольшему из времен формирования кодов начальных условий в регистрах 6, счетчиках 10, 151 и поступает в канал 31. Под действием этого управляквдего сигнала происходит окончание выполнения очередного . -го цикла устройства умножения,

После окончания очередного i-го (, 2, .,,, П-ly цикла работы устройства, содержимое счетчика циклов 1 не равняется нулю, В этом случае разрешающий сигнал по каналу 19 поступает на вход элемента И 78 и управляющий сигнал с выхода элемента И 78 поступает на вход элемента ИЛИ 70, вызывая фоЕШИрование улравлякщек последовательности следующего цикла работы устройства.

После окончания последнего Я -го цикла устройства содержимое счетчика циклов 1 равняется нули. В этом случае разрешающий сигнал поступает по каналу 18 с выхода счетчика 1 на элемент И 79. Управляющий сигнал с выхода элемента И 79 по каналу 21 поступает на управляющий вход регист ра произведения 4. Под действием этого сигнала код регистра 4 передается в блок информационной разгрузки 2. После окончания работы блока 2 по каналу 17 в блок управления 3 поступает сигнал окончания коррекции результата. Этот сигнал поступает на выход 59 устройства. Если значение содержимого счетчика 15 не равно содержимому последнего раэряда регистра множителя 12, то управля ющий сигнал с выхода схемы, сравнения 14 ПС каналу 55 поступает на управлякщий вход схемы сравнения 11 и разрешает сравнение содержи.мого счетчика 10 с постоянным значением t-1. в блоке управления 3 управлякшшй сигнал проходит через элемент задержки 63 (временной интервал элемента задержки 63 равеи времени формирования кода в схеме сравнения 11) и поступает на входы элементов И 81, 82. При неравенстве кодов, посту пгиощих на входы схемы сравнения 11, разрешающий сигнал поступает по каналу 32 на вход элемента И 81 и управляющий сигнгш проходит через элемент И 81, с выхода которого поступа ет в кансШ 23. Через временной интервал элемента задержки 64 (определяется временем переписки кода из регастра 8 в свободный регистр 6) уп равляющий сигнал поступает в кангшы 27 и 30. После поступления управляющего сигнала в каналы 27 и 30 через временной интервал элемента згшержки 65 (временной интервал элемента задержки 65 определяется наибольшим из времен формирования кода в счетчиках 10 и 15) управляющий сигнал поступает на вход элемента ИЛИ 71, вызывая формирование управляющей пос ледовательности сигналов следующего такта выполнения операции умножения П1ри равенстве значения счетчиКеГ 10 «постоянного значения 1-1 раз решсцощий сигнал поступает по каналу 33 на вход элемента И 82. В этом случае управляющий сигнал с выхода элемента задержки 63 поступает на вход элемента И 82 и проходит через него. Далее управляюсдай сигнал поступает на вход элемента ИЛИ 72, а через элемент задержки 66 на входы элементов ИЛИ 73, 74, С выходов эле ментов ИЛИ 72-74 управляющие сигнал поступают соответственно в каналы 22i, 26, 24. Временной интервал элемента задержки 66 равен временному интервалу элемента задержки 68. Управляющий сигнал в блоке управления 3 проходит через элемент задержки 67 (Временной интервал элемента задержки 67 равен временному интервалу элемента задержки 691 и поступает на вход элемента ИЛИ 71, вызывая продолжение выполнения данного такта работы устройства. Блок информационной разгрузки 2 работает следующим образом. В исходном состоянии в регистре 90 находится код результата выполнения собственно операции умножения. Счетчик 86 и накапливающий одноразрядный сумматор 87 по модулю к находятся в нулевом состоянии. В счетчик 85 занесен код 1. По управляющему скгнсшу, поступающему с выхода 134 узла местного управления 83 на схему сравнения 89, происходит сравнение п старших разрядов регистра 90 с кодом нуля, поступающего на схему сравнения 89 по шине 93. Если старших разрядов регистра 90имеют нулевые значения, то с первого выхода схемы сравнения 89 на регистр 90 поступает сигнал, под действием которого код с регистра 90 передается в регистр произведения 4. Этот код и является окончательным . кодом результата выполнения операции умножения. Одновременно с этим сигналсял по каналу 17 поступает сигнал в блок управления 3 и свидетельствует об окончании операции умножения. . Если же n старших разрядов регистра 90 не равны нулю, этом случае с второго выхода схемы сравнения 89 на вход 129 узла 83 поступает сигнал о неравенстве кодов, поступающих на входы схемы сравнения 89. По этому сигналу из узла местного управления 83 с выхода 133 выдается управляющий сигнал, разрешающий передачу i-ro и -го раз {рядов регистра 90 через коммутатор 91в счетчик 86 и накапливающий сумIматор 87. Номер i. -го разряда определяется кодом, хранящимся в счетчике 85. Поскольку информационная разгрузка начинается с первого и второго разрядов, то начальное значение счетчика 85 равно 1. Значение счетчика 85 поступает на коммутатор 91, разряд регистра 90 с номером А. через комвлутатор 91 поступает в счетчик 8$, а разряд с номером t+1 через коммутатор 91 поступает в сумматор 87. Значения разрядов с номерами i, i +1, хранящиеся в счетчике 86 и сукматоре 87 соответственно, анализируются в узлеанализа 84. При этом для работы блока 2 информационной разгрузки существенное значение имеют два таких случая: значение разряда с номером С равно нулю, либо значение разряда с номером +

превышает значение -l-i , значение разряда с номером 1 не равно нулю, а значение разряда с номером i+1 не превышает значение ic-l .

В первом случае дальнейшая работа блока 2 информационной разгрузки состоит в следующем. Сигнал с выхода 114 узла анализа 84 поступает на вход 126 узла местного управления 83 Под действием этого сигнала в узле местного управления. 83 формируется сигнал, который с выхода 131 поступает на вход 111 узла анализа 84. В узле 84 формируется сигнал, поступакадий на вход счетчика 85 и увеличивающий его значение на единицу. На этом такт работы блока 2 информацонной разгрузки заканчивается. Увеличение содержимого счетчика 85 на единицу означает,что в следующем так те работы блока 2 информационной разгрузки будут анализироваться значения разрядов регистра 90 со сдвигом вправо на единицу.

Во втором случае дальнейшая работа блока2 информационной разгрузки зависит, во-первых, от значе.ния кода, хранящегося в счетчике 85. Именно если в счетчике 85 записан код 1, то в блоке 2 реализуется операция информационной разгрузки. Если же код Б счетчике 85 отличен от кода 1, то в этом случае работа блока 2 информационной разгрузки определяется еще соотношением между значением . i -го разряда и величиной к-1-r. При их равенстве значение счетчика 85 уменьшается на единицу и работа с очередными разрядами регистра 90 заканчивается. Если эти зкачения не равны, то над разрядами с номерами i и /i +1 выполняется информационная разгрузка.

Информационная разгрузка выполняется следующим образом. Из узла анализа 84 с выхода 115 на вход 3-27 узла местного управления 83 поступает сигнал начала разгр узки. Под действием этого сигнала в узле 83 вырабатывается два последовательно формируемых управляющих сигнала. Первый управляющий сигнал с кнхода 132 поступает на входы счетчика 86 и узел 8В соответственной Под действием этого сигнала в. счетчике 86 и накапливающем суквиаторе 87 выполняется операция информационной разгрузки по рмуле

()li-l)A(.Xi44 ),

где Xi , VU - значения t-ro, (-c+l) -го разрядов; Л - идентификатор операции конъюнкции (в данном случае означает од новременность);

у - основание используемой позиционной избыточной Ct , 1C) - систеки счисления.

Значение f на выход сумматора 87 подается через узел 88. Второй управляющий сигнал с выхода 130 узла 83 поступает на коммутатор 92. Под действием этого сигнала вновь полученные значения л, -го и (i+lj го разрядов из счетчика 86 и сумматора 87 через коммутатор 92 передаются в регистр информационной разгрузки 90. На этом очередной такт работы блока 2 информационной разгрузки заканчивается.

При равенстве значений -го разряда и величины к -l-f в случае когда в счетчике 85 хранится код отличный от 1, в узле анализа 84 вырабатывается сигнал, который с выхода 114 передается на вход 126 узла местного управления 83. Под действием этого сигнала в узле 83формируется соответствующий управляющий сигнал. Он передается с выхода 131 на узел анализа 84. Под его действием в узле 84 формируется сигнал, который с выхода 112 поступает На вход счетчика 85 и уменьшает его значение на единицу. На этом очередной такт работы блока 2 информационной разгрузки заканчивается.

Следующий такт работы блока 3 информационной разгрузки начинается с выработки узлом местного управления 83 управляющего сигнала, который с выхода 134 передается на вход схеки сравнения 89. Номера разрядов , подлежащих информационной разгрузке, определяются значением кода, хранимого в счетчике 85.

Блок информационной разгрузки работает до тех пор, пока Пд старших разрядов регистра 90 не будут иметь нулевых значений. Когда -н разрядов имеют нулевые значения, с первого выхода схемы сравнения 89 на регистр 90 поступает сигнал, под действием которого код с регистра 90 передается в регист произведения 4. Этот код и является окончательным кодом результата операции умножения. Одновременно с этим сигналом по каналу 17 поступает сигнал в блок управления 3 и свидетельствует об окончании операции умножения.

Работа узла анализа 84 заключается в формировании всех условий, необходимых для работы блока 2 информационной разгрузки. Сравнение -1 -го разряда с постоянным значением О осуществляет схема сравнения 94. Сравнение (t +1)-го разряда с постоянным значением .n-l-i осуществляет схема сравнения 957

В первом случае сигнал о равенстве разряда с номером i нулю. либо сигнал о том, что значение разряда с номером -t+l превышает значение к -1-г , поступают на вы ходы элемента ИЛИ 97. Сигнал с выхо да элемента ИЛИ 97 поступает на вход элемента И 98 и через элемент ИЛИ 103 этот сигнал поступает на выход 114 узла 84. Управляющий сигнал поступает с выхода 131 узла местного управления 83 на входы элементов И 98, 99. Так как на другом входе элемента И 98 разрешающий сигнал, то управляюишй сигнал проходит через элемент И 98 на выход 113узла 84. Во втором случае сигнал о нераве стве -t -го разряда нулю, а также сигнал о том, что значение - +1)-г разряда не превышает значение t-l-f , поступают на входы элемента И 96. На выходе элемента И 96 формулируется сигнал второго случая работы блока 2 информационной разгрузки. Этот сигнал поступает на вход схемы сравнения 100 и разрешает сравнение значения счетчика 85 и постоянного значения 1. Значени счетчика 85 поступает на вход 107 узла 84, а значение 1 поступает на вход схемы 100.по шине 106. Если значение счетчика 85 равно едини це , то сигнал с второго выхода схе мы сравнения 100 поступает на вход элемента ИЛИ 102 и на выход 115 узл 84. В блоке информационной разгрузки 2 выполняется операция информационной разгрузки как указано. Если код в счетчике 85 отличен от кода 1, то сигнал с первого выхода схе мы сравнения 100 поступает на вход схемы сравнения 101 и разрешает сравнение i -го разряда С.постоянным значением |с.-1-Г . Если значение г -го разряда равно величине t-1-4 , то сигнал с первого выхо да схемы сравнения 101 поступает элемента ИЛИ 102 и на вход элемента И 99. С выхода элемента ИЛИ 103 сигнал поступает на выход 114узла 84. Управляю11а1й сигнал пос тупает с выхода 131 узла 83 на входы элементов И 98, 99. Так как в этом случае на другом входе элемента И 99 разрешающий сигнал, то управляющий сигнал проходит через эле мент И 99 на выход 112 узла 84. Есл значение - -го разряда не равно величине fc-1-f , то сигнгш с второго выхода схемы сравнения 101 ;ПОступает на вход элемента ИЛИ 102. С выхода элемента ИЛИ 102 сигнал по тупает на выход 115 узла 84. Работа узла 83 местного управления заключается в выработке управлякяаей последовательности сигналов, необходимых для работы блока 2 информационной разгрузки. После окончания операции собственно умножения сигнал с выхода счетчика циклов 1 поступает по каналу 40 на вход элемента ИЛИ 116 и начинает формировать управляющую последовательность сигналов. Первый управляющий сигнал поступает в блок информационной разгрузки с выхода 134 через время X после прихода сигнала по каналу 40. Время Cv определяется приемом кода из регистра произведения 4 в регистр информационной разгрузки 90 и формируется элементом задержки 117. Если на вход 129 приходит сигнал, то через время ti с выхода элемента И 119 формируется второй управляющий сигнал. Время ti определяется формированием сигнала на выходе схемы сравнения 89. Временной интервгш & формирует элемент задержки 118 Второй управляющий сигнал поступает на выход 133, проходит через элемент задержки 120 с временем задержки tn, . Это время определяется появлением сигналов узла анализа 84. Если с выхода 114 узла анализа 84 поступает сигнал на вход 126, то на выходе элемента И 121 формируется третий управляющий сигнал, поступающий на выход 131. Этот же . сигкал, пройдя через элемент задержки 122, поступает на вход элемента ИЛИ 116 и вызывает формирование последовательности сигналов следующего такта работы блока информационной разгрузки. Временной интервал И, элемента задержки 122 определяется установлением кода в счетчике 85. Если с выхода 115 узла анализа 84 поступает сигнал на вход 127, то с выхода элемента И 123 на выход 132 поступает четвертый управляющий сигнгш. Через временной интервал t после формирования четвертого управ ляющего сигнала на выход 130 поступает пятый управляпкпй сигнал. Временной интервал 5 определяется временем выполнения операции информационной разгрузки и формируется элементом зещержки 124. Пятый управляющий сигнал, пройдя через элемент задержки 125 с временем задержки t, поступает на вход элемента ИЛИ 116 и вызывает формирование управляющей последовательности следующего такта работы блока информационной азгрузки 2. Временной интервгш t« определяется временем приема кода вновь образованных разрядов с номерами i и /+1 в регистр информационной разгрузки 90. Узел местного управления 83 прекращает свою работу в том случае, если отсутствует сигнал на входе 129. В этом случае блок информационной разхтУзки 2 формирует сигнал, поступаюиий по каналу 17 в блок 3 и определяичий оконче-ние работы блока 2. Данное устройство для умножения реализует практическую возможность построения устройства умножения в позиционной избыточной (г, k) - сис теме счисления на основе суммирования без сквозного переноса опера °° . p-f«uLfeii±i i. I- к- J Эффект от использования данного устройства состоит в уменьшении количества суммирований при получении цифр разрядов произведения и может быть оценен следующим образом Время выполнения операции умножения(1чуцц4 при условии, что цифры от О до с-1 в каждом разряде равноверО5|тны в прототипе, равно W,{T-t. где (; - время суммирования в одном разряде сумматора; ini - время сдвига на один разряд регистра множите. ля, tnp. - время информационной разгрузки. Время выполнения операции умножения 1(чн.г в данном устройстве равноtvMHa )4-tQ При таком подсчете, правда, не учтено, что данное устройство имее-х более сложный, а значит и менее быстродействующий сумматор, а также время, необходимое на запись и считывание информации в буферных регистрах. Без учета указанных факторов повышение в быстродействии данного устройства составит .. , nC.ieVtu. .)-tap. t/г г„(.t. , ir-, r Ч.... Mt..b Фиг.г

1Ю

Риг.З Р

Wtt109 .

жГд

ТП D

I

108 105

ш

т

./У«

U

105

f//

ам-

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Верхний многокамерный кессонный шлюз | 1919 |

|

SU347A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1979 |

|

SU920705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-15—Публикация

1982-01-20—Подача