(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в позиционной избыточной ( @ , @ )-системе счисления | 1982 |

|

SU1067498A1 |

| Устройство для деления | 1980 |

|

SU928344A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Преобразователь кода одной позиционной системы счисления в другую | 1980 |

|

SU960793A1 |

| Устройство для приема информации | 1979 |

|

SU796893A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

I

Изобретение относится к вычисли тельной технике и может быть использовано при построении арифметических устройств ЦВМ.

Известны устройства для умножения чисел с фиксированной запятой в позиционной системе счисления. Такие устройства содержат регистр множимого, регистр множителя, сумматор l н 2.

Наиболее близким к предлагаемому является устройство для умножения чисел с фиксированной запятой в позиционной системе с шсления содержащее регистры множимого и множителя, регистр произведения, сумматор, блок управления, причем выходы регистров множимого и произведения соединены со входами сумматора, выход которого соединен со входом регистра произведенияШ.

Однако оно не позволяет выполнять операцию умножения чисел с фиксированной запятой в позиционных избыточных (г, k) - системах счисления, использование которых позволяет повышать быстродействие операционных устройств за счет исключения переноса через несколько разрядов при суммировании. Известное устройство для умножения не может быть использовано для умножения чисел с фиксированной запятой в позиционных избыточных (г, k) системах /счисления потому, что его структура и принцип действия не учитывают специфики представления в таких системах счисления чисел с фиксированной запятой. Эта специфика состоит в том, что между перпой значащей цифрой числа и запятой записывается п нулей, причем

k-1

т 1 К- I г

31од г ,

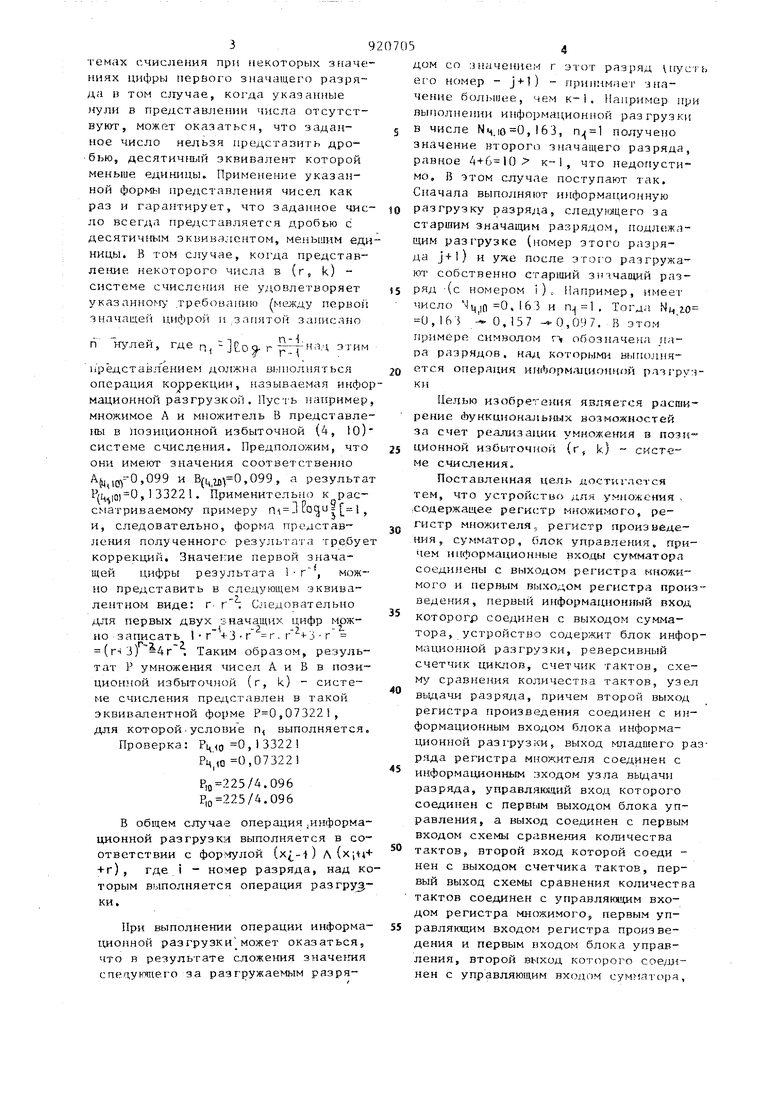

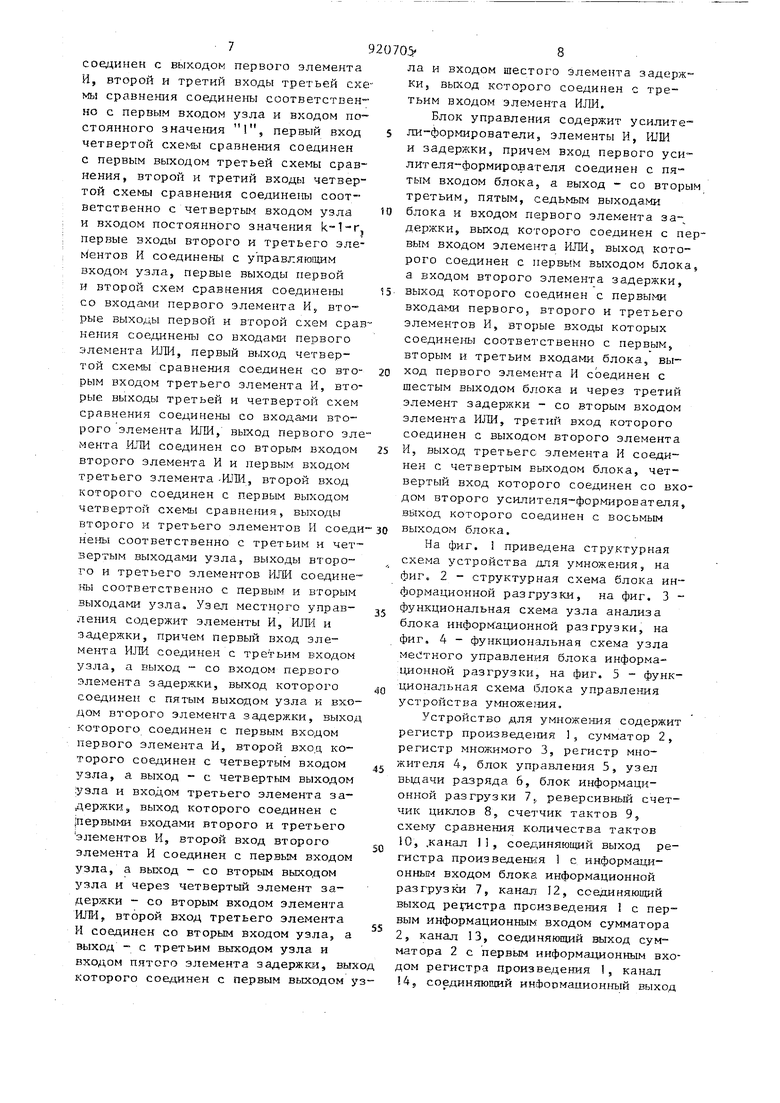

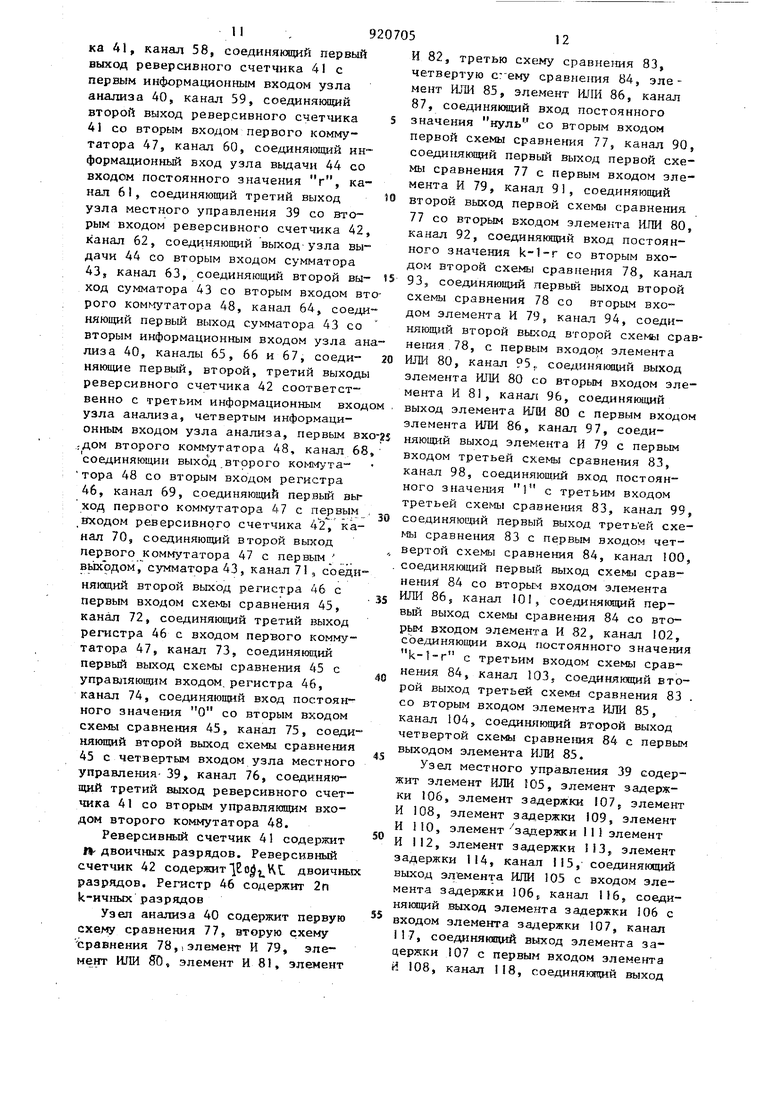

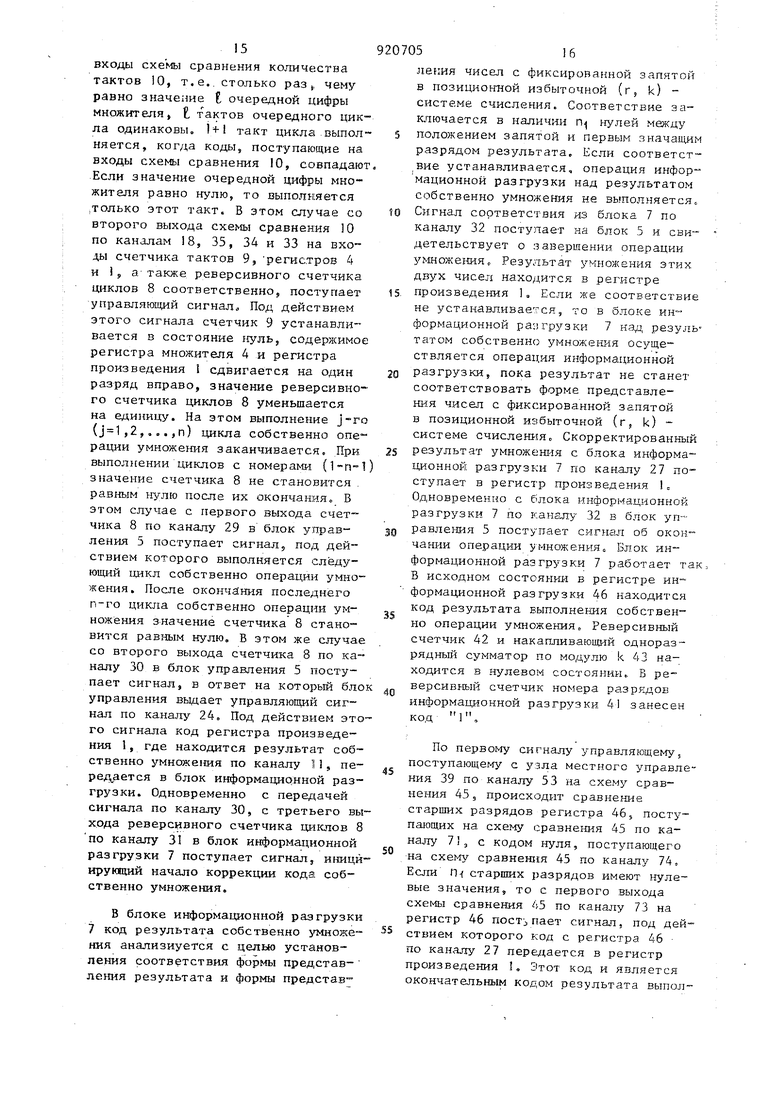

где 1tt - идентификатор округления t до ближайшего целого значения. В избыточных позищтонных (г, k) - сие39темах счисления при некоторых значениях цифры первого значащего разряда в том случае, когда указанные нули в представлении числа отсутствуют, может оказаться, что заданное число нельзя представить дробью, десятичный эквивалент которой меньше единицы. Применение указанной формы представления чисел как раз и гарантирует, что заданное число всег/,а пре;1,ставляется дробью с десятич1 ым эквивалентом, меньшим еди ницы. В том случае, когда представле ше- некоторого числа в (г, k) системе счисления не удовлетворяет yкaзaннo ry тpeбoвaн iю между первой значащей цифрой и .запятой записано , где р, на,, Эгим нрёдставлением должна выполняться операция коррекции, называемая инфор мационной разгрузкой . Пус1Ь например множимое А и множитель В нредставле Ы в Позиционной избыточной (4, 10) системе счисления. Предположим, что они имеют значения соответственно Af ,099 и В(ц гвГО099, а результат Р/ц 1(1)0,1 3322 . Применительн(з к рассматриваемому примеру П- J l-QJul 1 и, следовательно, форма представпения полученного результата требуе коррекций, Значегше первой значащей цифры результата 1г, можно представить в следующем эквивалентном виде: г. г . Следовательно для первых двух значащих цифр мож но записать г.г -i-j-r (r-i З) -Ar . Таким образом, результат Р умножения чисел А и В в позиционной избыточной (г, k) - системе счисления представлен в такой эквивалентной форме ,073221, для которой.условие п выполняется. Проверка: 0,13322 Рц,а 0,07322 i P,(j 225/4.096 Pio 225/4.096 В общем случае операция .информационной разгрузки выполняется в соответствии с фop:Nfyлoй () Л {х|-ц+ +г), где i - номер разряда, над к торым выполняется операция pa3rpyj. ки. При выполнении операции информа ьщонной разгрузкиможет оказаться, что в результате сложения значергня спеауютего за разгружаемым разрядом со значением г этот разряд игусть его номер - ) - принимает значение , чем к-1. 1апримар при выгюлнеиии информационной разгрузки в числе N.,163, п 1 получено значение второго значащего разряда, ранное к-1, что недопустимо, В этом случае поступают так. Сначала выполняют информационную разгрузку разряда, сле/дугацего за старшим значащим разрядом, подле.жащим разгрузке (номер этого разряда ) и уле после этохо разгружают собственно старншй злччаошй разряд -(с номером 1)„ 1апример, имеет число Nijid 0.163 и . Тогда ц го 0,163 ,157 -. 0,09 7. В этом примере символом ni обозначена пара разрядов, Haj.i, которыми вьпюлняется операция ииЛормлционнпй разгрузкиЦелью изобретения является расширение йункциональнмх возможностей за счет реализации умножения в пози ционной избыточной (г, k.) - системе счисления. Поставленная цель х остнглстся тем, что устройство для умножения , 1содержа дее регистр множимого, регистр мм.ожителя, регистр произведения, сумматор, блок управления, причем информационные входы сумматора соединены с выходом регистра множимого и первым вь ходом регистра произведения, первый информационный вход которогр соединен с выходом сумматора, устройство содержит блок информационной разгрузки, реверсивный счетчик циклов, счетчик тактов, схему сравнения количества тактов, узел выдачи разряда, причем второй регистра произведения соединен с информационным входом блока информационной разгрузки, выход младшего разряда регистра множителя соединен с информационным зходом узла вьщачи разряда, управляющий вход которого соединен с первым выходом блока управления, а выход соединен с первым входом схемы сравнения количества тактов, второй вход которой соеди нен с выходом счетчика тактов, первый выход схемы сравнения количества тактов соединен с управляющим входом регистра множимого, первым управляющим входом регистра произведения и первым входом блока управления, второй выход которого coe/inнен с управляющим входом сум:матс.1ра, второй и третий управляющие входы регистра произведения соединены соответственно с третьим и четвертым выходами блока управления, второй выход схемы сравнения количества та тов соединен с управляющим входом регистра множителя, четвертым управ ляющим входом регистра произведения и первым входом счетчика тактов, второй и третий входы-которого соединены соответственно с пятым и шес тым выходами блока управления, седь мой выход которого соединен с первым входом реверсивного счетчика ци ЛОВ, второй вход которого соединен со вторым выходом схемы сравнения количества тактов, первый, второй и третий выходы реверсивного счетчика циклов соединены соответственно со вторым и третьим входами блока управления и управляющим входом блока информационной разгрузки, информационный и управлякяций выходы которого сое хинены соответственно со вторым информационным входом регистра произ ведения и четвертым входом блока управления, пятыйвход которого соединен с управлякицим входом устройства выход индикации которого соединен с восьмым выходом блока управления. Блок информационной разгрузки содержит узел местного управления, узе анализа, реверсивный счетчик номера разрядов информационной разгрузки, реверсивный счетчик, накапливающий одноразрядный сумматор по модулю k, узел выдачи, схему сравнения, регист информационной разгрузки, первый и второй коммутаторы, причем первый ин формационный вход регистра информаци онной разгрузки соединен с информационным входом блока, первьй, второй и третий выходы регистра информационной разгрузки соединены соответственно с информационным выходом бло ка, первым информационным входом схе мы сравнения и информационным входом первого коммутатора, первый и второй выходы которого соединены с первыми входами соответственно реверсивного счетчика и накапливающего одноразрядного сумматора по модулю k, первый, второй, третий, четвертый и пятьш выходы узла местного управления соединены соответственно с первым управляющим входом второго коммутатора, управляющим входом узла анализа, вторым входом ревер сивного счетчика, первым управля(о056ним входом nepBOio ком.-гутатора и управляющим входом сксмы сравнения, первый и второй выходы узла анализа соединены соответствен}1о с первым и вторым входами узла местного управления, третий и четвертый выходы узла анализа соединены соответственно с первым и вторым входами реверсивного счетчика номера разрядов информационной разгрузки, первый, второй и третий выходы которого соединены соответственно с первым информационным входом узла анализа, вторым управляющим входом первого коммутатора и вторым управляющим входом второго комментатора, первый выход накапливающего одноразрядноIO сумматора по модулю k соединен со вторым информационным входом узла анализа, п&рвый, второй и третий выходы реверсивного счетчика соединены соответственно с третьим и четвертым информационными входами узла анализа и первым информационным входом второго коммутатора, второй инфopмaциoн a ш вход которого соединен со вторым выходом накапливающего одноразрядного сумматора по модулю k, второй вход которого соединен с выходом узла выдачи, управлякщий вход блока соединен с третьим входом узла местного управления, первый выход схегФ. сравнения соединен с управляющим входом регистра информационной разгрузки и управляюи(им выходом блока, второй выход схемы сравнения соединен с четвертым входом узла местного управления, выход второго коммутатора соединен со информационным входом регистра информационной разгрузки, информационный вход узла, выдачи соединен со входом вход узла выдачи соединен с третьим выходом узла местного управления, второй информационный вход схемы сравнения соединен со входом постоянного значения О. Узел анализа содержит четыре схемы равнения, три элемента И, три элеента ШШ, причем первый и второй ходы первой схемы сравнения соеинены соответственно с третьим вхоом узла и входом постоянного значеия О, первый и второй входы втоой схемы сравнения соединены соотетственно со вторым входом узла и ходом постоянного значения k-1-r, epBbM вход третьей схемы сравнения соеддинен с выходом первого элемента И, второй и третий входы третьей схе f-ibi сравнения соединены соответственно с первым входом узла и входом постоянного значения 1, первый вход четвертой схемы сравнения соединен с первым выходом третьей схемы сравнения, второй и третий входы четвертой схемы сравнения соединены соответственно с четвертым входом узла и входом постоянного значения k-1-r, первые входы второго и третьего элементов И соединены с управляюпшм входом узла, первые выходы первой и второй схем сравнения соединены со входами первого элемента И, вторые выходы первой и второй схем срав нения соединены со входами первого элемента ШЖ, первый выход четвертой схемы сравнения соединен со вторым входом третьего элемента И, вторые выходы третьей и четвертой схем сравнения соединены со входами второго элемента ИЛИ, выход первого эл мента ИЛИ соединен со вторым входом второго элемента И и первым входом третьего элемента -ШШ, второй вход которого соединен с первььм выходом четвертой схемы сравнения, выходы второго и третьего элементов И соед нены соответственно с третьим и чет вертым выходами узла, выходы второго и третьего элементов ИЛИ соедине пЫ соответственно с первым и вторым выходами узла. Узел местного управления содержит элементы И, ИЛИ и задержки, причем первый вход элемента ШЖ соединен с третьим входом узла, а выход - со входом первого элемента задержки, выход которого соединен с пятым выходом узла и вхо дом второго элемента задержки, выхо которого соединен с первым входом первого элемента И, второй вход которого сое-динен с четвертым входом узла, а выход - с четвертым выходом узла и входом третьего элемента задержки, выход которого соединен с ,первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с первьЕм входом узла, а выход - со вторым выходом узла и через четвертый элемент задержки - со вторым входом элемента 1-ШИ, второй вход третьего элемента И соединен со вторым входом узла, а выход - с третьим выходом узла и входом пятого элемента задержки, вы которого соединен с первым выходом ла и входом шестого элемента задержки, которого соединен с третьим входом элемента ИЛИ, Блок управления содержит усилители-формирователи, элементы И, ШШ и задержки, причем вход первого усилителя-формирователя соединен с пятым входом блока, а выход - со вторым третьим, пятым, седьмым выходами блока и входом первого элемента задержки, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с первым выходом блока, а входом второго элемент а задержки, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим входами блока, выход первого элемента И соединен с шестым выходом блока и через третий элемент задержки - со вторым входом элемента ИЛИ, третий вход которого соединен с выходом второго элемента И, выход третьего элемента И соединен с четвертым вькодом блока, четвертый вход которого соединен со входом второго усилителя-формирователя, выход которого соединен с восьмым выходом блока. На фиг, 1 приведена структурная схема устройства для умноже шя, на фиг. 2 - структурная схема блока информационной разгрузки, на фиг. 3 функциональная схема узла анализа блока информационной разгрузки, на фиг, 4 - функциональная схема узла местного управления блока информационной разгрузки, на фиг, 5 - функциональная схема блока управления устройства умножег-шя. Устройство для умножения содержит регистр произведения 1, сумматор 2, регистр множимого 3, регистр множителя 4, блок управления 5, узел выдачи разряда 6, блок информационной разгрузки 7f реверсивный счетчик циклов 8, счетчик тактов 9, cxBNry сравнения количества тактов 10, .канал 11, соединяющий выход регистра произведения с информационньи входом блока информационной разгрузки 7, канах( 12, соединяющий выход реестра произведения 1 с первым информационным входом сумматора 2, канал 13, соединяющий выход сумматора 2 с первым информационным входом регистра произведения I, канал 14, соединяющий информацион11ый выход регистра множимого 3 со вторым информационным входом сумматора 2, канал 15, соединяюищн первый выход сх мы сравнения количества тактов 10 с управляющим входом регистра множимого 3, канал 16, соединяющий выход узла выдачи разряда 6 с первым входо схемы сравнения количества тактов 10 канал 17, соединяющий выход счетчика тактов 9 со вторым входом схемы срав иения количества тактов 10, канал 18 соединяющий второй выход схемы сравнения количества тактов 10 с первым входом счетчика тактов 9, канал 19, соединяющий первый выход схемы оравнения количества тактов 0 с первым управляющим входом регистра произведения 1, канал 20, соединяющий первый выход схемы сравнения количества тактов 10 с первым входом блока у равления 5, канал 21, соединяющий первьш выход блока управления 5 с управляющим входом узла выдачи разря да 6, канал 22, соединяющий второй выход блока управления 5 с управляю щим входом сумматора 2, канал 23, соединяющий третий выход блока управления 5 со вторым управляющим вхо дом регистра произведения I, канал 24, соединякяций четвертый выход блока управления 5 с третьим управляющим входом регистра произведения 1, канал 25, соединяющий пятый выход блока управления 5 со вторым входом счетчика тактов 9, канал 26, соединяющий шестой выход блока управления 5 с третьим входом счетчика 9, канал 27, соединяющий информационный выход блока информационной разгрузки 7 со вторым информационным входом регист ра произведения 1, канал 28, соединякщий седьмой выход блока управления 3 с первым входом счетчика циклов 8, канал 29, соединяющий первый выход реверсивного счетчика циклов 8 со вторым входом блока управления 5, канал 30, соединяющий второй выхо реверсивного счетчика циклов 8 с тре тьим входом блока управления 5, канал 31, соединяющий третий выход реверсивного счетчика циклов 8 с управляющим входом блока информационной разгрузки 7, канал 32, соединякщий управляющий выход блока информационной разгрузки 7 с четвертым входом блока управления 5, канал 33, соединянщий второй выход схемы сравнения количества тактов 10 со вторым входом счетчика циклов 8, каяал 34, 0510 соединяющий второй выход схемы сравнения количества тактов 10 с четвертым управляющим входом регистра произведения 1, канал 35, соединяющий второй выход схемы сравнения количества тактов 10 с управляющим входом регистра множителя 4, канал 36, соединякяций выход регистра множителя 4 с информационным входом узла выдачи разряда 6, канал 37, соединяющий управлякщий вход устройства с пятым входом блока управления 5, канал 38, соединяющий восьмой выход блока управления 5 с выходом индикации устройства. Регистры 3 и 4, а также сумматор 2 имеют по и, а регистр 1-2п 1 -ичнь1х разрядов. Счетчик тактов 9 содержит3Boa,tS двоичных разрядов, а реверсивный с етчик циклов 8 jc(ia,flL двоичных разрядов. Узел выдачи 6 представляет собой набор элементов И, на первые входы которых подается двоичное представлениеk-ичного разряда, а на вторые входы - управляющий сигнал. Блок информационной разгрузки содержит узел местного управления 39, узел анализа 40, реверсивный счетчик номера разрядов информационной разгрузки 41, реверсивный счетчик 42, накапливающий одноразрядшз1й сумматор 43 по модулю k, узел вадачи 44, схему сравнения 45, регистр информационной разгрузки 46, первый коммутатор 47, второй коммутатор 48, канал 49, соединяющий первый выход узла местного управления 39 с первым управляющим входом второго коммутатора 48, канал 50, соединяющий второй выход узла местного управления 39 с.управляющим входом узла анализа 40, канал 51, соединяющий третий выход узла местного управления 39 с управляющим входом узла выдачи 44, канал 52, соединяю1цйй четвертый выход узла местного управения 39 с первым управляющим входом первого коммутатора 47, канал 53, соединяющийпятый выход узла местного управления 39 с управляющим вхоом схемы сравнения 45, каналы 54 55, соединяющие первый и второй ыходы узла анализа 40 соответствено с первым и вторым входами узла естного управления 49, каналы 56 57, соединяюоще третий и четвертый ыходы узла анализа 40 соответствено с первым и вторым входами счетчиII , 9 ка 41, канал 58, соединяющий первый выход реверсивного счетчика 41 с первым информационным входом узла анализа 40, канал 59, соединяющий второй выход реверсивного счетчика 41 со вторым входом первого коммутатора 47, канал 60, соединяющий ин формадионный вход узла выдачи 44 со входом постоянного значения г, канал 6I, соединяющий третий выход узла местного управления 39 со вторым входом реверсивного счетчика 42 канал 62, соединяющий выход узла вы дачи 44 со вторым входом сумматора 43, канал 63, соединяющий второй выход сумматора 43 со вторым входом вт рого коммутатора 48, канал 64, соеди няющий первый сумматора 43 со вторым информационным входом узла а лиза 40, каналы 65, 66 и 67, соединяющие первый, второй, третий выходы реверсивного счетчика 42 соответственно с третьим информационным вход узла анализа, четвертым информационным входом узла анализа, первьм B :дом второго коммутаторв 48, канал 6 соединяющий выход .второго ком1 1утатора 48 со вторым входом регистра 46, канал 69, соединяющий первьй вы ход первого коммутатора 47 с первым Входом реверсивного счетчика 42, канал 70, соединяющий второй вьпсод первого коммутатора 47 с первым выходом, сумматора 43, канал 71 , соеди няющий второй выход регистра 46 с первым входом схемы сравнения 45, канал 72, соединяющий третий выход регистра 46 с входом первого коммутатора 47, канал 73, соединяющий первый выход схемы сравнения 45 с управляющим входом, регистра 46, канал 74, соединяющий вход постоянного значения О со вторым входом схемы сравнения 45, канал 75, соеди няющий второй выход схемы сравнения 45 с четвертым входом узла местного управления- 39, канал 76, соединяющий третий выход реверсивного счетчика 41 со вторым управлякшшм входом второго коммутатора 48. Реверсивный счетчик 41 содержит И- двоичных разрядов. Реверсивный счетчик 42 coдepжит Eo KL двоичны разрядов. Регистр 46 содержит 2п k H4HMX разрядов Узел анализа 40 содержит первую схему сравнения 77, вторую схему сравнения 78,, элемент И 79, элемент ИЛИ 50, элемент И 81, элемент И 82, третью схему сравнения 83, четвертую сгему сравнегшя 84, элемент ИЛИ 85, элемент ШШ 86, канал 87, соединякиций вход постоянного значения нуль со вторым входом первой схемы сравнения 77, канал 90, соединяющий первый выход первой схемы сравнения 77 с первым входом элемента И 79, канал 91, соединяющий второй выход первой схемы сравнения 77 со вторым входом элемента И.ПИ 80, канал 92, соединяющий вход постоянного значения со вторым входом второй схемы сравнет1я 78, канал 93j соединяющий первый выход второй схемы сравнения 78 со вторььм вхо дон элемента И 79, канал 94, соединяющий второй выход второй схемы сравнеьшя.78, с первым входом элемента ИЛ- 80, канал 95. соединякедий выход элемента ИЛИ 80 со вторым входом элемента И 8, канал 96, соединякнций выход элемента ИЛИ 80 с первым входом элемента ИЛИ 86, канал 97, соединяющий выход элемента И 79 с первым входом третьей схемы сравнения 83, канал 98, соединяющий вход постоянного значеш-1я 1 с третьим входом третьей схемы сравнения 83, канал 99, соединяюи ий первый выход третьей схемь сравнения 83 с первым входом четвертой схемы сравнения 84, канал 100, соединякадий первый выход сравHemifi 84 со вторым входом элемента ИЛИ 86, канал 101, соединянщий первьй выход схемы сравнения 84 со вторь М входом элемента И 82, канал 102, сое/диняющии вход постоянного значения k-1-r с третьим входом схемы сравнения 84, канал ЮЗ, соединякщий второй выход третьей схемы сравнения 83 . со вторым входом элемента ИЛИ 85, канал 104, соединяющий второй выход четвертой схемы сравнения 84 с первым выходом элемента ИЛИ 85. Узел местного управления 39 содержит элемент ИЛИ 105, элемент задержки 106, элемент задержки 107, элемент И 108, элемент задержки 109, элемент И ПО, элемент задержки 1 1 1 элемент И 112, элемент задержки 113, элемент задержки 114, канал 115, соединяющий выход элемента ИЛИ 105 с входом элемента задержки 106 канал 116, соединяющий выход элемента задержки 106 с входом элемента за держки 107, канал 117, соединяющий выход элемента зацержки 07 с первым входом элемента и 108, канал 118, соединякщий выход П элемента И 108 с входом элемента за держки 109, канал 119, соединяющий выход элемента задержки 109 с первы входом элемента И 110, канал 120, соединяющий выход элемента задержки 103 с первым входом элемента И 112, канал 121, соединяющий выход элемента И ПО с входом элемента задерж ки 111, канал 122, соединяющий выход элемента задержки 111 с первым входом элемента ИЛИ 105 канал 123, соединяющий выход элемента И 1-12 с входом элемента задержки 113, канал 124 соединяющий выход элемента задержки ИЗ, с входом элемента задержки 114, канал 125, соединяющий выход элемента задержки 114 с третьим входом элемента ИЛИ 105. Блок управления 5 содержит усилители-формирователи 126 и 134, элементы задержки 127, 129 и 1.31, эле мент ИЛИ 128, элементы И 130, 132 и 133, канал 135, соединямций выход усилителя 126, с входом элемента задержки 127, канал 136, соединяющий выход элемента задержки 127 со вторы входом элемента ИЛИ 128, канал 137, соединяющий-выход элемента ИЛИ 128 с входом элемента задержки 129, кана лы 138, 139 и 140, соединяющие выход элемента задержки 129 соответственно со вторыми входами элементов И 130, 132 и 134, канал 141, соединяющий выходэлемента И 130 с входом элемента задержки 131, канал 142, соединяющий выход элемента задержки 131 с первым входом элемента ИЛИ 128, канал 143, соединяющий выход элемента И 143 с третьим входом элемента ИЛИ 128, В исходном состоянии в регистре множителя 4 находится k-ичный код множителя. В регистре множимого 3 k-ичный код мно жимого. Регистр произведения 1, сумматор 2, счетчик тактов 9 установлены в нулевое состояние сигналами, поступаю щими с блока управления, 5 по каналам 23, 22 и 25 соответственно. Под действием управляющего сигнала, поступающего с блока управления 5 по кана лу 28 в реверсивный счетчик 8 записы вается число п. Работа устройства для умножения начинается с момента поступления управляроцего сигнала по каналу 37 устройства. В качестве такого сигнала может быть использован, например, упранлягаций сигнал, формируемый в це тральном устройстве управления ариф- 705 метического устройства, в котором применяется в качестве отдельного функционального блока предлагаемое устройство. Управляющий сигнал, приходящг1ц по. входному каналу 37, запускает в работу блок управления 5, Процесс умножения двух П разрядных чисел, представленных k-нчными кодами в избыточной (г, k) - системе счисления, Б общем случае состоит из собственно операции умножения этих чисел и коррекции результата, связанной с выполнением операции информационной разгрузки. Собственно операция умножения выполняется за п 1ДИКЛОВ. В каждом очередном цикле множимое умножается на соответствующий i-и (,2,.,.,п) разряд множителя. Цикл реализуется за Е+1 тактов, где L - цифра разряда множителя с номером t, В первом такте каждого цикла из блока управления 5 по каналу 21 на узел 6 подается управляющий сигнал. Под действием этого сигнала значение последнего разряда регистра множителя 4 по каналу 36 через узел 6 подается на схему сравнения количества тактов 10. На второй вход схемы 10 по каналу 17 подается значение кода, хранящегося в счетчике тактов 9. .Если коды не совпадают, то на выходе схемы сравнения 10 появляется сигнал, который по каналам 15 и 19 поступает на управЛякщие входы регистров множимого 3 и произведения 1 соответственно. Под действием этого сигнала из регистров 3 и 1 по каналам 14 и 12 соответственно на сумматор 2 подаются коды множимого и частичного произведения. Результат суммирования с выхода сумматора 2 по каналу 13 передается в регистр произведения 1. Одновременно с поступлением сигналов на регистры 3 и 1 сигнал с выхода схемы сравнения количества тактов 10 поступает также по каналу 20 на первый вход блока управления 5. Под действием этого сигнала в блоке 5 формируется управля1(щий сигнал, поступающий о каналу 26 на счетчик тактов 9 и величивающий его значение на единицу. В случае, когда коды не совпаают, на этом выполнение первого така заканчивается. Операции, аналогичые операциям при реализации первого акта, продолжаются до тех fiop, поа не совпадут коды, поступающие выходов узла 6 и счетчика 9 на входы схемы сравнения количества тактов 10, т.е.. столько раз j, чему равно значение t очередной цифры множителя, t тактов очередного цикла одинаковы, ) + 1 такт цикла .выполняется, когда коды, поступающие на входы схемы сравнения 0, совпадают .Если значение очередной цифры множителя равно нулю, то выполняется .только этот такт. В этом случае со второго выхода схемы сравнения 10 по каналам 8, 35, 34 и 33 на входы счетчика тактов 9, регистров 4 и i J а-также реверсивного счетчика циклов 8 соответственно5 поступает управляющий сигнал. Под действием этого сигнала счетчик 9 устанавливается в состояние нуль, содержимое регистра множителя 4 и регистра произведения сдвигается на один разряд вправо, значение реверсивного счетчика циклов 8 уменьшается на единицу. На этом выполнение J-ro (,2,,,.,п) цикла собственно one рации умножения заканчивается. .При выполнении циклов с номерами (1-nзначение счетчика 8 не становится . равным нулю пос-пе их окончания,, Б этом случае с первого выхода счетчика 8 по каналу 29 в блок управления 5 поступает сигнал, под действием которого выполняется следующий цикл собственно операции умно жения. После окончания последнего п-го цикла собственно операции умножения значение счетчика 8 становится равным нулю. В этом же случа со второго выхода счетчика 8 по ка налу 30 в блок управления 5 поступает сигнал, в ответ на который бл управления выдает управляющий сигнал по каналу 24. Под действием эт го сигнала код регистра произведения 1, где находится результат соб ственно умножения по каналу I, пе ред ается в блок информационной раз грузки. Одновременно с передачей сигнала по каналу 30, с третьего в хода реверсивного счетчика циклов по каналу 31 в блок информационной разгрузки 7 поступает сигнал, иниц ирукидай начало коррекции кода собственно умножения. В блоке информационной разгрузк 7 код результата собственно ния анализиуется с целью установления соответствия формы представления результата и формы представ;;16ления чисел с фиксированной запятой в позиционной избыточной (г, k) системе счисления. Соответствие зак.пючается в наличии п нулей между положением запятой и первым значащим разрядом результата. Если соответствие устанавливается, операция информационной разгрузки над результатом собственно умножения не выполняется Сигнал соответствия из блока 7 по каналу 32 поступает на блок 5 и сви- детельствует о завершении операции умножения. Результат умножения этих двух чисел находится в регистре произведения 1. Если же соответствие не устанавливается, то в блоке информационной разгрузки 7 над результатом собственно умножения осуществляется операция информационной рс1згрузки5 пока результат не станет соответствовать форме представления чисел с фиксированной запятой в позиционной избыточной (г, k) системе счисления Скорректированный результат умножения с блока информаци:онной разгрузки 7 по каналу 27 поступает в регистр произведения Одновременно с блока информационной разгрузки 7 по ка.налу 32 в блок управления 5 поступает сигнал об окончании операции умножения Блок информационной разгрузки 7 работает так Б исходном состоянии в регистре информационной разгрузки 46 находится код результата выполнения собственно операции умножения. Реверсивный счетчик 42 и накапливающий одноразk 43 нарядньш сумматор по модулю ходится в нулевом состоянири В реверсивный счетчик номера разрядов информационной разгрузки 41 занесен код 1, По первому сигналу управляющему, поступающег-1у с узла местного управления 39 по каналу 53 на схему сравнения 45, происходит сравнение старших разрядов регистра 46, поступающих на схему сравнения 45 по каналу 71э с кодом нуля, поступающего на схему сравнения 45 по каналу 74, Если П-( старших разрядов имеют нулевые значения, то с первого выхода схемы сравнения 45 по каналу 73 на регистр 46 поступает сигнал, под действием которого код с регистра 46 по каналу 27 пep€y.aeтcя в регистр произведения I, Этот код и является окончательнь м кодом результата выполнекия операции умножения. Одновременно с сигналом, передаваемым по каналу 73. по каналу 32 поступает нал в блок управления 5 и свидетел ствует об окончании операции умножения. Если же щ старших разрядов не равны нулю, то в этом случае со второго выхода схемы сравнения 45 в узел местного управления 39 по-ка налу 75 поступает сигнал о неравенстве кодовJ поступающих на входы сх мы сравнения 45. По этому сигналу из узла местного управления 39 по каналу 52 выдается управляющий сигнал, разрешающий передачу i-ro и ( + Г)-го разрядов регистра 46 через первый коммутатор 47 в реверсивный счетчик 42 и накапливающий сумматор 43. Номер i-ro разряда определяется кодом, хранящимся в счетчике 41.. Поскольку информационная разгрузка начинается с первого и вт рого разрядов, то начальное значение счетчика 41 равно единице. Значение счетчика 41 по каналу 59 пост пает на коммутатор 47, разряд регистра 46 с номером i. через коммутатор 47 по каналу 69 поступает в реверсивный счетчик 42, а разряд с номером i+1 через коммутатор 47 по каналу 70 поступает в сумматор 43. Значение разрядов с номерами i, i+1, хранящиеся в счетчике 42 и сумматоре 43 соответственно, анализируются в устройстве анализа 40. При этом для работы блока информационной разгрузки существенное значение имеют два Случая: значение разряда с номером L равно нулю, либо значение разряда с номером i+1 превышает значение k-1-r значение разряда с номером i не равно нулю, а значение разряда с номером i+1 не превышает значение k-1-r. В пер вом случае дальнейшая работа блока информационной разгрузки состоит в следующем. Сигнал с первого выхода узла анализа 40 по каналу 35 посту пает на первый вход узла местного управления 39. Под действием этого сигнала в узле местного управления 39 формируется сигнал, который по каналу 50 поступает на управляккций вход узла анализа 40. В узле 40 фор мируется сигнал, поступакиций по каналу 56 на первый вход счетчика 41 и увеличивающий его значение на еди ницу. На этом такт работы блока информационной разгрузки saKat MHsaeT 518 ся. Увеличение содержимого счетчика 41 на едшчицу означает, что .в следующем такте работы блока информационной паз грузки анализируются значе НИН разрядов регистра 46 со сдвигом вправо на единицу. Во втором случае дальнейшая работа блока информационной разгрузки зависит, вопервых от значения кода, хранящегося в счетчике 41. Именно если в этом счетчике записан код единицы, то в блоке реализуется операция информационной разгрузки. Если же код в счетчике 4I отличен от кода единицы, то в этом случае работа блока информационной разгрузки определяется еще соотношением между значением i-ro разряда и величиной k-1-r. При их равенстве значение счетчика 41 уменьшается на единицу и работа с очередными разрядами регистра информационной разгрузки заканчивается. Если эти значения не равны, то над разрядами с номерами i и i+I ,выполняется информационная разгрузка. Информационная разгрузка выполняется так. Из узла анализа 40 по каналу 54 на второй вход узла местного управления 39 поступает сигнал начала разгрузки. По действием этого сигнала в узле 39 вырабатывается два последовательно формируемых управляющих сигнала. Первый управляющий сигнал по каналам 61 и 51 поступает на вторые входы реверсивного счетчика 42 и cxei-ы И 44 соответственно. По дейстБ1;ем этого сигнала в реверсивном счетчике 42 и накапливающем сумматоре 43 выполняется операция информационной разгрузки по формуле {х -1) Л (х. +г) где xi, - значение и (i + l)-ro разрядов; N идентификатор операции конъюнкции (данном случае означает одновременность) ; г - основание используемой позиционной избыточной (г, k) системы счисления. Значение г на вход сумматора 43 подается по канау 62 с выхода узла 44. Второй управяющий сигнал по каналу 49 поступает на второй коммутатор 48. Под ействием этого сигнала вновь полученные значения i-ro и (i+1)-го разядов из счетчика 42 и сумматора 43 о каналам 67 и 63 соответственно ерез коммутатор 48 передаются по аналу 68 в регистр информационной азгрузки 46. На этом очередной такт аботы блока информационной paarjjyaкн заканчивается. При равенстве экачений i ГО разряда и величинь kl-r в случае, .когдй. в счетчике 4 хранится код, отлич1Лз1й от единицы, в узле анализа 40 вырабатывается сиг нал, который по каналу 55 передается на первый вход узла местного управления 39, Иод действием этого сигнала в узле формируется соответствующий управляющий сигна.г1. Он передается по каналу 50 на узел анализа 40. Под eiO действием в узле 34 формируется сигнал, который по ка налу 57 поступает на второй вход счетчика 41 и уменьшает его значение на единицу. На этом очередной такт работы блока информационной разгрузки заканчивается. Следу1аций такт работы блока информационной разгрузки начинается с выработки узлом мест ного управления 39 управляющего сигнала, который по каналу 53 передается на вход схемы сравнения 45; Номера разрядов, подлежащих информационной разгрузке, определяются значением кода, xpaapiMoro в реверсивном счетчике 4. Блок информационной раз грузке работает до тех пор, пока п. старших разрядов регистра 46 не имешт нулевых значений. Когда п, разрядов имеют нулевые значения, с первого выхода схемы сравнения 45 по кана.пу 73 на регистр 46 поступает сигнал, под действием которого код с регистра 46 по каналу 27 передаетс в регистр произведения 1. Этот код и яштяется окончательным кодом результата операции умножения. Одновр менно с сигналом, передаваемым по каналу 73, но каналу 32 поступает с нал в блок управления 5 (фиг. 1) и свидетельствует об окончании операции умножения. Работа узла анализ 40 заключается в фор даровании; всех условийJ необходимых для работы бло ка информационной разгрузки. Сравне ние i-го разряда -с постоянным значе нием О осуществляет первая схема сравне1шя 77. Сравнение {1+1)-го ра ряда с постояньаш значением k-1-r осуществляет вторая схема сравнения 78, В первом случае, сигнал о равенстве разряда с номером i нулю, либо сигнал о том, что значение разряда номером i + 1 превъшает значени:е k-1поступают соответственно по каналам 91 и 94 на второй и первый входы 5. 20 элемента ШТИ 80, Сигнал с выхода элемента HJM 80 поступает по каналу 95 на второй вход злемента И 81, а по каналу 96 через элемент ИЛИ 86 этот сигнал по каналу 55 поступает на первый вход угла местного управления 39 блока информационной разгрузки (фиг. 2). Управляющий сигнал , поступает с выхода узла местного управле1-1ия 39 по каналу 50 на первые входы элементов И 8 и 82. Так как на втором входе элемента И 81 разрешающий сигнал, то управляюций сигнал проходит через элемент И 81 и по каналу 56 поступает на первый вход реверсивного счетчика номера разрядов информационной разгрузки 41 (фиг, 2), увеличивая его значение на единицу,. Во втором случае сигнал ,о неравенстве разряда нулю, а также сигнал о том, что значение (i+IJ-ro разряда не превьшает значение , поступают соответственно по каналам 90 и 93 на первый и второй входы элемента И 79. На выходе .элемента И 79 формируется потенциал второго случая работы блока информационной разгрузки. Этот потенциал по каналу 97 поступает на первый вход третьей схемы сравнения 83 и разрешает сравнение значения реверсивного номера разрядов информационной разгрузки 41 и постоянного значения единица. Значение счетчика 41 поступает на второй вход 83 по каналу 38, а значение единица поступает на третий вход схемы 83 по каналу 98. Если, значение счетчика 41 равно единице, то сиг.нал со второго выхода схем1з сравнения 83 по каналу 103 поступает на второй вход элемента ИЛИ 85. Сигнал с выхода злемента И1ЯИ 85 по каналу 54 поступает на второй .вход узла местного управления 39 блока инфоомационной разгрузки 7, В блоке информационной разгрузки 7 выполняется операция информационной разгрузки как описывалось .выше. Если код в счетчике 41 отличен от кода единица, то сигнгш с первого выхода схемы сравнения 83 по каналу 99 поступает на первый вход схемы сравнения 84 и разрешает сравнение 1-го разряда с постоянным значением k-1-г. Если значение t-го разряда равно величине k-1-r, то сигнал с первого выхода сравнения 84 по аналу 100 поступает на второй вход элемента ИЛИ 86, а по каналу 101 на второй вход элемента И 82. С выхода элемен та ИЛИ 86 сигнал по каналу 55 поступает на первый вход узла местного управления 39 (фиг. 2). Управляющий сигнал поступает с выхода узла 39 по каналу 50 на первые входы эле ментов И 81 и 82. Так как в этом случае на втором входе элемента И 82 разрешающий сигнал, то управля ющий сигнал проходит через элемент И 82 и по каналу 57 поступает на вт рой вхощ реверсивного счетчика 41, уменьшая его значение на единицу. Если значение i-ro разряда не разно величине , то сигнал со второго выхода схемы сравнения 84 по каналу 104 поступает на первый вход элемента ИЛИ 85. С выхода элемента ИЛИ 85 сигнал поступает по каналу 54 на второй вход узла местного управления 39 и происходит выполнение операции информационной разгрузки. Работа узла местного управления заключается в выработке управляющей последовательности сигналов, необходимых для работы блока информационной разгрузки. После окончания опера ции собственно умножения сигнал с третьего выхода реверсивного счетчик циклов 8 (фиг. I) поступает по каналу 31 на второй вход элемента ИЛИ 10 и начинает формировать управляющую последовательность сигналов. Первый управлякшдай сигнал поступает в блок информационной разгрузки по каналу 53 через время Т после прихода сигнала по каналу 31. Время t 1,определя ется приемом кода из регистра произведения 1 (фиг. l) в регистр информа ционной разгрузки 46(фиг. 2) и формируется элемент задержки 106. Если с блока информационной разгрузки при ходит сигнал по каналу 75, то через время , выхода элемента И 108 формируется второй управляющий сигнал. Время Их определяется формирова нием сигнала на выходе схемы сравнения 45, Временной интервал g формирует элемент задержки 107. Второй управляющий сигнал поступает в блок информационной разгрузки 7 по каналу 52, Второй управлякнций сигнал проходит по каналу ИЗ через элемент задержки 109 с временем задержки .. Это время определяется появлением сигналов на выходах узла анализа 40 (фиг. 2). Если с выхода узла анализа 40 поступает сигнал по каналу 55, то на выходе элемента И 110 формируется третий управляющий сигнал, поступающий в блок информационной разгрузки 7 по каналу 50J Этот же сигнал, пройдя через элемент задержки 111 по каналу 122, поступает на первый вход элемента ИЛИ 105 и вызывает формирование управлякядей последовательности сигналов следующего такта работы блока информационной разгрузки. Временной интервал t ц элемента задержки III определяется установлением кода в реверсивном счетчике 41. Если с выхода узла анализа 40 поступает сигнал по канал 54, то с выхода элемента И 106 в блок информационной разгрузки 7 поступает четвертый управляюощй сигнал по каналам 61 и 51. Через временной интервал tg после формирования четвертого управляющего сигнала в блок информационной разгрузки 7 поступает по каналу 49 пятый управляющий сигнал. Временной интервал Ts определяется временем выполнения операции информационной разгрузки и формируется элементом задержки ПЗ. Пятый управляюпцш сигнал,пройдя через элемент задержки 114 с временем задержки tg поступает на третий вход элемента ИЛИ 105 и вызывает формирование управляющей последовательности следующего такта работы блока информационной разгрузки 7. Временной интервал Т Б определяется временем приема кода вновь образованных разрядов с номерами 5 и t+1 в регистр информационной разгрузки 46. Узел местного управления 39 прекращает свою работу в том случае, если отсутствует сигнал, приходящий из блока информационной разгрузки 7 по каналу 75. В этом случае блок информационной разгрузки 7 формирует сигнал, поступающий по каналу 32 в устройство умножения (фиг. 1) и определяющий окончание работы этого блока. Работа блока управления 5 начинается под действием входного управляющего сигнала, поступающего по входному каналу 37. Этот сигнал проходит через усилитель 126, с выхода которого в устройство умножения поступает первый управляющий импульс по каналам 23, 22, 25 и 28, Через время ti посе поступления в устройство для умноения первого управляющего импульса, с выхода элемента ИЛИ 128 в устройство поступает второй управляющий 23 импульс по каналу 2 i. Временной интервал t определяется нaибoльши из времен, требуемых; для занесения крда о в регистр I, сумматор 2, счетчик тактов 9, а также занесением кода числа п в счетчик циклов 8 (фиг. l). Временной интервал t фор мируется элементом задержки 127, Если в процессе работы устройс ва для умножения на блок управления 5 пррпсодит сигнал по каналу 265 то через время 12, формируемое элементом задержки 129 в устройство для умножения с выхода, элемента И 30 поступает третий управляющий импульс Время t определяется суммарным вре менем суммирования кодов,регистра i и регистра 3 и записью результата. суммироваю1Я в регистр i , Третий управляющий сигнал, пройдя через элемент задержки 131, по каналу 142 поступает на первый вход элемента ИЛН 128 и вызывает формирование управляющей последовательности сигна™ лов следугацего такта работы устройства для умножения. Временной интервал t элемента задержки 131 определяется временем установлением кода в счетчике тактов 9, Если же после окончания очередного i-ro (,2,.,,,п-1) цикла работы устройства flfiH умножения, управляюищй сиг нал поступает с выхода счетчика цик лов 8 по каналу 29, то в этом случа сигнал с выхода элемента задержки 129 через элемент И 132 поступает в канал 143 и передается- на элемент ИЛИ 128, вызывая формирование управ ляющей последовательности следующего цикла работы устройства для: умно жения. После окончания последнего п-го цикла работы устройства для ум ножения с выхода счетчика 8 по кана лу 30, поступает сигнал наэлемент И 133. В этом случае сигнал с выход элемента задержки 129 проходит элемент И 133 и по каналу 24 поступает на управляющий вход регистра произведения 1 устройства для умно жения (фиг. 1). Под действием этого сигнала код регистра 1 передается в блок информационной разгрузки 7. После окончания работы блока 7 по его выходному каналу 32 в блок упра Ленин 5 поступает сигнал окончания коррекции результата. После усиления (усилитель 134) этот сигнал поступает по выходному каналу 38 уст5ойства и может быть использован в ачестве сигнала окончания операции множения. Данное устройство умножения в изьпочной (г, k) системе счислеия позволяет практически примездать збыточные (r,.k) - системы счисления при построении арифметических устойств высокопроизводительшзгх ЦВМ. ОжидаемЕ)Гй экономический эффект or использования в ЭВМ предлагаемого стройства для умножения достигается за счет отсутствия сквозного переноса при вычислении суммь.: частичных произведений либо экономией аппаратур -1ых затрат по сравнению с устройствами для умножения,, в которых применяются специальные методы ускорения переносов при вычислении сумг.1ы частичных произведений. Уве/шчение быстродействия устройства для умножения зависит от числа разрядов сомножителей и определяется .по формуле ... .JiiiliMI /it; где tp - время распространения переноса из одного разряда в другойj п число разрядов операндов. Удельные временные затраты на реализацию собственно информационной разгрузки незначительны, Операг-шя информационной разгрузки может выполняться автономно, что создает предпочтительные условия для применения предлагаемого устройства в системах обработки инфорнахщи конвейерного типа. Формула и:)обретения 1. Устройство умножения, содержащее регистр множимого, регистр множителя, регистр произведершя, сумматор, блок управления, причем информационные входы сумматора соединены с выходом регистра множимого и первым выходом регистра произведения первый информационный вход которого соединен с выходом сумматора, отличающе еся тем, что, с целью расширения функциональных возможностей за счет реализации умножения в позиционной избыточной (г, k) - систем счисления, устройство содержит блок информационной разгрузки, реверсивный счетчик цик25лов, счетчик тактов, схему сравнения количества тактов, узел вьщачи разряда, причем второй выход регист ра .произведения соединен с информационным входом блока информационной разгрузки, выход младшего разряда регистра множителя соединен с инфор мационным входом узла выдачи разрядов, управляющий вход которого соеди нен с первым выходом блока управлеНИН,-а выход соединен с первым входом схемы сравне -шя количества тактов, второй вход которой соединен с выходом счетчика тактов, первый выхо схемы сравнения количества тактов соединен с управляющим входом регист ра множимого,первым управляющим вхо дом регистра произведения и первым входом блока управленияj второй выхо которого соединен с управляющим входом сумматора, второй и третий управляющие входы регистра произведения соединены соответственно с третьим .и четвертым выходами блока управления , второй выход схемы сравнения количества тактов соединен с управля кщим входом регистра множителя, четвертым управляющим входом регистра произведения и первым входом счетчика тактов, второй и третий входы которого соединены соответственно с пятым и шестым выходами блока управления, седьмой выход которого соединен с первым входом реверсивного сче чика циклов, второй вход которого со динен со вторым выходом схемы сравне ния количества тактов, первый, второй, и третий выходы реверсивного счетчика циклов соединены соответственно со вторым и -третьим входами блока управления и управляющим входо блока информационной разгрузки, ин-. формационный и управляющий выходы которого соединены соответственно со вторым информационным входом регистра произведения и четвертым входом блока управления, пятый вход которого соединен с управляюпщм входом уст ройства, выход индикации которого со динен с восьмым выходом блока управления. 2. Устройство по п. , отличающееся тем, что блок информационной разгрузки содержит узел местного управления, узел анализа, реверсивный счетчик номера разрядов информационной разгрузки реверсивный счетчик, накапливающий одноразрядный сумматор по модулю k. 5 узел выдачи, схему сравнения, регистр информационной разгрузки, пер.вьвЧ и второй коммутаторы, причем первый информационный вход регистра информа1ДИОННОЙ разгрузки соединен-с информационным входом блока, первый, второй и третий выходы регистра информационной разгрузки соединень соответ™ ственно с информационным.выходом бло ка,. первым информационным входом схемы сравнения и информационт)1м входом первого коммутатора, первьш и второй выходь которого соединены с первыми входами соответственно реверсивного счетчика и накапливающего одноразрядного сумматора по модулю k, первый, второй, третий, четвертый и пятый выходы узла местного управления соединены соответственно с первым управляющим входом второго коммутатора, управляняцим входом узла анализа, вторым входом реверсивного счетчика, первым управляющим входом первого коммутатора и управлякщим входом схемы сравнения , первьш и второй выходы узла анализа соединены соответственно с пер вым и вторым входами узла местного управления, третий и четвертьш выходы узла анализа соединены соответственно с первым и вторым входами реверсивного счетчика номера раз-, рядов информационной разгрузки, пер- вый, второй и третий выходы которого соединены соответственно с первым информационным входом у5яа ана.лиза,, вторым управляющим входом первого коммутатора и вторым управляющим входом второго коммутатора, первый выход накапливающего одноразрядного сумматора по модулю k .соединен со .вторым информационным входом узла анализа, первый, второй и третий выходы реверсивного счетчика соединены соответственно с третьим и четвертым информационными входами узла анализа и пер.вым информационным входом второго коммутатора, второй ннформационнь й вход которого соединен со .вторым выходом накапливающего одноразрядного сумматора о модулю k,, второй вход которого Соединен с выходом узла выдачи, упавлякщий вход блока соединен с треьим входом узла местного управлеия, первый выход схемы сравн-ения оединен.с управляющим входом регитра информационной разгрузки и упавляющим вьосодом блока, второй выход схемы сравнения сое дииен с четвертым входом узла местного управления, выход второго коммутатора со динен со BTOpbJM информационным входом регистра информационной разгруз ки, информагщонный вход узла выдачи соединен со входом постоянного знН чения г, управляющий вход узла выдачи соединен с третьим выходом узл местного управления, второй информационный вход схемы сравнения соед нен со входом постоянного значения Ю. 3, Устройство по пп. 1 и 2, о т л и ч а ю щ е е с я тем, что узел анализа содержит четыре схемы сравнения , три элемента И, три элемента ИЛИ, причем первый и второй входь( первой схемы сравнения соединены со ответственно с третьим входом узла и входом постоянного значения О, первый и второй входы второй схемы сравнения соединены соответственно со вторым входом узла и входом постоянного значения k-1-r, первый вход третьей схемы сравнения соединен с выходом первого элемента И, второй и третий входы третьей схемы сравнения соединены соответственно с первым входом узла и входом по стоянного значения 1, первый вход четвертой схемы сравнения соединен с первым выходом третьей схемы срав нения, второй и третий входы четвертой схемы сравнения соединены со ответственно с четвертым входом узла и входом постоянного значения k-l-r, первые входы второго и третьего элементов И соединены с управ ляю1а 1М входом узла, первые выходы первой и второй схем сравнения соед нены со входами первого элемента И, вторые выходы первой и второй схем сравнения соединены со входами перв го элемента ИЛИ) первый выход четвертой схемы сравнения соединен со вторым входом третьего элемента И, вторые выходы третьей и четвертой схем сравнения соединены со входами второго элемента ИЛИ,, выход первого элемента ИДИ соедине { со вторым вхо дом второго элемента И и первым вхо дом третьего элемента ИЛИ, второй в которого соединен с первьЫ выходом четвертой схемы сравнения, выходы второго и третьего элементов И соединены соответственно с третьим и четвертым выходами узла, выходы вт рого и третьего элементов ИЛИ соед нены соответственно первым и нторым выходами узла. 4е Устройство по пп. И 2 5 л и ч а ю щ е е с я тем, что узел местного управления содержи элементы И, ИЛИ задержки, причем первый вход элемента ИЛИ соединен с третьим входом узла, а выход - со входом первого элемента задержки, выход которого соединен с пятым выходом узла и входом второго элемента задержки, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с четвертым входом узла, а выход с четвертым выходом узла и входом третьего элемента задержки, выход которого соединен с первыми входами второго и треть.его элементов И,.второй вход второго элемента И соединен с первым входом узла, а выход - со вторым выходом узла и через четвертый элемент задержки - со вторым входом элемента ИЛИ, второй вход третьего элемента И соединен со вторым входом узла, а выходс третьим выходом узла и входом пятого элемента задержки, выход которого соединен с первым выходом узлй и входом шестого элемента задержки выход которого сое/щнен с третьим входом элемента ИЛИ, 5 Устройство по п, 5 отличающееся тем, что блок управления содержит усилители-формирователи, элементы И, ИЛИ и задержки, причем вход первого усилителя-формирователя соединен с пятым входом блока, а выход - со вторьм, третьим, пятым, седьмым выходами блока и входом первого элемента задержки, выход которогосоединен с первым входом элемента ИЛИ, выход которого соединен с первым выходом блока, и входом второго элемента задержки, выход которого соединен с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с первым, вторым и третьим входами блока, выход перво|го элемента И соединен с шестым выходом блока и через третий элемент задержки - со вторым входом элемента ИЛИ, третий вход которого соединен с выходом второго элемента И, выход третьего элемента И соединен с четвертым выходом блока, четвертый вход которого соединен со входом второго усилителя-формирователя, выход которого соединен с восьмым вьг/содом блока. Источники информации, npHiiflTbie во внимание при экспертизе ., Авторское свидегельство СССР № 224267, кл. G 06 F 7/38, 1967. 20705 2.Авторское свидетельство СССР № 326577, кл. G 06 F 7/38, 1970. 3,Карцев М,А. Арифметика цифровых машин. М. , Наука, 1969, с. 348, рис, 4-1 (прототип).

i

«r

t5

«vi

/ V / k /

S5 -«e

«Si

e

/

u

Авторы

Даты

1982-04-15—Публикация

1979-12-07—Подача