СП

4;

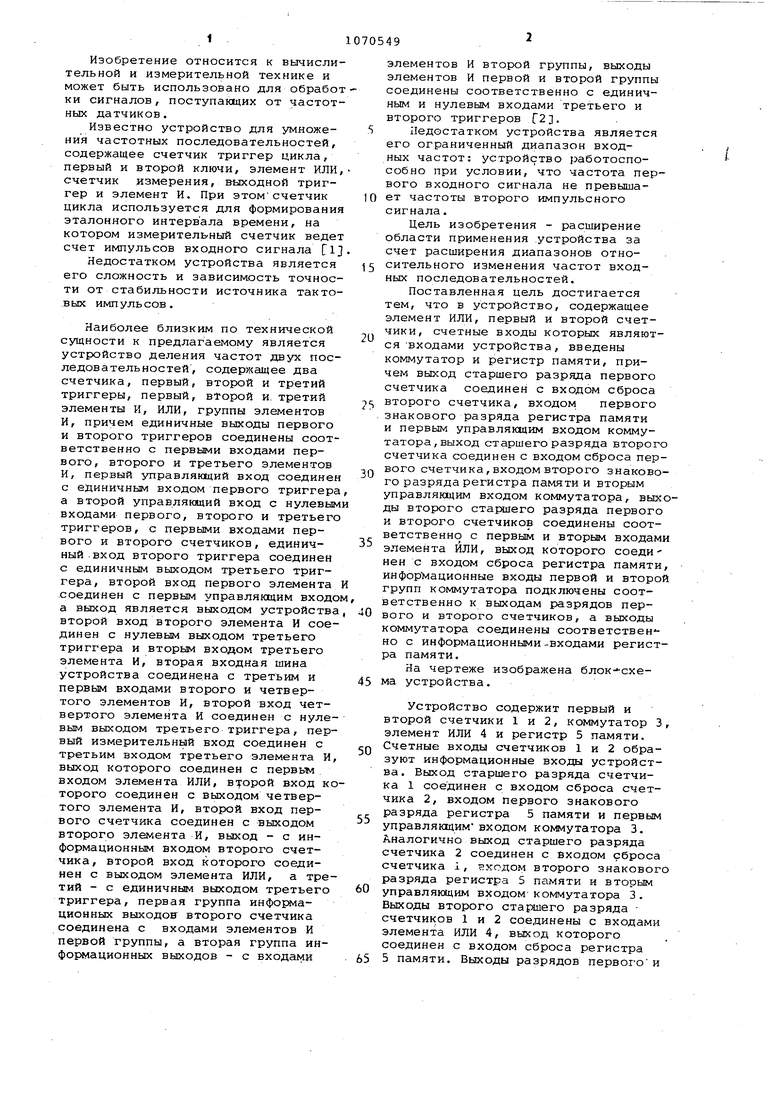

со Изобретение относится к вычислительной и измерительной технике и может быть использовано для обработ ки сигналов, поступающих от частотных датчиков. Известно устройство для умножения частотных последовательностей, содержащее счетчик триггер цикла, первый и второй ключи, элемент ИЛИ счетчик измерения, выходной триггер и элемент И. При этомсчетчик цикла используется для формирования эталонного интервала времени, на котором измерительный счетчик ведет счет импульсов входного сигнала ClJ Недостатком устройства является его сложность и зависимость точности от стабильности источника тактовых импульсов. Наиболее близким по технической сущности к предлагаемому является устройство деления частот двух последовательностей, содержащее два счетчика, первый, второй и третий триггеры, первый, второй и. третий элементы И, ИЛИ, группы элементов И, причем единичные выходы первого и второго триггеров соединены соответственно с первыми входами первого, второго и третьего элементов И, первый управлягаций вход соединен с единичным входом первого триггера а второй управляющий вход с нулевым входами первого, второго и третьего триггеров, с первыми входами первого и второго счетчиков, единичный .вход второго триггера соединен с единичным выходом третьего триггера, второй вход первого элемента соединен с первым управляющим входо а выход является выходом устройства второй вход второго элемента И соединен с нулевым выходом третьего триггера и вторым входом третьего элемента И, вторая входная шина устройства соединена с третьим и первым входами второго и четвертого элементов И, второй вход четвертого элемента И соединен с нулевым выходом третьего триггера, первый измерительный вход соединен с третьим входом третьего элемента И выход которого соединен с первьм входом элемента ИЛИ, B- opofi вход ко торого соединен с выходом четвертого элемента И, второй вход первого счетчика соединен с выходом второго элемента И, выход - с информационным входом второго счетчика, второй вход которого соединен с выходом элемента ИЛИ, а тре тий - с единичным выходом третьего триггера, первая группа инфор 1ационных выходо второго счетчика соединена с входами элементов И первой Труппы, а вторая группа информационных выходов - с входами элементов И второй группы, выходы элементов И первой и второй группы соединены соответственно с единичным и нулевым входами третьего и второго триггеров Г2. Недостатком устройства является его ограниченный диапазон входных частот: устройство работоспособно при условии, что частота первого входного сигнала не превышает частоты второго импульсного сигнала. Цель изобретения - расширение области применения устройства за счет расширения диапазонов относительного изменения частот входных последовательностей. Поставленная цель достигается тем, что в устройство, содержащее элемент ИЛИ, первый и второй счетчики, счетные входы которых являются -входами устройства, введены коммутатор и регистр памяти, причем выход старшего разряда первого счетчика соединен с входом сброса второго счетчика, входом первого знакового разряда регистра памяти и первым управляющим входом коммутатора, выход старшего разряда второго счетчика соединен с входом сброса первого счетчика,входом второго знакового разряда регистра памяти и вторым управляющим входом коммутатора, выходы второго старядего разряда первого и второго счетчиков соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соеди нен с входом сброса регистра памяти, инфорМационные входы первой и второй групп коммутатора подключены соответственно к выходам разрядов первого и второго счетчиков, а выходы коммутатора соединены соответствен но с информационными-входами регистра памяти. На чертеже изображена блок-схема устройства. Устройство содержит первый и второй счетчики 1 и 2, коммутатор 3, элемент ИЛИ 4 и регистр 5 памяти. Счетные входы счетчиков 1 и 2 образуют информационные входы устройства. Выход старшего разряда счетчика 1 соединен с входом сброса счетчика 2, входом первого знакового разряда регистра 5 памяти и первым управляющим входом коммутатора 3. Аналогично выход старшего разряда счетчика 2 соединен с входом сброса счетчика 1, яходом второго знакового разряда регистра 5 памяти и вторым управляющим входом коммутатора 3. Выходы второго старялего разряда счетчиков 1 и 2 соединены с входами элемента ИЛИ 4, выход которого соединен с входом сброса регистра 5 памяти. Выходы разрядов первогои второго счетчика подключены соотве ственно к информационньл входам п вой и второй групп коммутатора 3, выходы коммутатора 3 соединены соо ветственно с информационными входам регистра 5 памяти. Устройство работает следукщим образом. В исходном состоянии счетчики 1 и 2 и регистр 5 памяти обнулены, на выходах счетчиков 1 и 2, элемента ИЛИ 4 и коммутатора 3 - нуле вые сигналы. При поступлении на входы устрой ства последовательностей импульсов частоты F и 2 счетчики 1 и 2 про изводят подсчет входных импульсов. Под полным циклом N счетчика понимается число импульсов до появления единицы в его старшем разряде. Предположим, 4ifeF f и первой появляется единица в старшем разряде счетчика 1. Это происходит через интервал времени Т 1/ Р N . По этому признаку записывается единица в первый знаковый разряд регистра 5 памяти, значение P2-T NF2/F , накопленное в счетчике 2, переносится коммутатором 3 в регистр 5 памяти. В случае первым заканчивает свой цикл счетчик 2. В момент времени Т 1/F2N из счетчика 1 переносится накопленное в нем числр F -TrNF./Fj. Таким образом, в регистре 5 памяти образуется величина, пропорциональная модулю отношения двух частот входных импульсных последовательностей, а коды в знаковых разрядах 10 и 01 соответствуют значениям Fj/F и F,, /Fj . Элемент ИЛИ 4 осуществляет сброс регистра 5 памяти незадолго до обнуления результата. Таким образом, предлагаемое устройство по сравнению с прототипом имеет более широкую область применения за счет расширения диапазонов относительно изменения частот входных последовательностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1980 |

|

SU1062717A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧАСТОТ ДВУХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее элемент ИЛИ, первый и второй счетчики, счетные входы которых являются входами устройства, отличающееся тем, что, с целью расширения области применения путем расширения диапазонов относительного изменения . частот входных последовательностей, в него введены ко1 5иутатор и регистр памяти, причем выход старшего разряда первого счетчика соединен с входом сброса второго счетчика, входом первого знакового разряда регистра памяти и первым управляющим входом коммутатора, выход старшего разряда второго счетчика соединен с входом сброса первого счетчика входом второго знакового разряда регистра памяти и вторым управляющим входом коммутатора, выходы второго старшего разряда первого и второго счетчиков соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с входом сброса регистра i памяти, информационные входы первой и второй групп коммутатора подклюКЛ чены соответственно к выходеш разрядов первого и второго счетчиков, а выходы коммутатора соединены соответственно с информационными входами регистра памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Частотное делительное устройство | 1976 |

|

SU596945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-30—Публикация

1982-11-26—Подача