(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU985830A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

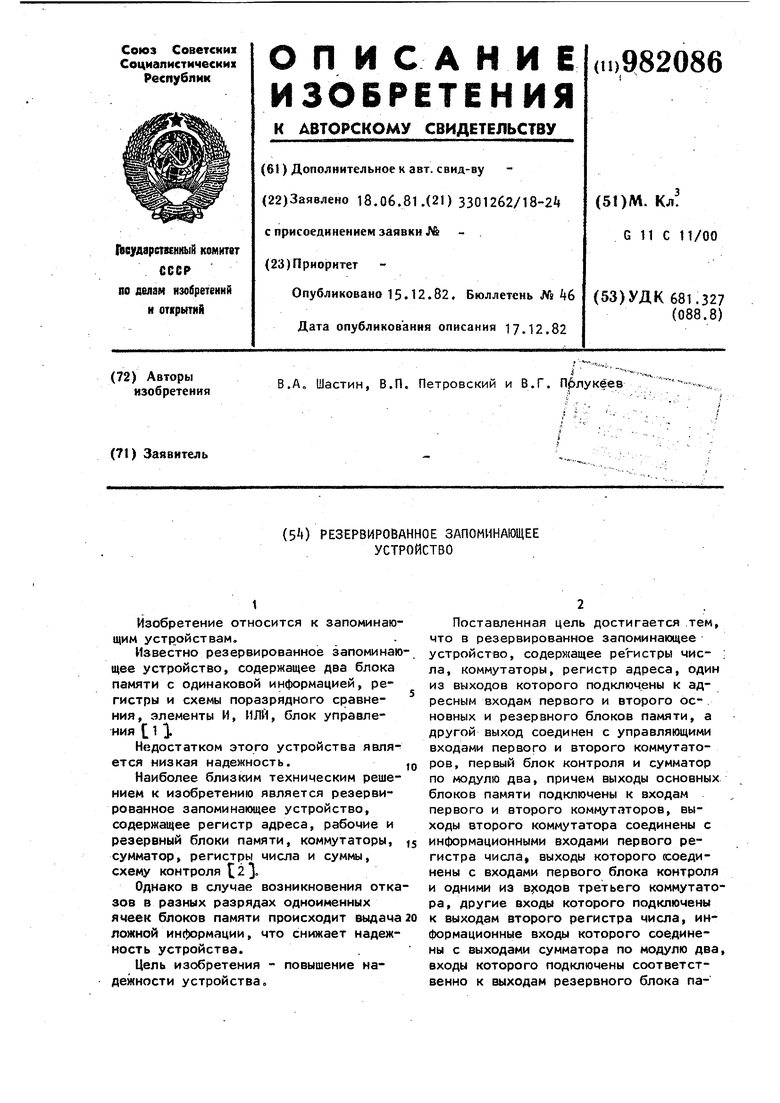

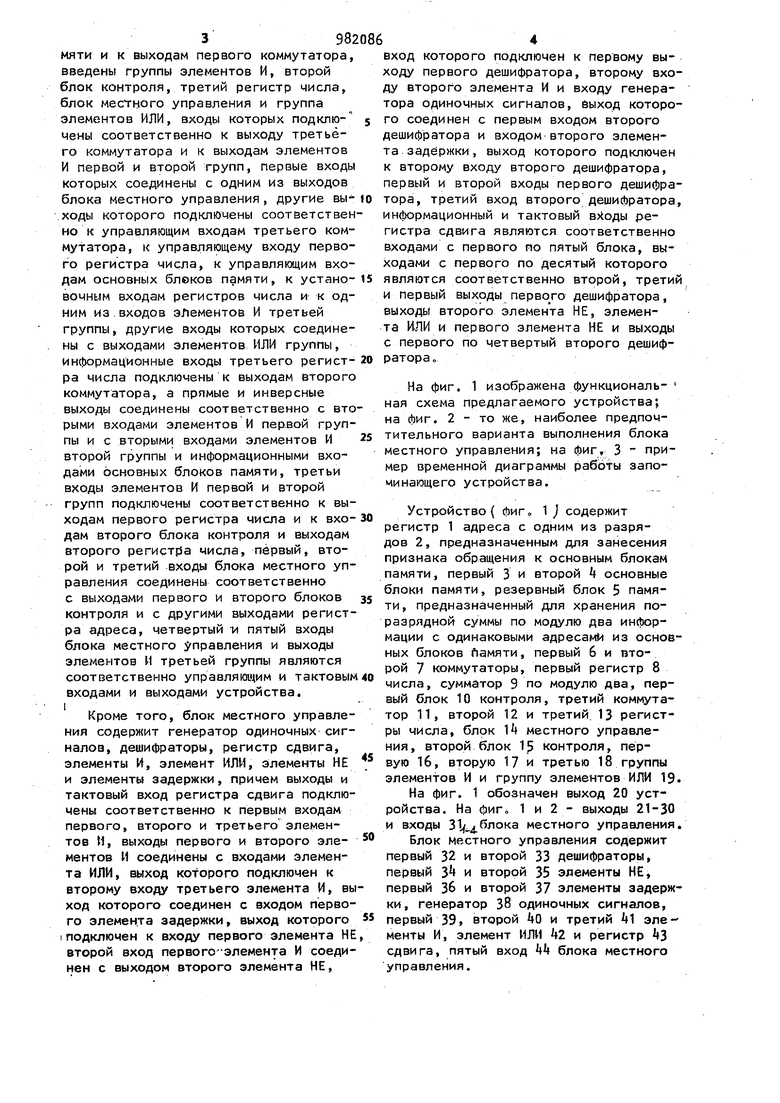

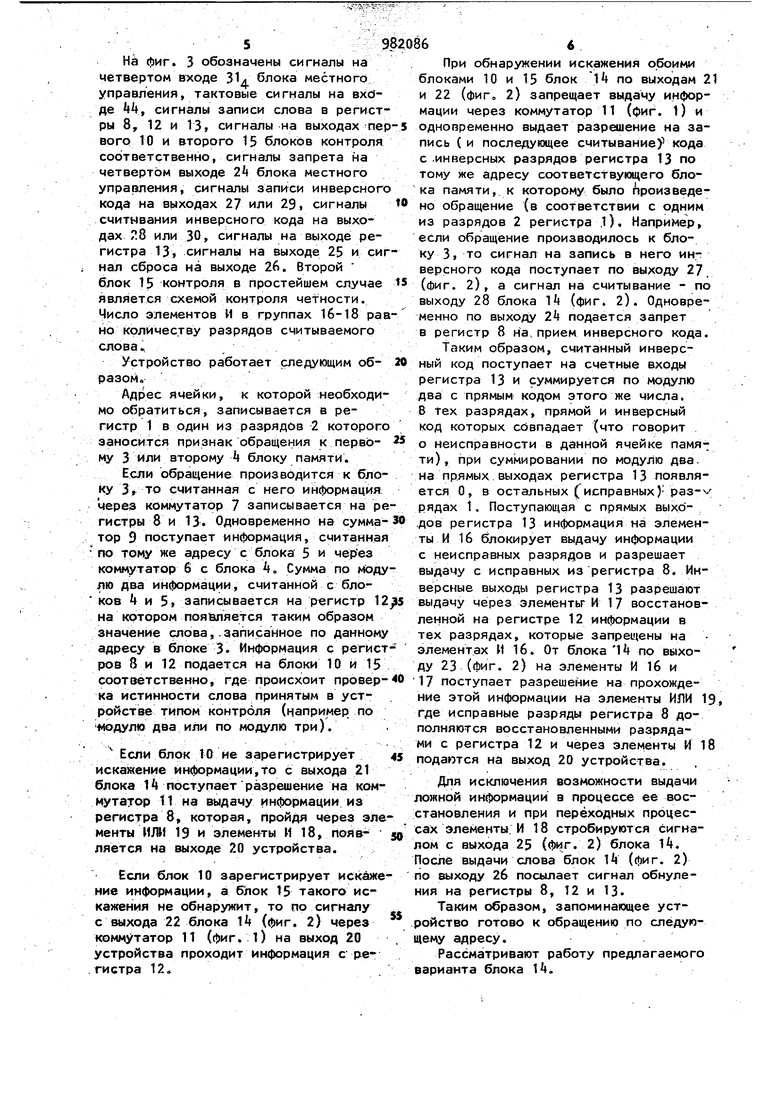

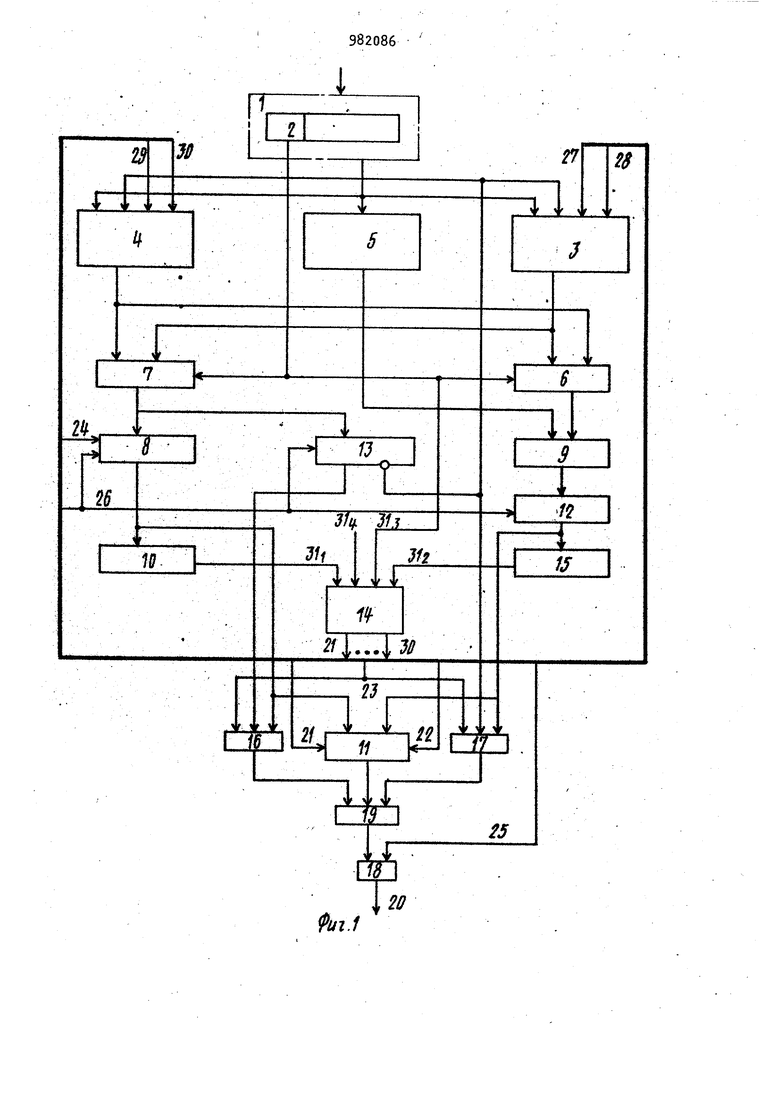

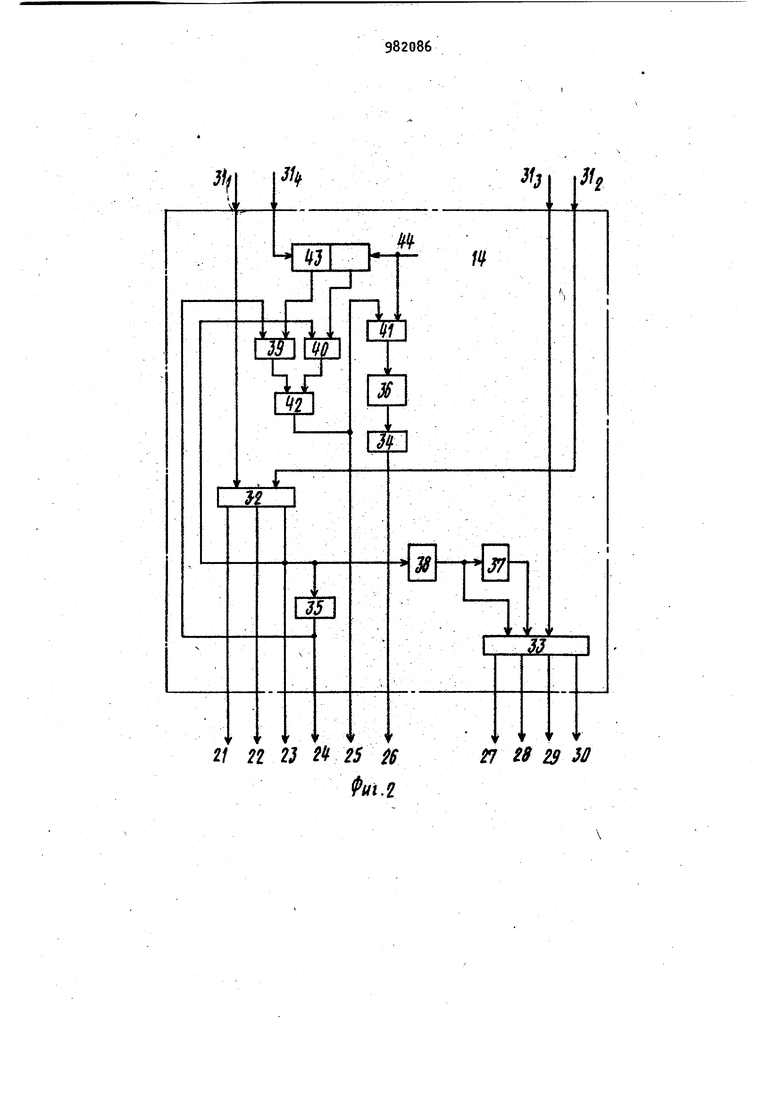

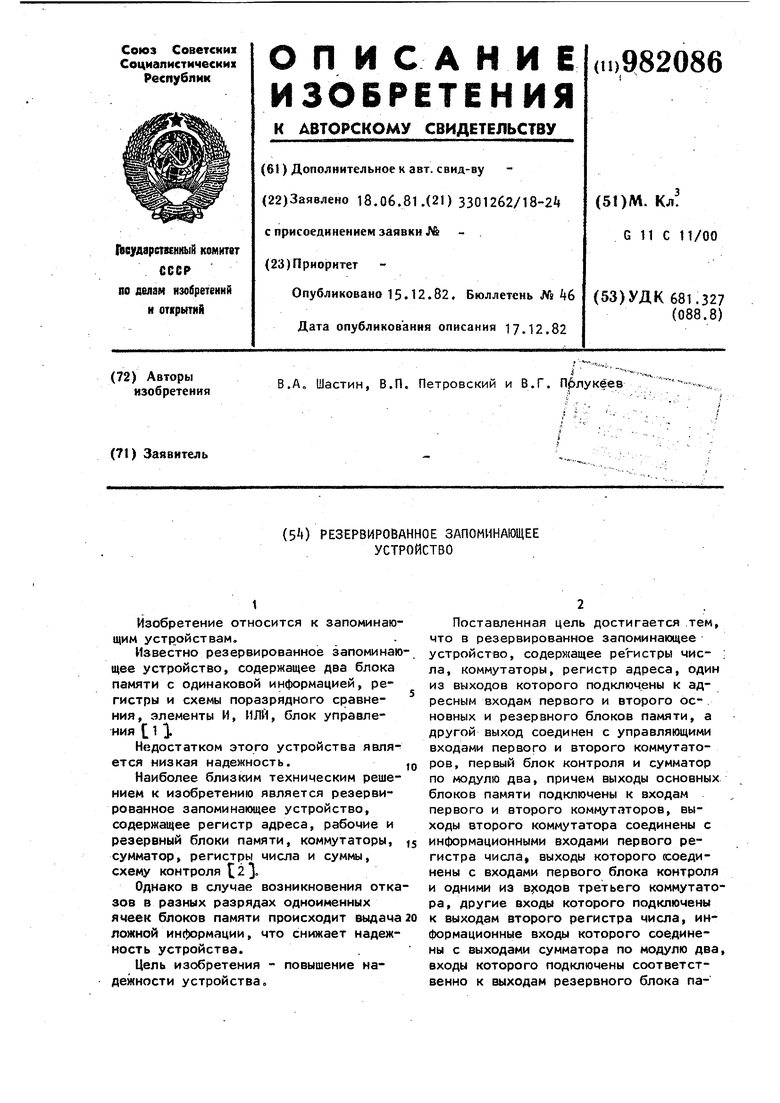

Изобретение относится к запоминаю щим устройствам. Известно резервированное запоминаю щее устройство, содержащее два блока памяти с одинаковой информацией, регистры и схемы поразрядного сравнения, элементы И, ИЛИ, блок управления 1 1 3. Недостатком этого устройства является низкая надежность. Наиболее близким техническим решением к изобретению является резервированное запоминающее устройство, содержащее регистр адреса, рабочие и резервный блоки памяти, коммутаторы, сумматор, регистры числа и сум№й, схему контроля 2 3 Однако в случае возникновения отка зов в разных разрядах одноименных ячеек блоков памяти происходит выдача ложной информации, что снижает надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается .тем, что в резервированное запоминающее устройство, содерхсащее регистры чис- ; ла, коммутаторы, регистр адреса, один из выходов которого подключены к адресным входам первого и второго основных и резервного блоков памяти, а другой выход соединен с управляющими входами первого и второго коммутаторов, первый блок контроля и сумматор по модулю два, причем выходы основных блоков памяти подключены к входам первого и второго коммутаторов, выходы второго коммутатора соединены с информационными входами первого регистра числа, выходы которого соединены с входами первого блока контроля и одними из вводов третьего коммутатора , другие входы которого подключены к выходам второго регистра числа, информационные входы которого соединены с выходами сумматора по модулю два, входы которого подключены соответственно к выходам резервного блока па3982мяти и к выходам первого коммутатора, введены группы элементов И, второй блок контроля, третий регистр числа, блок местного управления и группа элементов ИЛИ, входы которых подклюмены соответственно к выходу третьего коммутатора и к выходам элементов И первой и второй групп, первые входы которых соединены с одним из выходов блока местного управления, другие выходы которого подключены соответствен но к управляющим входам третьего коммутатора, к управляющему входу первого регистра числа, к управляющим входам основных блоков памяти, к установочным входам регистров числа и к одним из.входов элементов И третьей группы, другие входы которых соединены с выходами элементов ИЛИ группы, информационные входы третьего регистра числа подключены к выходам второго коммутатора, а прямые и инверсные выходы соединены соответственно с вто рыми входами элементов И пер-вой группы и с вторыми входами элементов И второй г эуппы и информационными входами основных блоков памяти, третьи входы элементов И первой и второй групп подключены соответственно к выходам первого регистра числа и к входам второго блока контроля и выходам второго регистра числа, первый, второй и третий входы блока местного управления соединены соответственно с выходами первого и второго блоков контроля и с другими выходами регистра адреса, четвертый -и пятый входы блока местного управления и выходы элементов И третьей группы являются соответственно управляюидим и тактовым входами и выходами устройства. Кроме того, блок местного управления содержит генератор одиночных си1- налов, дешифраторы, регистр сдвига, элементы И, элемент ИЛИ, элементы НЕ и элементы задержки, причем выходы и тактовый вход регистра сдвига подключены соответственно к первым входам первого, второго и третьего элементов И, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, вы ход которого соединен с входом первого элемента задержки, выход которого I подключен к входу первого элемента НЕ второй вход первого -элемента И соединен с выходом второго элемента НЕ, вход которого подключен к первому выходу первого дешифратора, второму входу второго элемента И и входу генератора одиночных сигналов, еыход которого соединен с первым входом второго дешифратора и входом второго элемента задержки, выход которого подключен к второму входу второго дешифратора, первый и второй входы первого дешифратора, третий вход второго дешифратора, информационный и тактовый вХоды регистра сдвига являются соответственно входами с первого по пятый блока, выходами с первого по десятый которого являются соответственно второй, третий и первый выходы первого дешифратора, выходы второго элемента НЕ, элемента НЛИ и первого элемента НЕ и выходы с первого по четвертый второго дешифратора „ На фиг. 1 изображена функциональная схема предлагаемого устройства, на фиг. 2 - то же, наиболее предпочтительного варианта выполнения блока местного управления; на фиг, 3 пример временной диаграммы работы запоминающего устройства. Устройство ( фиГо 1J содержит регистр 1 адреса с одним из разрядов 2, предназначенным для занесения признака обращения к основным блокам памяти, первый 3 и второй Ц основные блоки памяти, резервный блок 5 памяти, предназначенный для хранения поразрядной суммы по модулю два информации с одинаковыми адресами из основных блоков памяти, первый 6 и второй 7 коммутаторы, первый регистр 8 числа, сумматор 9 по модулю два, первый блок 10 контроля, третий коммутатор 11 второй 12 и третий. 13 регистры числа, блок I местного управления, второй блок 15 контроля, первую 16, вторую 17 и третью 18 группы элементов И и группу элементов ИЛИ 19. На фиг. 1 обозначен выход 20 устройства. На фиг 1 и 2 - выходы 21-30 и входы 3(л(пока местного управления. БЛОК Местного управления содержит первый 32 и второй 33 дешифраторы, первый 3 и второй 35 элементы НЕ, первый Зб и второй 37 элементы задержки, генератор 38 одиночных сигналов, первый 39, второй kO и третий 1 элементы И, элемент ИЛИ k2 и регистр ЦЗ сдвига, пятый вход kk блока местного управления. 59820 Н фиг. 3 обозначены сигналы на четвертом входе 31 блока местного управления, тактовые сигналы на Bxdде Ц, сигналы записи слова в регистры 8, 12 и 13, сигналы на выходах пер-5 вого 10 и второго 15 блоков контроля соответственно, сигналы запрета на четвертом выходе 2k блока местного управления, сигналы записи инверсного кода на выходах 27 или 29, сигналы считывания инверсного кода на выходах Г.8 или 30, сигналы на выходе регистра 13, сигналы на выходе 25 и сигнал сброса на выходе 26. Второй блок 15 контроля в простейшем случае 5 является схемой контроля четности. Число элементов И в группах 16-18 равно количеству разрядов считываемого слова., Устройство работает следующим об- 20 разом. Адрес ячейки, к которой необходиМО обратиться, записывается в регистр 1 в один из разрядов 2 которого заносится признак обращения к перво- 25 му 3 или второму k блоку памяти. Если обращение производится к блоку Зг то считанная с него информация: через коммутатор 7 записывается на регистры 8 и 13. Одновременно на сумма-30 тор 9 поступает информация, считанная по тому же адресу с блока 5 и через коммутатор 6 с блока , Сумма по Модулю два информации, считанной с блоков t и 5, записывается на регистр на котором появляется таким образом значение слова,.записанное по данному адресу в блоке 3. Информация с регистров 8 и 12 подается на блоки 10 и 15 соответственно, где происхоит nposep- 0 ка истинности слова принятым в устройстве типом контроля (например по «одулю два И.ПИ по модулю три). Если блок 10 не зарегистрирует искажение информации,то с выхода 21 блока Ц поступаетразрешение на ком мутатор 11 на выдачу информации из регистра 8, которая, пройдя через эл менты ИЛИ 19 И элементы И 18 появляется на выходе 20 устройства. Если блок 10 зарегистрирует искаж ние информации, а блок 15 такого искажения не обнаружит, то по сигналу с выхода 22 блока 1 (фиг. 2) через коммутатор 11 (фиг. 1) на выход 20 устройства проходит информация с регистра 12. 64 При обнаружении искажения обоими блоками 10 и 15 блок Н по выходам 21 и 22 (фиг, 2) запрещает выдачу информации через коммутатор 11 (фиг. 1) и одновременно выдает разрешение на запись (и последующее считывание) кода с .инверсных разрядов регистра 13 по тому же адресу соответствующего блока памяти, к которому было йроизведено обращение (в соответствии с одним из разрядов 2 регистра .1), Например, если обращение производилось к блоку 3, то сигнал на запись в него инверсного кода поступает по выходу 27. (фцг. 2), а сигнал на считывание - по выходу 28 блока Т (фиг. 2). Одновременно по выходу 2 подается запрет в регистр 8 на прием инверсного кода. Таким образом, считанный инверсный код поступает на счетные входы регистра 13 и суммируется по модулю два с прямым кодом этого же числа. В тех разрядах, прямой и инверсный код которых совпадает (что говорит „ неисправности в данной ячейке памяти), при суммировании по модулю два. на прямых выходах регистра 13 появляется О, в остальных ( исправных) разрядах 1. Поступающая с прямых выхо,дов регистра 13 информация на элементы И 16 блокирует выдачу информации с неисправных разрядов и разрешает йыдачу с исправных из регистра 8. Инверсные выходы регистра 13 разрешают выдачу через элементы И 17 восстановленной на регистре 12 информации в тех разрядах, которые запрещены на элементах И 16. От блока1 по выходу 23 (фиг. 2) на элементы И 16 и 17 поступает разрешение на прохождение этой информации на элементы ИЛИ 19, где исправные разряды регистра 8 дополняются восстановленными разрядами с регистра 12 и через элементы И 18 подаются на выход 20 устройства. Для исключения возможности выдачи ложной информации в процессе ее восстановления и при переходных процессах элементы И 18 стробируются сигналом с выхода 25 (фиг. 2) блока Н. После выдачи слова блок 1ч (фиг. 2) по выходу 26 посылает сигнал обнуления на регистры 8, 12 и 13. Таким образом, запоминающее устройство готово к обращению по следующему адресу. Рассматривают работу предлагаемого варианта блока 14. При операции считывания из блоков 2 и памяти на вход;31|( подается сигнал упра вления считыванием, который запускает-регистр 3 s который впоследствии формирует сигнал опроса элементов Я 18 и сброс регистров 8, 12 и 13. После контроля считанных слов блоками 10 и 15 на входы 31, и 312 блока 14 поступают,сигналы о наличии ошибок. Эти сигналы попадают на первый и второй входы дешифратора 32 соответственно (фиг. 2), который формируе уровень 1, при отсутствии сигнала , ошибки по первому входу на выходе 2 приналичий сигн&ла по-первому ВХОД.У и отсутствии по второму на выходе 2 а при наличии сигнала ошибки по обоим входам - на выходе 23 и одновременно уровень О на выходе 2k, Выходы 21 и 2 управляют коммутатором 11, выходы 23 элементами И 16...и 17s э на выходе 2if (фиг. 2) выдается запрет приема инверсного кода в регистр В С появлением 1 на выходе (фиг,2 запускается генератор 38, который выдает сигнал на запись ( и через элемент задержки 37 на считывание инверсного кода из регистра 13 в блоки или .4„ Эти сигналы на запись и на счипшание,в зависимости от признака обрацения на входе 31 блока 14 через дешийратор 33 подаются либо в блок 3 по выходам 27 и 28 соответственно, ли бо в блок 4 по выходам 23 и 30 соответственно ( фиг. 2|с Для устранения излишних временных затрат при считывании в случае ствия сигнала ошибки одновременно в блоках 10 и 15 сигнал опроса элементов И 18 формируется с Выхода первого разряда регистра 43 и через элементы И 39 и ИЛИ 42 поступает на выход 25, а при наличии сигналов ошибки в обо их блоках 10 и 15 сигнал опроса формируется с выхода второго разряда региЪтра 43 и на выход 25 поступает через элементы И 4П и ИЛИ 42« В обоих случаях по концу сигнала опроса элементом И 41 сформируется сигнал сброса, который через элементы задержки 3 и элемент НЕ 34 подается на выход 26, По этому сигналу происходит сброс регистров 8, 12 и 13 запоминающего У Уфйства. Для случая обнаружения ошибки обоими блоками 10 и 15 в первом такте запускается регистр 43, происходит за пись и считывание инверсного кода, формирование на входах элементов И 18 истинного значения слова. Во втором такте происходит опрос элементов И 18 и выдача на выход 20 считываемого по данному адресу слова. Третий такт . выдачу слова прекращает и через элемент задержки Зб обнуляет регистры 8, 12 и 13s подготавливая запоминающее устройство к следующей операции, Если производится обращение к блоку 4 памяти, то работа устройства происходит аналогично описанному. Таким образом, обеспечивается исправная работа запоминающего устройства при наличии отказов в разных разрядах одноименных ячеек рабочих и резервного блоков памяти при сокращении, по сравнению с прототипом количества оборудования в цепях съема информации с резервного блока памяти и упрО1;4ении реализации блока местного управления о Технико-экономическое преимущество предлагаемого устройства заключается в более высокой по сравнению с прототипом надежности устройства. Формула изобретения 1. Резервированное запоминающее устройство, содержащее регистры числа, коммутаторы, регистр адреса, одни из выходов которого подключены к адресным входам первого и второго основных и резервного блоков памяти, а другой выход соединен с управляющими входами первого и второго коммутаторов, первый блок контроля и сумматор по модулю два, причем выходы ос- .: новных блоков памяти подключены к входам первого и второго коммутаторов, выходы второго коммутатора соединены с информационными входами первого регистра числа, выходы которого соединены с входами первого блока контроля и одними из входов третьего коммутаора, другие входы которого подключены к выходам второго регистра числа, информационные входы которого соединены с выходами сумматора по модулю два, входы которого подключены соответственно к выходам резервного блока памяти и к выходам первого коммутатора, о т ли чающееся тем, что, с целью повышения надежности устройства, в него введены группы элементов И, второй блок контроля, третий регистр числа, блок местного управления и группа элементов ИЛИ,входы которых подключены соответственно к выходу третьего коммутатора и к выходам элементов И первой и второй групп, первые входы которых соединены с одним из выходов блока местного управления, другие выходы которого подключены соответственно к управляю щим входам третьего коммутатора, к .управляющему входу первого регистра числа, к управляющим входам основных блоков памяти, к установочным входам регистров числа и к одним из входов элементов И третьей группы, другие входы которых соединены с выходами элементов ИЛИ группы, информационные входы третьего, регистра числа подклю чены к выходам второго коммутатора, а прямые и инверсные выходы соединены соответственно с вторыми входами элементов И первой группы и с вторым входами элементов И второй группы и информационными входами основных бло ков памяти, третьи входы элементов И первой и второй групп подключены соответственно к выходам первого регис ра числа и к входам второго блока контроля и выходам второго регистра числа, первый}, второй и третий входы блока местного управления .соединены соответственно с выходами первого и. второго блоков контроля и с другим выходом регистра адреса, четвертый и пятый, входы блока местного управления и выходы элементов И третьей груп пы являются соответственно управляющим и тактовыми входами и выходами устройства. 2. Устройство по п. 1,отлйч ,а о щ е е с я тем, что блок местного управления содержит генератор одиночных сигналов, дешифраторы, регистр сдвига, элементы И, элемент ИЛИ элементы НЕ и элементы задержки, причем выходы и тактовый вход регистра сдвига подключены соответственно к пер- вым входам первого, второго и третьего элементов И, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого подключай к второму входу третьего элемента И, Шз1ход которого соединен с входом первого элемента задержки, выход которого подключен к входу .первого элемента НЕ, второй вход первого элемента И соединен с выходом второго элег мента НЕ, вход которого подключен к первому выходу первого дeшифpaтopa второму входу второго элемента И и входу генератора одиночных сигналов, выход которого соединен с первым входом второго дешифратора и входом второго элемента задержки, выход которого подключен к второму входу второго дешифратора, первый и второй входы первого дешифратора, третий вход второго дешифратора, информационный и тактовый входы регистра сдвига являются соответственно входами с первого по пятый блока, выходами с первого по десятый которого являются соответственно второй, третий и первый выходы первого дешифратора, выходы второго элемента НЕ, элемента ИЛИ и I первого элемента НЕ и выходы с первого по четвертый второго дешифратораИсточники информации, . ; принятые во внимание при экспертизе 1. Авторское свидетелвство СССР W , кл. G 11 С 29/00, 1979. 2, Авторское свидетельство СССР № 6 10375, кл. G 11 С 29/00, 1977 (прототип).

й/г./

20

Щ

J/

J

Л

Ь

J

f

MlNi

2

L

Г f . I

2/ fr2J l 25 6

j I

t. .. .1

27 19 29 ff Фи1,1

Авторы

Даты

1982-12-15—Публикация

1981-06-18—Подача