(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРО

1

Изобретение относится к области .запоминающих устройств.

Известное запоминающее устройство содержит регистр адреса, в,ыходы которого через дешифраторы адреса подключены ко входам накопителей, выходы которых подключены к соответствующим регистрам слова, схему равенства кодов, входы которой подключены к выходам регистров слова, а выход подключен к одному входу элемента И, Другой вход которой подключен к. блоку управления, а выход подключен к одному из регистров слова, элемент ИЛИ, группы элементов по количеству накопителей и выходной регистр l .

Недостатком этого запоминающего устройства является то, что при наличии отказов в одноименных запоминающих ячейках накопителей не происходит выдача информации.

Наиболее близким т:ехническим решением к данному изобретению является запоминающее устройство, которое содержит дополнительные регистры слова по количеству накопителей, входы которых подключены к выходам соответствующих основных регистров слова, схемы поразрядной проверки по

В11ГВ

fe I. ;i/ l-ff--f. : f «y l -|i&j|l

количеству накопителей, одни входы которых подключены к выходам соответствующих основных регистров Слова, а другие входы подключены к выходам дополнительных регистров слова,выходы подключены к управляющим входам элементов И групп, информационные входы которых подключены к блоку управления, а выходы подключены к управляющим йхо дам соответствующих регистров основных регистров слова, выходы которых через элемент ИЛИ подключены к выходному регистру 2.

Недостатком этого запоминающего

15 устройства является то, что при наличии ошибок В; одноименных разрядах одноименных запоминающих ячеек не происходит выдача информации, что приводит к снижению его надежности.

20 Целью изобретения является повышение надежности запог инающего устройства за счет записи слова таким образом., чтобы были сохранены правильными все разряды слова, несмотря

25 на сбои в одноименных разрядах одноименных запоминающих ячеек.

Указанная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее регистр адреса, первые и вторые деишфраторы, накопители, основные и дополнительные регистры слова,,схемы сравнения, элементы И и элемент ИЛИ, входной регистр и блок.управления, П15ичем выходы регистра адреса подключены к входам дешифраторов, адресные входы накопителей соединены с выходами соответствующих дешифраторов, первые информационные выходы накопителей соединены с первыми входами соответствующих основных регистров слова, вторые входы которых подключены к выходам соответствующих элементов И, информационные входы которых соединены с .первыми выходами соответствующих схем сравнения, первые вых.оды основных регистров слова подключены к входам соответствующих дополнительных регистров слова и схем сравнения, вторые входы которых подключены к выходам соответствующих дополнительных регистров слова, вторые выходы основных регистров слова подключены к первым информационным входам соответствующих накопителей, третьи выходы основных регистров слова подключены к входам элемента ИЛИ, выход которрго подключен к первому входу входного регистра, второй вход которого подключен к первым информационным входам накопителей, выход - к третьему входу первого основного регистра слова, первые управляющие, входы регистров и управляющие входы накопителей и элементов И подключены к одним из выходов блока управления, введены реверсивный счетчик, схема поразрядного сравнения и дополнительные элементы И и ИЛИ, причем входы схемы поразрядного сравнения подключены к вторым входам схем сравнения, первый выход подключен к вторым управляющим входам входного регистра, первых регистров слова, к первому управляющему входу реверсивного счетчика, второй выход схемы поразрядного сравнения подключен к одному из входов блока управления выход дополнительного элемента И.подключен к третьйй управляющим входам первых регистров слова, к второму управляющему входу реверсивного счетчика, информационный вход которого подключен к второму выходу первого накопителя, выходы реверсивного счетчика подключены к второму входу первого накопителя и входам дополнительного элемента ИЛИ выход которого соединен с первым входом дополнительного элемента И, второй вход которо-го и третий управляющий вход реверсивного счётчиКа подключены к другим выходам блока управления.

Регистры слова и входной регистр могут быть выполнены в виде сдвигающих реверсивных регистров.

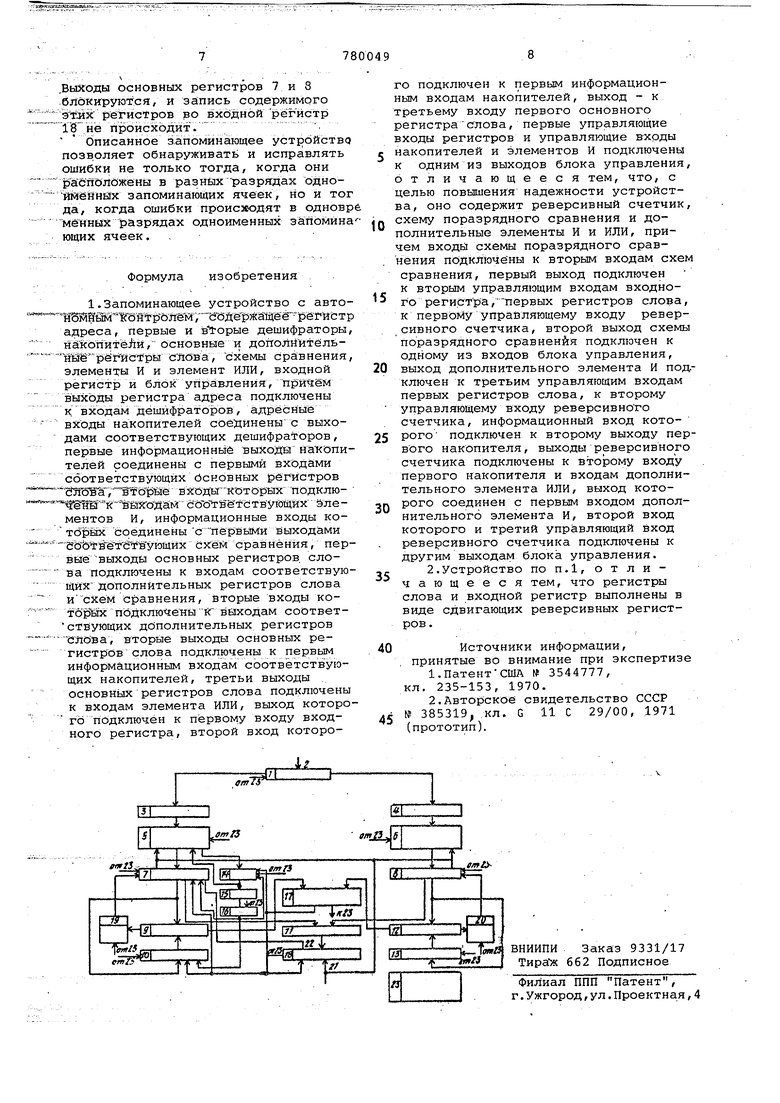

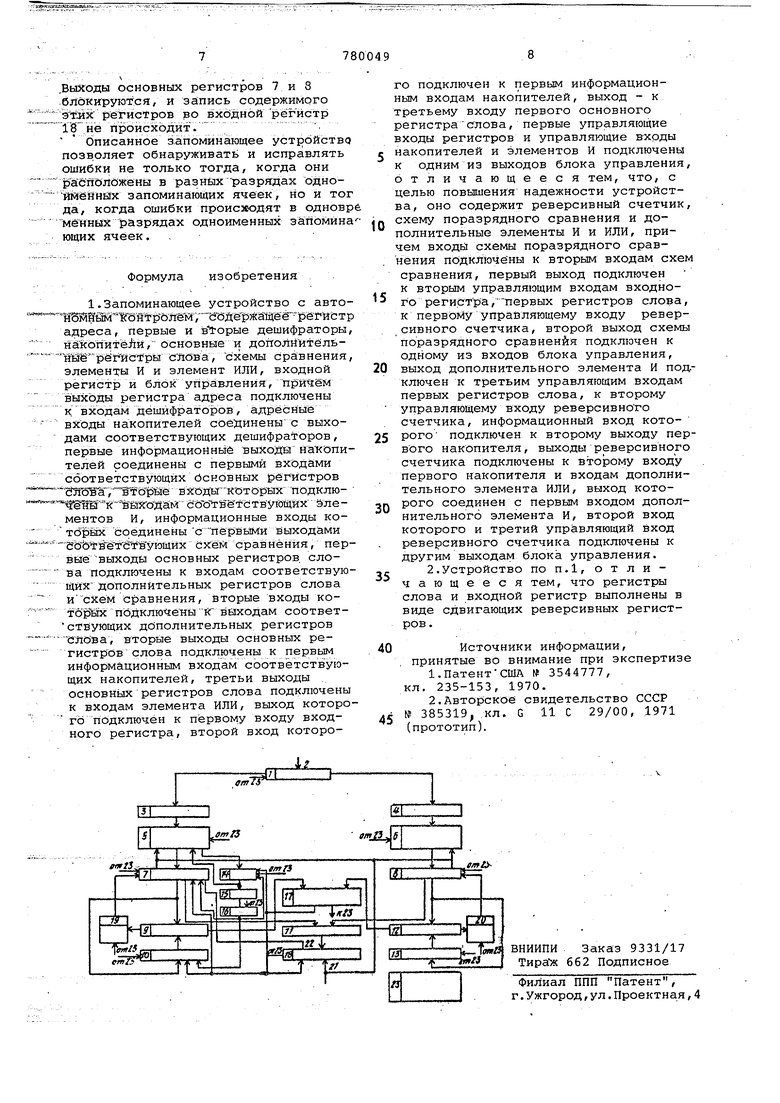

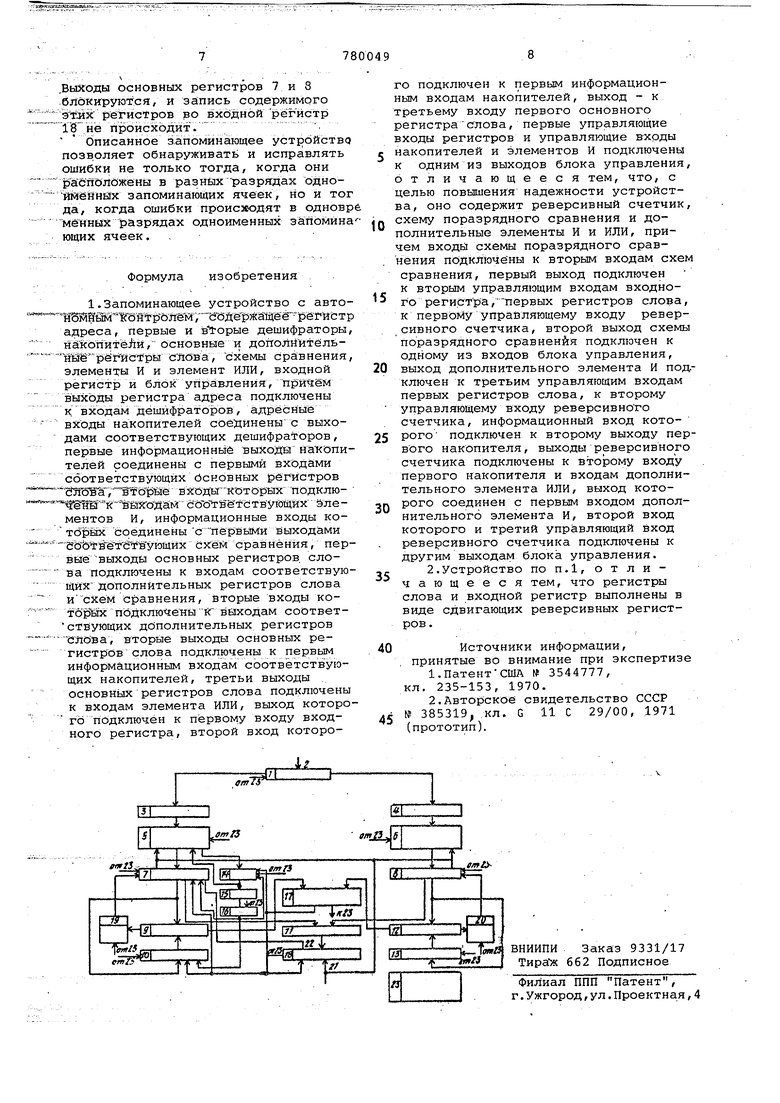

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит регистр 1 адреса, имеющий информационный вход 2, первый 3 и второй 4 дешифраторы адреса, первый 5 и второй 6 накопители, первый 7 и второй 8 основные регистры слова, первую схему 9 сравнения, первый дополнительный регистр 10 слова, элемент ИЛИ 11, вторую схему 12 сравнения, второй дополнительный регистр 13 слова, реверсивный счетчик 14, дополнительные элемент ИЛИ 15 и элемент И 16, схему 17 поразрядного сравнения, входной регистр 18, элементы И 19 и 20.

Регистр 18 имеет вход 21 и выход 22:

Устройство также содержит блок 23 управления. Выходы регистра 1 адреса подключены к входам дешифраторов 3 и 4, адресные входы накопителей 5 и б соединены с выходом соответствующих дешифраторов 3 и 4, а первые информационные выходы соединены с первыми входами соответствующих Основных регистров 7 и 8 слова вторые входы которых подключены к выходам соответствующих элементов И 19 и 20, информационные входы которых соединены с первыми выходами соответствующей схемы 9 или 12 сравнения. Первые выходы основных регистров 7 и 8 слова подключены к первым входам соответствующих дополнительных регистров 10 и 13 слова. Вторые выходы основных регистров 7 и 8 слова подключены к первым информационным входам соответствующих накопителей 5 и б, третьи выходы основйых регистров 7 и 8 слова подключены к входам элемента ИЛИ 11, выход которого подсоединен к первому входу входного регистра 18, второй вход которого подключен к первым информационным входам накопителей 5 и б, выход - к третьему входу первого основного регистра 7 слова, первые управляющие входы регистров 7,8,10, 13 и управляющие входы накопителей . 5 и б и элементов И 19 и 20 подклю-, чены к одним из выходов блока 23 управления. Входы схемы 17 поразрядного сравнения подключены jc вторым выходам схем 9 и 12 сравнения, первый выход подключен к вторым управляющим входам входного регистра 18, первых основного 7 и дополнительного 10 регистров слова к первому управляющему входу реверсивного счетчика 14, второй выход подключен к одному из входов блока 23 управления выход дополнительного элемента 16 подключен к третьим управляющим входам первых основного 7 и дополнительного 10 регистров слова к второму управляющему входу реверсивного счетчика 14, информационный вход которого подключен к второму выходу первог

накопителя 5, выходы реверсивного счетчика 14 подключены к второму входу первого накопителя 5 и входам дополнительного элемента ИЛИ 15, выход которого соединен с первым входом дополнительного элемента И 16 второй вход которого и третий управляющий вход реверсивного счетчика 14 подключены к другим выходам блока 23 управления.

Для нормальной работы установки необходимо, чтобы выполнялось усло.вие;

К--,, .

где К - число дополнительных разрядов ; п - число разрядов в слове.

Работа запоминающего устройства в режиме записи.

На регистр 1 адреса по бходу 2 поступает адрес ячейки, в которую необходимо записать слово. Одновременно происходит установка счетчика 14 в нулевое состояние и по входу 21 слово поступает во входной регистр 18, в накопители 5 и 6 с последующим считыванием соответственно в регистры 7,8,10 и 13 слова. В те -же ячейки накопителей 5 и 6 происходит запись .обратных кодов содержимого регистров 7 и 8 слова с последующим считыванием в те же регистры. Коды с основного регистра 7 слова и дополнительного регистра 10 слова поступают на бхему 9 сравнения. Коды сосновного регистра 8 слова и дополнительного регистра 13 слова .поступают на схему 12 сравнения. При совпадении прямых и обратных кодов одноименных разрядов, схемы .9 и 12 сравнения выдают сигнал 1 только в этих разрядах.сформированного данной схемой кода. Коды со схем 9 и 12 сравнения поступают на схему 19 поразрядного сравнения, которая вырабатывает сигнал 1, если есть совпадение единиц в одноименных .раз-рядах поданных на нее кодов.

Если этот сигнгип равен О, то происходит запись слов с основных регистров 7 и 8 слов соответственно в накопители 5 и 6. Если сигнал, вырабатываемый схемой 17 поразрядного сравнения,-, то он поступает на вход основного регистра 7 слова, дополнительного регистра 10 слова, регистра 18(содержимое этих регистров сдвигается на один разряд вправо), на первый вход счетчика 14. При подаче единичного сигнала на первый вход счетчика 14 его содержимое увеличивается на единицу, а при подаче единичного сигнала на второй ВХОД - уменьшается на единицу. , Сигнал 1 поступает на второй вход счетчика 14 и устанавливает его в состояние 00... 01. После этого сдвинутые на одну позицию вправо код

с основного регистра 7 слова и дополнительного регистра 10 слова поступают на схему 9 сравнения, а коды с основного регистра 8 слова и дополнительного регистра 13 слова поступают на схему 12 сравнения. Коды со схем 9 и 12 сравнения поступают на схему 17 поразрядного сравнения и т.д.

Этот цикл повторяется до тех пор, пока схема 17 поразрядного сравнения не выработает сигнал О, после чег

0 с выхода 22 входного регистра 18 происходит выдача обратного кода его содержимого и запись его в основной регистр 7 слова. Содержимое основного регистра 8 слова записывается в

5 накопитель б, а содержимое основного регистра 7 слова и счетчика 14.записывается внакопитель5. Таким образом в накопителе б будет записан обратный код слова, в накопителе 5

0 будет записан обратный код, сдвинутый вправо на некоторое число разрядов, а число сдвигов записано в счетчике 14.

Работа запоминающего устройства в режиме -считывания.

5

На регистр 1 адреса по входу 2 поступает адрес ячейки, к которой необходимо обратиться. Из накопителей 5 и б происходит выдачакодов соответственно в основной регистр 7

0 слова, дополнительный регистр 13 слова. В те же ячейки накопителей происходит запись обратных кодов содержимого соответствующей основных ре.гист| ов 7 и 8 слова с последующим

5 считыванием в эти же регистры.

Если содержимое счетчика 14 не равно нулю, то на выходе элемента ИЛИ 15 появляется единичный сигнал, который поступает на вход элемента И 16, а на другой вход элемента И 16

0 поступает сигнал от блока 23 управления, который открывает элемент И 16, и сигнал 1 вьщается на вход основного регистра 7 слова, на вход дополнительного регистра 10 слова

5 (содержимое этих регистров сдвигается на один разряд влево), на второй вход счетчика 14 и его содержимое уменьшается на единицу. Этот цикл повторяется до тех пор, пока

0 содержимое счетчика 14 не станет равно нулю, после чего кода с основного регистра 7 слова и дополнительного регистра 10 слова поступят на Схему 9 сравнения, а .коды с основ5ного регистра 8 слова и дополнительного регистра 13 слова поступают аа схему 12 сравнения. При несовпадении прямых и обратных кодов одноименных разрядов схем 9 и 12 сравнения через соответствующие элементы

0 И 19 и 20 выдают сигналы, разрешающие выдачу кодов соответственно с основных регистров 7 и 8 через элемент ИЛИ 11 на вход входного регистра 18 только для этих разрядов.

5

.Выходы основных регистров 7 и 8 блокигруются, и запись содержимого ЭТЙХ рётгисТров во входной регистр

1 не п эойсходит.

Описанное запоминающее устройства позв.оляет обнаруживать и исправлять ошибки не только тогда, когда они расположены в разНйх разрядах одно ййёйнах запоминающих ячеек, но и тог

да, когда ошибки происзводят в одноврё. мённых разрядах одноименных запомйна ющих ячеек. ,

Формула изобретения

1.Запоминающее устройство с автоШЙйШ 1с5н Е0-ШТй,ббдержЩёе фёГйстр адреса, первые и вторые дешифраторы, ййкопйтёЛй, основные и дополййтёль нтаё рёгистры , схемы сравнения, элементы И и элемент ИЛИ, входной регистр и блок управления, причём выходы регистра адреса подключены к входам дешифраторов , адрёсньаё входы накопителей соединеныс выходами соответствующих дешифраторов, первые информационнее выхода Накопителей соединены с первыми входами соответствующих Основных регистров e5 c5Sa7 BTfОрйё ВХОДЫКОторЫХ подклю Гё1Ге-Г-&аХ0-аам--сОЪ йётствУ адйх--элементов И, информационные входы коtdpEix соединены с первьгМй выходами сЬдт;вётс вую1Цйх схём сравнёййя, первые выходы основных регистров, слова подключены к входам соответствующих дополнительных регистров слова и схем сравнения, вторые входы котОраХ пОДклю 1ёна iT вйходам соответствующих дополнительных регистров СлОва, вторые выходы основных регИстрОвслова подключены к первЕдм информационным входам соответствующих накопителей, третьи выходы ocHOBHbiX регистров слова подключены к входам элемента ИЛИ, выход которого подключен к первому входу входного регистра, второй вход которого подключен к первым информационным входам накопителей, выход - к третьему входу первого основного регистраслова, первые управляющие входы регистров и управляющие входы накопителей и элементов И подключены к одним из выходов блока управления, отличающееся тем, что, с целью повышения надежности устройства, оно содержит реверсивный счетчик, схему поразрядного сравнения и дополнительные элементы И и ИЛИ, причем входа схемы поразрядного сравнения подключены к вторым входам схем сравнения, первый выход подключен к вторым управляющим входам входного регистра, первых регистров слова, к первому упраззляющему входу реверсивного счетчика, второй выход схемы поразрядного сравненйя подключен к одйому из входов блока управления, выход дополнительного элемента И подключен к третьим управляющим входам первых регистров слова, к второму управляющему входу реверсивного счетчика, информационный вход которого подключен к второму выходу первого накопителя, выхода реверсивного счетчика подключена к второму входу Первого накопителя и входам дополнительного элемента ИЛИ, выход которого соединен с первым входом дополнительного элемента И, второй вход которого и третий управляющий вход реверсивного счетчика подключены к другим выходам блока управления.

2.Устройство по п.1,отличающее с я тем, что регистры слова и входной регистр выполнены в виде сдвигающих реверсивных регистров .

Источники информации, принятые во внимание при экспертизе

1.ПатентСШЛ № 3544777, кл. 235-153, 1970.

2.Авторское свидетельство СССР № 385319, кл. G 11 С 29/00, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Запоминающее устройство | 1977 |

|

SU658602A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1075312A1 |

| Постоянное запоминающее устройство с самоконтролем | 1985 |

|

SU1285538A1 |

| Запоминающее устройство | 1972 |

|

SU470866A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство с обнаружением ошибок | 1985 |

|

SU1277215A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

Авторы

Даты

1980-11-15—Публикация

1978-07-18—Подача