(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| Устройство для поиска информации на ленточном носителе | 1984 |

|

SU1208564A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

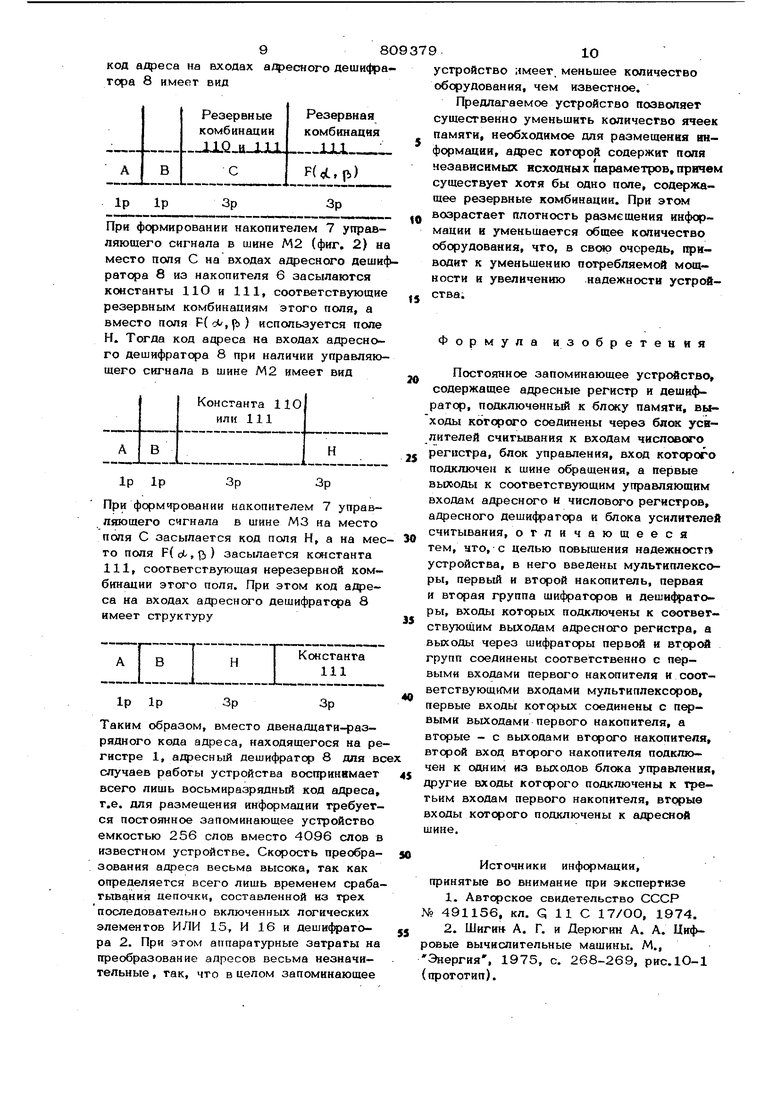

Изобретение относится к вычислитель- ной технике и может бьггь гфименено в постоянных запоминающих устройствах контроллеров, устройств сбора и обработки инфс мации и специализированных ЭВМ в случаях, когда адрес определяется совокупностью нескольких параметров. Известно постоянное зaпo инaioшee устройство, позволяющее уменьшать количество адресуемых sneeK памяти за счет введения блока моди()шкааии адреса, ко- торый включен между усилителями считывания и регистром числа. В таком запоминающем устройстве требуемая выходная информация может быть получена на основе выходной информации аз накопителя и . .информации о коде адреса путем моакфикации определенных разрядов в соответствии с признаками модвфикацнн, чта фактически равносильно увеличенкю информационной емкости запоминающего уст- ;рсЛства l . Такое устройство формирует данные на своем выходе, но не формирует адресов с учетом рабочих и резервных комбинаций каждого поля кода aqpeca н тем самым не позволяет за счет этого умевьщить объем адресуемой памяти. Наиболее близким техническим решением .по предлагаемому является aocToiraное запоминающее устрсЛство, содержащее регистр адреса, адресный дешифратор, блок памяти, усилители считывания, числовой регистр слова и блок управления. Данное устройство имеет большую емкость памяти, определяемую как Q 2. N ti , где - копичество попя ащреса, соответствующего -1 -ому иохошкму параметру К - количество воходаых параметр. При этом блок памяти пустые здны общей емкостью (3L, ячё -памятв, и равно VEP. -1( где Р. - количество неиспользуемых (резервных) комбинаций поля i -го исходного параметра, а также 0. резервны ячеек памяти с повторягощимися фрагментами информации равное. WN-VA. .-)i где m - количество функций от исходных параметров, входящих в состав кода адре са, р - количество совпадающих значений ju функции разрядностью li.j f2 К недостаткам относится также низкая плотность размещения инффмации в блоке памяти из-за наличия пустых зон и повторяющихся фрагментов информации. Из-за указанных недостатков устройство низкую -надежность. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее адресные регистр и дешифратор, подключенный к блоку памяти, выходы которого соединены через блок усилителей считывания :к входам числового регистра, блок управления, вход коTqDoro подключен к шине обращения, а первые выходы к соответствующим управляющим входам адресного и числового регистров, адресного деши4ратора и блока усилителей считывания, введены муль типлексоры, первый и второй накопитель, первая и вторая группа щифраторов и дешифраторы, входы подключены к соответствующим выходам адресного регистра, а выход через шифраторы первой и второй групп соединены соответственно с первыми входами первого накопителя и соответствующими входами мул типлекссфов, первые входы которых соединены с первыми выходами первого накопителя, а вторые - с выходами второго накопителя, второй выход второго накопителя подключен к одним из выходов блока управления, другие входы которог подключены к третьим входам первого н копителя, вторые входы которого подклю чены к адресной шине. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - то же, с дополнени ми. Устройство содержит адресный регист 1, дешифраторы 2, первую и вторую гру пы щифраторов 3 и, 4, мультиплексоры 5, первый и второй накопители 6 и 7, адресный дешифратор 8, блок 9 памяти, усилители 10 считывания, числовой реистр 11, блок 12 управления, шину 13 обращения, адресную шину 14. дресный регистр 1 имеет разрядность -.-л и содержит К полей, причем i -ое поле соответствует i -ому исодному .параметру и имеет количество разрядов, равное и . Дешифратор 2 подключен ко вторым выходам адресного регистра 1, которые принадлежат полю, обладающему хотя бы одной резервной комбинацией. Соответствующий дешифратор 2 пошслючен также ко вторым выходам регистра 1 двух или более полей, значение функции от которых используется для формирования адреса. Кроме того, дешифратор 2 подключен ко вторым выходам регистра 1 того поля, которое хотя и не имеет ни одной резервной комбинации, но рабочие коды которого перекодируют для оптимального размещения информации в блоке 9 памяти. Следует отметить, что применение дешифратора 2 во всех случаях позволяет перекодировать коды соответствующих полей, а также коды значений функции от соответствующих исходньк параметров. Первые вьрсоды регистра 1 полей, не обладающих резервными комбинациями, а также не подлежащие преобразованию или перекодированию, подключены непосредственно к соответствующим первым входам адресного дешифратора 8. Выходы каждого из дешифраторов 2 подключены к входам соответствующих шифраторов 3 и 4 первой и второй групп. Выходы всех шифраторов 3 подключены к соответствующим первым входам накопителя 7, BTqjbie входы которого соединены с адресными шинами 14. Выходы всех шифраторов 4 подключены к соответствующим первым информационным входам мультиплексоров 5, управляющие входы соединены с соответствующими первыми выходами накопителя, втсрые выходы которого подключены к первым входам накопителя 6, Вторые входы накопителя 6 соединены со втqэымй выходами блока 12 управления, третьи выходы которого подключены к третьим входам накопителя 7. Вход блока i 12 управления соединен с шиной 13 обращения. Выходы накопителя 6 подключены к соответствующим вторым информационным входам мультиплексора 5, выходы которых подключены к соответствующим вторым входам адресного дешифратора 8. Выходы адресного дешифратора 8 соединены с адресными входами блока 9 памяти, выходные шины которого подключены к соогветствующим входам усилителей 1О считывания, выходы которых подключены к соответствующим входам числового регистра 11. Первые выходы блока 12 утфавления подключены к соответствующим управляю щим входам (на фиг. 1 не показано) адресного регистра 1, числового регистра 11, адресного дешифратора 8, усилителей Ю считьшания. Шифратор 4 аредаазначен для выделения и фиксации используемых (рабочих) состояний поля кода адреса соответствующего исходного параметра, количество значений (состояний) котсрсн о меньше максимального возможного, а также для перекодирования поля кода адреса с целью оптимального размещения информации в блоке памяти 9. По своему принципу построения каждый блок 4 представ ляет собой усеченную схему классического шифратора и может быть реализсшана например, на интегральных лся ических элементах серии 155, диодных или транзисторных элементах. В качестве шифратора могут быть применены также интегральные матрицы небольшой размерности, применяемые для построения узла памяти постоянных запоминающих устройств. Шифратор 3 по своему принципу построения аналогичен шифратору 4 и применяется для вьщеления и фиксации неиспользуемых (резервных) состояний поля кода адреса соответствующего исходного параметра. При этом количество блоков 3 равно количеству полей кода адреса, содержащих неиспользуемые сост яния. Накопитель 7 на основании кода адресов, поступающих по адресным шинам 14, и адреса, соответствующего заранее известным резервным комбинациям полей регистра адреса, поступающего на его первые входы, выдает на свои первые выходы коды управляющих слов, которые для каждого мультиплексора 5 в каждом конкретном случае выбирают направление коммутации, т.е. выходы какого шифратора 4 подключить на соответствующие вхо ды адресного дешифратора 8. Кроме того накопитель 7 выдает на свои вторые выходы управляющие сигналы, поступающие на первые входы накопителя 6 для выбора адреса константы, соответствующей коду адреса на шинах 14 и кодам резервных комбинаций. Накопитель 6 хранит (или формирует) и выдает на свои выходы коды адреса константы, необходимые для преобразования кода аореса с целью эффективного использования свобоаных зон в блоке 9 памяти. Он может быть выполнен на интегральных логических элементах, например, серии 155 или в виде матрицы постояннсго запоминающего устройства, например, с диодными элементами связи, в которой хранятся константы. В этом случае накопитель 6 выдает константы в соответствии с кодом адреса, поступающим с накопителя 7 на его первые входы, и сигналом обращения, поступающим на второй вход с блока 12 управления. Работа устройства происходит следующим образом. При обращении к устройству на вход 12 управления поступает сигнал обращения. Блок 12 управления выдает на свои выходы определенную последовательность импульсов, которые управляют работой всех узлов и блоков устройства, а также сигнал вызова константы, поступающий на второй вход накопителя 6. Одновременно с сигналом обращения но шинам 14 поступает код адреса, который указывает на условия преобразования адреса. Код адреса на регистр 1 заносят заранее или одновременно с сигналом обращения 13. Коды полей регистра 1, котсрые не имеют резервных комбинаций, а также подлежат преобразованию и перекодированию (например, поля А и В на фиг. 1), поступают непосредственно на соответствующие входы адресного дешифратора 8, Коды остальных полей регистра 1 поступают на входы соответствующих дешифраторов 2, где осуществляется их дешифра- . ция. При этом, если для формирования адреса испбльзуют значение функции от двух или более исходных параметров (например, F (eL,fi ), то коды полей соответствующих этим параметрам ( ct и fi ),поступают на соответствующие входы одного дешифратора 2, во всех остальных случаях на входы дешифратора 2 посту- пает код только одного поля соответствующего исходнея о параметра. Сигналы с выходов дешифраторов 2 поступают на входы шифратора 4 н входы шифратора 3. Если код поля адреса, выставленного на регистре 1, является используемым (рабочим), то соответствующий блок 4 шифратора срабатывает и на ее выходе сфор- мировьшается соответствующий код. При этом соответствующий блок 3 шифратора вьшает на вькоды нулевой код, который поступает на соответствующие входы на-, копителя 7.

Еслн код поля адреса, высгавленнбго на регистре 1, является неиспользуемым (резервнымJ, то срабатывает соогветствующнй блсж 3,а на выходах соответствующего блока 4 появляется нулевой код. Таким образом, на первых входах накопителя 7 содержится полная информация о наличии резервных состояний для каждого поля кода адреса, выставленного на регистр 1. По этой информации, а также по коду адреса, выставленному на шннах 14 адреса, накопитель 7 выдает на свои первые вьиоды коды управляющих слов, поступающие на соответствующие входы мультиплексоров 5, и код адреса константы (если в соответствии с кодом условий вызов константы необходим), поступающий на цервые входы накопителя 6. При наличии этого кода адреса, а также сигнала вызова константы, поступающего с блока 12 управления на вто.рой вход накопителя 6, накопитель б выдает код константы, который поступает на соответствующие информационные входы мультиплексоров 5. Таким образом на информационных входах каждого из мультиплексоров 5 присутствуют коды рабочих состояний и нулевые коды (резервные состояния), а также код вызванной константы.

Коды управляющих слов, поступающие на соответствующие входы мультиплексоров 5, коммутируют на выход каждого мультиплексора 5 один из кодов, присутствующих на его входах от блоков 4 и нкопителя 6. При этом возможна как просранственная перестановка полей внутри кода адреса, так и заполнение поля кода адреса кодом константы, вызванной из накопителя 6. Преобразованный код каждот о поля кода адреса, а также код константы поступает на соответствующие вторые входы адресаного дешифратора 8, который на одном из своих выходов вырабатывает сигнал, возбуждающий один и адресных входов блока 9 памяти. При этом на выходных шинах блока 9 памяти появляются сигналы кода слова, которые через усилители Ю считывания передаются на соответствующие входы числового регистра 11, где запоминаются до следующего обращения к устройству.

Таким образом, данное устройство Позволяет размещать информацию в блоке 9 памяти с максимальной плотностью за счет эффективного использования пустых ЗОИ, а также исключения повторяющихся фрагментов информации в блоке 9 памяти, что эквивалентно уменьшению общего количества ячеек памяти. При этом скорость преобразования адреса высока, так как она определяется только задержками прохождения кода адреса через обыные логические элементы И и ИЛИ, входящие в состав дешифратора 2, шифраторов 3 и 4, мультиплексора 5, Аппаратурные затраты на преобразование адресов незначительны, так как деши(}раторы 2 применяют на небольшое количество выходов (не более 16), а количество таких дешифраторов и соответствующих :им щифраторов и мультиплексоров также невелико вследствие того, что не все поля кода адреса., как правило, имеют резервные комбинации и не все поля кода адреса подлежат преобразованию и перекодированию.

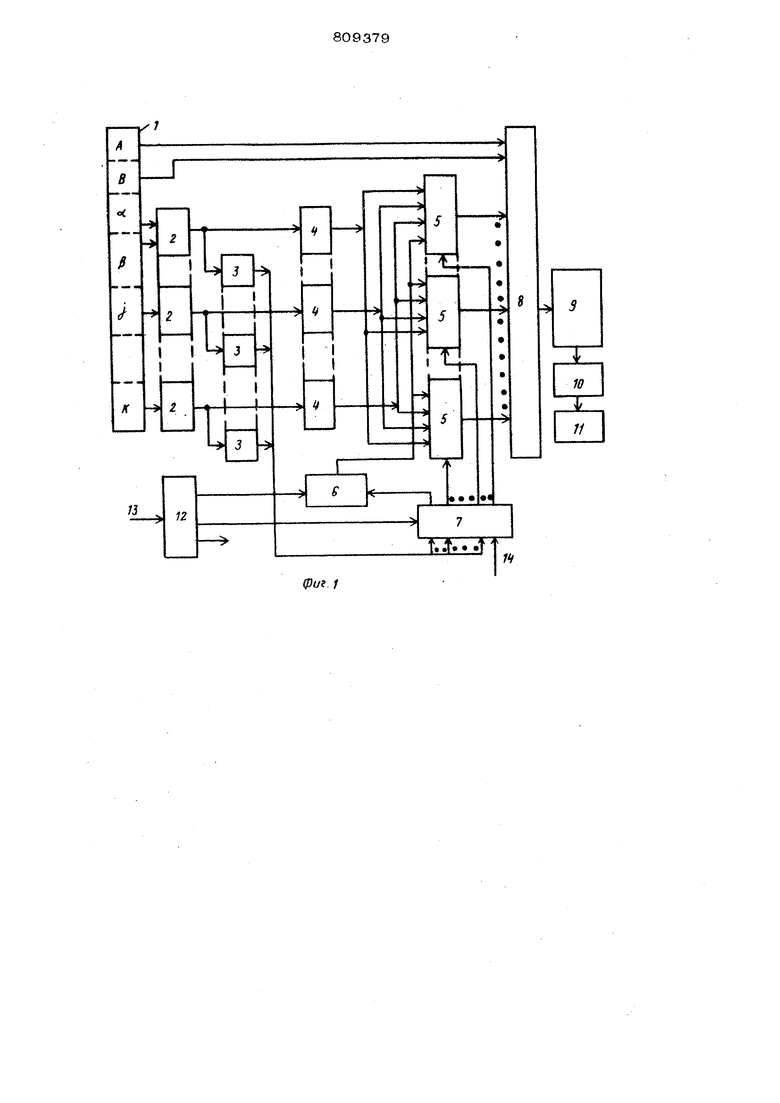

На фиг, 2 приняты те же обозначения что и на фиг. 1, но дополнительно обозначены: элементы 15 ИЛИ, элементы 16 И, щины управляющих сигналов М 1, М 2, М 3.

На фиг. 2 адресньй регистр 1 хранит двенадаатиразрядный код адреса, содержащий четыре поля А, В, С, Н независимых параметров и два поля , р , значения функции от которых F(,в) используются для формирования регулирующего кода адреса. При этом А и В - одноразрядные поля, С и Н - трехразрядные, а о1 , fi - двухразрядные. Выходы регистра адреса полей А и В подключены непосредственно к соответствующим входам адресного деши4чзатора 8, выходы полей С и Н - ко входам дешифраторов 2, имеющих восемь вькодов каждый: а выходы полей параметров оС и р подключены к соответствующим входам дешифратора 2, имеющего шестнадцать выходов, причем каждый из шестнадцати вь1ходов подключен ко входам соответствующего шифратора 4 так, что на выходе этой схемы реализуется функция F( Ajf) ). Так как для различных значений о, и |) значени F( |Ь ) повторяются, то для представлен этой функции использовано всего три разряда вместо четырех на входах дешифратора 2. Заведомо известно, что поле параметра С имеет две неиспользуемые (резервные) комбинации, НО, 111. функция F( , PI )-одну, например, 111.

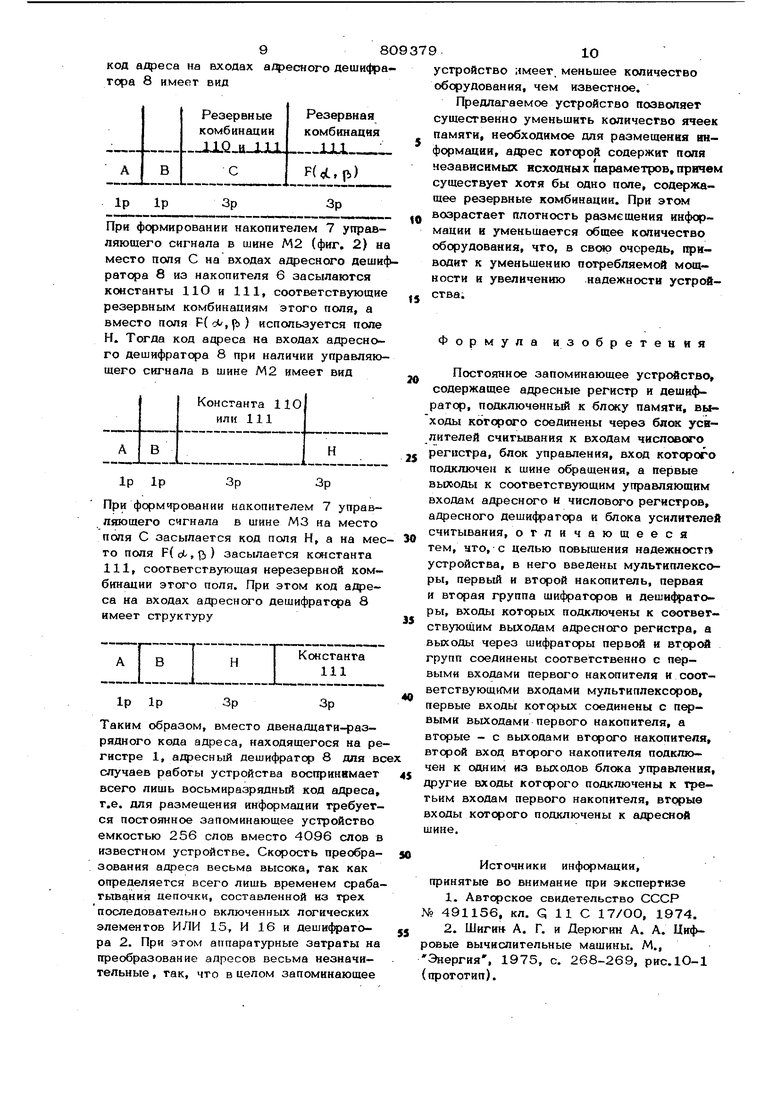

Для того, чтобы исключить свободные зоны в блоке 9 памяти из-за наличия имеющихся резервных комбинаций, преобразование адресов выполняют так, что при наличии в шине Ml управляющего сигнала, вьфабатываемого накопителем 7 код адреса на входах адресного дешифра тора 8 иМОЙт вид При формировании накопителем 7 управляющего сигнала в шине М2 (фиг, 2) н место поля С на входах адресного деши ратора 8 из накопителя б засылаются константы НО и 111, соответствующие резервным комбинациям этого поля, а вместо поля F( сА/, р) ) используется поле Н. Тогда код адреса на входах адресного дешифрат{ра 8 при наличии управляющего сигнала в шине М2 имеет вид Константа НО или 111 1Р 1Р При фсрмчровании накопителем 7 управляющего сигнала в шине МЗ на место поля С засылается код поля Н, а на мес то поля Ffob,) засылается константа 111, соответствующая нерезервной комбинации этого поля. При этом код адре са на входах адресного дешифратора 8 имеет структуру :Е I Константа 1iii. 1р 1р Таким образом, вместо двенадцати-разрядного кода адреса, находящегося на ре гистре 1, адресный дешифратор 8 для в случаев работы устройства воспринимает всего лишь восьмиразр$шный код адреса, т.е. для размещения информации требуется постоянное запоминающее устройство емкостью 256 слов вместо 4О96 слов в известном устройстве. Скорость преобразования адреса весьма высока, так как определяется всего лишь временем сраба тывания цепочки, составленной из трех последовательно включенных логических элементов ИЛИ 15, И 16 и дешифратора 2. При этом аппаратурные затраты на преобразование адресов весьма незначительные , так, что в целом запоминающее устройство имеет, меньшее количество оборудования, чем известное. Предлагаемое устройство позволяет существенно уменьшить количество ячеек памяти, необходимое для размещения информации, а;фес которой содержит поля независимых исходных параметров, причем существует хотя бы одно поле, содержащее резервные комбинации. При этом возрастает плотность размещения информации и уменьшается общее количество оборудования, что, в свою очередь, приводит к уменьшению потребляемой мощности и увеличению надежности устройства;Формула изобретения Постоянное запоминающее устройство, содержащее адресные регистр и дешифратор, подключенный к блоку памяти, выходы которого соединены через блок усилителей считывания к входам числового регистра, блок управления, вход которого подключен к шине обращения, а первые выходы к соответствующим управляющим входам адресного и числового регистров, адресного дешифратора и блока усилителей считывания, отличающееся тем, НТО, с целью повышения надежностг устройства, в него введены мультиплексоры, первый и второй накопитель, первая и вторая группа шифраторов и деши4 аторы, входы которых подключены к соответствующим выходам адресного регистра, а выходы через шифраторы первой и второй групп соединены соответственно с первыми входами первого накопителя и соответствующими входами мультиплексоров, первые входы которых соединены с первыми выходами первого накопителя, а втсчэые - с выходами второго накопителя, второй вход второго накопителя подключен к одним из выходов блсжа управления, другие входы которого подключены к третьим входам первого накопителя, вторые входы которого подключены к адресной шине. Источники инфсрмации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 491156, кл. Q 11 С 17/ОО, 1974. 2.Шигин А. Г. и Дерюгин А. А. Ци4 овые вычислительные машины. М., Энергия, 1975, с. 268-269, рис.10-1 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-01-29—Подача